г

t « 1

«гг

,i - If

00

00

Oi

25

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1300569A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых ПЗУ с многоразрядной организацией. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что устройство содержит элемент ИЛИ 15, блок переадресации 17, группу элементов ИЛИ 18, дешифратор неисправных разрядов на элементах И 19 с соответствующими связями. Строка резервного накопителя 5 разбита на несколько частей, каждая из которых соответствует одному разряду устройства. Указанное соответствие устанавливается блоком переадресации 17. В результате одна резервная строка может занять несколько дефектных элементов памяти в разных строках основного накопителя 1. 2 нл. (Л

Отгз

Изобретение относится к вычислительной технике и может быть исполь- зонано в полупроводниковых ПЗУ с многоразрядной организацией.

Целью изобретения является упрощение устройства.

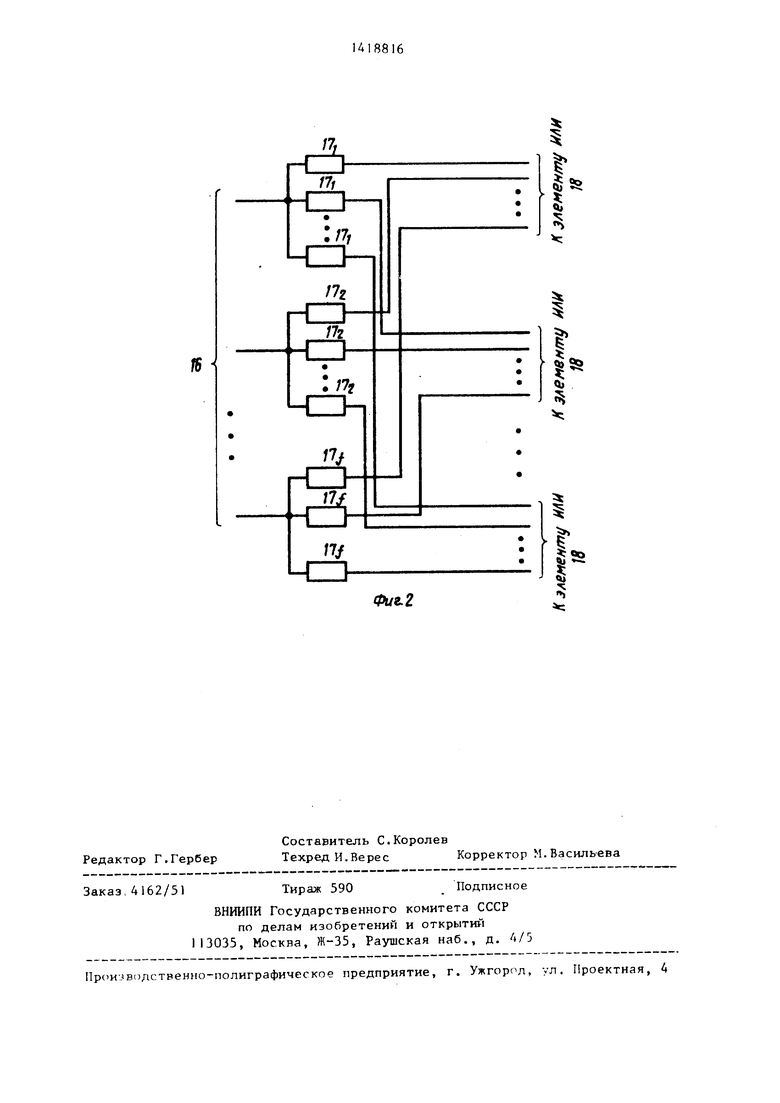

На фиг.1 представлена структурная схема ПЗУ; на фиг.2 - структурная схема блока переадресации.

ПЗУ содержит основной накопитель 1 со словарными 2 и разрядными 3 шинами и тактовыми входами 4, резерв- ньш накопитель 5, со словарной шиной 6 и разрядными шинами 7, резервный усилитель 8 считывания, информапяон- ные входы 9 резервного накопителя 5, основные усилители 10 считывания с адресными входами 11, дешифратор 12 разрядов, блоки 13 сравнения, элементы И 14, элемент ИЛИ 15, выходы 16 элементов И 14, блок 17 переадресации, группу элементов ИЛИ 18, дешифратор неисправных разрядов, выполненных на элементах И 19, выходы 20 дешифратора неисправных разрядов, мультиплексоры 21 с первыми и вторыми информационными входами 22 и 23, адресные входы 24 первой группы устройства, дешифратор 25 слов, адресные входы 26 второй группы устройства, выходы 27 устройства.

Блок 17 переадресации (фиг.2) состоит из f групп 17, 17.,...,17 программируемых элементов, которые могут представлять собой транзисторные ключи, один из выводов которых через пережигаемую перемычку соединен с соответствующими элементами устройства (необходимые для пережигания перемычек цеш элементы не показаны). Количество групп программируемых элементов определяется разрядностью накогштеля, т.е. числом одновременно опрашиваемых элементов памяти. Фактически, в определенной группе элементов 17 должен храниться двоичный адрес чисел от 1 до f. Следует подчеркнуть, что здесь рассматривается, как отмечалось, случай, когда дефекты появляются в отдельных (в любой строке может быть неисправной одна из f частей) группах элементов памяти. При появлении единичного сигнала на одном из входов 16 программируемых элементов 17 на выходах элементов соответствующей группы будут логические сигналы, соответствукщие двоичному представ0

5

0

5

0

5

0

5

0

5

лению числа, которое было запрограммировано .

Блоки 13 сравнения также состоят из аналогичных элементов и предназначены для хранения адреса дефектной строки.

Резервный накопитель 5 может представлять собой как отдельную строку элементов постоянной, так и оперативной памяти. Во втором случае занесение в накопитель 5 необходимой информации может осуществляться и в процессе работы устройства (необходимый для этого управляющий сигнал не показан). Однако возобновление состояния ячеек этого накогштеля должно осуществляться сразу после включения устройства через информационные входы 9. При этом можно устранить не только дефекты производства элементов памяти (кристалла) , но и отказы, появляющиеся в процессе эксплуатации устройства. Предполагается, что в накопителе 3 дефекты не появляются. Единичный сигнал на выходе 20 элемента И 19 соответствует случаю, когда опрашиваемая часть строки является дефектной и считывание соответствующего символа должно осуществляться не из накопителя 1, а из аналогичной части строки (точный адрес элемента задается сигналами на шинах 11) накопителя 5.

Дефектные элементы памяти основного накопителя 1 обнаруживаются в процессе функционального контроля устройства (кристалла памяти). При этом первым может быть обнаружен дефект (или несколько дефектов) в одной из частей строки. Адрес этой строки программируется в первом из блоков 13, а двоичный номер - в соответствующей группе программируемых элементов 17. Соответствующие адреса обнаруженных в последующем дефектных элементов идентифицируются с состоянием следующих блоков 13 и групп элементов в блоке 17. При обнаружении дефектов часть строки с дефектными элемента П1 заменяется со- ответствуквдей частью строки накопителя 5, т.е. в эту часть строки 5 заносится информация, которая должна храниться в строке накопителя 1. Ясно, что при использовании только одной резервной строки допускается появление не более С лиого дефекта в

1А1В816

строке в каждом из поднакопителей в

накопителе 1. По схожему принципу можно использовать сколько угодно резервных строк.

Устройство работает следующим образом.

Адрес опрашиваемой для чтения ячейки накопителя 1 задается адресом 26 столбца и адресом 24 строки накопителя 1. Если в опрашиваемой строке накопителя 1 нет ни одного неисправного элемента (по крайней мере, ранее обнаруженного), то ни на одном из выходов элементов И 14 не будет единичного сигнала, которого не будет и на словарной шине 6 строки накопителя 5, а также ни на одном из выходов 20 элементов и 19. Вместе с тем, единичные сигналы ус- тановятся на одной из словарных шин 2 на соответствующих управлянлцих шинах 11 ( разрядных шинах 3 накопителя усилителей 10 считывания (а также на соответствующих шинах усилите- лей 8 считывания). В соответствии с этим на выходах 22 усилителей 10 считывания установятся считанные информационные символы, которые по нулевому сигналу 20 через мультиплексоры 21 попадут на информационные выходы устройства.

Если же при обращении к строке накопителя 1 в одной из ее частей ранее были обнаружены неисправные элементы памяти, то наряду с выборкой основной ячейки в накопителе 1 происходит обращение и к строке накопителя 5. Последнее обеспечивается тем, что в одном из блоков 13 происходит совпадение адреса 24 с запрограммированным в этом блоке адресом дефектной строки, в результате чего на выходе соответствующего элемента И 14 будет единичный сигнал, который че- рез элемент ИЛИ 15 разрешит обращение к строке накопителя 5. Параплель но с этим единичный сигнал с выхода элемента И 14 поступит на вход соот- ветствующе группы программируеьых элементов блока 17, где запрограммирован двоичный номер части строки с дефектами. Этот двоичный номер установится и на выходах элементов ИЛИ 18, а также на выходе 20 одного из элементов И 19. В соответствии с этим на управляющем входе определенного мультиплексора 21 будет единичный сигнал, который пропустит на вы

5 0 5 О

0 Q g

5

ход этого мультиплексора бит информации, считанный из накопителя 5, остальные биты искомого слова считываются из строки накопителя 1, поскольку на входах 20 остальных мультиплексоров 2 - нулевые уровни. Формула изобретения Постоянное запоминающее устройство, содержащее основной и резервный накопители, основной и резервный усилители считывания, дешифратор слов, дешифратор разрядов, блоки сравнения, элементы И, мультиплексоры, выходы которых являются выходами устройства, первые информационные входы мультиплексоров соединены с соответствующими выходами основных усилителей считывания, а вторые - с соответствующими выходами резервных усилителей считывания, информационные входы которых подключены к соответствующим разрядным щинам резервного накопителя, а адресные входы соединены с со- ответствуюгцими адресными входами основных усилителей считывания, информационные входы которых подключены к соответствующим разрядным шинам основного накопителя, словарные шины которого подключены к соответствующим выходам дешифратора слов, входы которого являются адресными входами первой группы устройства и соединены с соответствующими входами блоков сравнения, выходы которых соединены с г.ходами соответствующих элементов И, адресные входы основных усилителей считывания соединены с соответствующими выходами дешифратора разрядов, входы которого являются адресными входами второй группы устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ, группу элементов ИЛИ, блок переадресации, дешифратор неисправных разрядов, выходы которого соединены с входами управления коммутацией соответствующих мультиплексоров, адресные входы соединены с выходами соответствующих элементов ИЛ11 группы, входы которых соединены с соответствующими выходами блока переадресации, входы которого соединены с выходами соответствующих элементов И и с соответствуюш1ми входами элемента , выход которого подключен к словарной шине резервного накопителя и соединен с входом сбросу дешифратора непсправш. рагчрядон .

| Электроника, 1981, т | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| СОСТАВ ДЛЯ ОБЕЗВОЖИВАНИЯ И ОБЕССОЛИВАНИЯ НЕФТИ, ИНГИБИРОВАНИЯ КОРРОЗИИ И АСФАЛЬТЕНО-СМОЛОПАРАФИНОВЫХ ОТЛОЖЕНИЙ | 1998 |

|

RU2129585C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-05—Подача