1

Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах специализированных цифровых вычислительных устрюйствах и вычислительных средах, построенных на больших интегральных схемах.

Известно арифметическое устройство, в котором операнды могут быть представлены последовательным кодом{ 1

Однако такие устройства обладают невысоким быстродействием, так как врмя вьтолнения операций в таких устройствах пропорционально п где п разрядность операндов, работе в сиетемах управления процессами в реальном масштабе времени, когда операнды поступают на вход непосредственно с преобразователей аналог-код или измерительных устройств поразрядного уравновешивания последовательно разряд на разрядом.

Такие устройства обладают также невысоким быстродействием при работе в вычислительной среде, когда результат, сформированный в одной ячейке, является операндом последуюдей, а каждая ячейка при этом выполняет определенную операцию. Кроме того, в таких устройствах при работе в вычис|лительной среде для связи между ячейками необходимо иметь по п шин на каждый операнд.

Наиболее близко к предлагаемому изобретению арифметическое устройство, содержащее регистры первого и второго операндов, информационные входы которых подключены соответствено к первой и второй группам информационных входов устройства, ВЫХОДУ накапливающего регистра и регистров первого и второго операндов соединены с входом сумматора 2. Устройство содержит, кроме того, блок анализа и блок фОЕ 4ирования переноса.

Недостатком такого устройства является низкое быстродействие.

Действительно, чтобы получить п разрядов результата, с помощью этого устройства, необходимо выполнять 2т циклов вычислений. При выполнении певых п циклов очередные разряды результата не вычисляются, а происходит только поразрядный ввод операндов. Фо ялирова-ние очередных разрядов результата осуществляется при выполнении последующих п циклов вычислений .

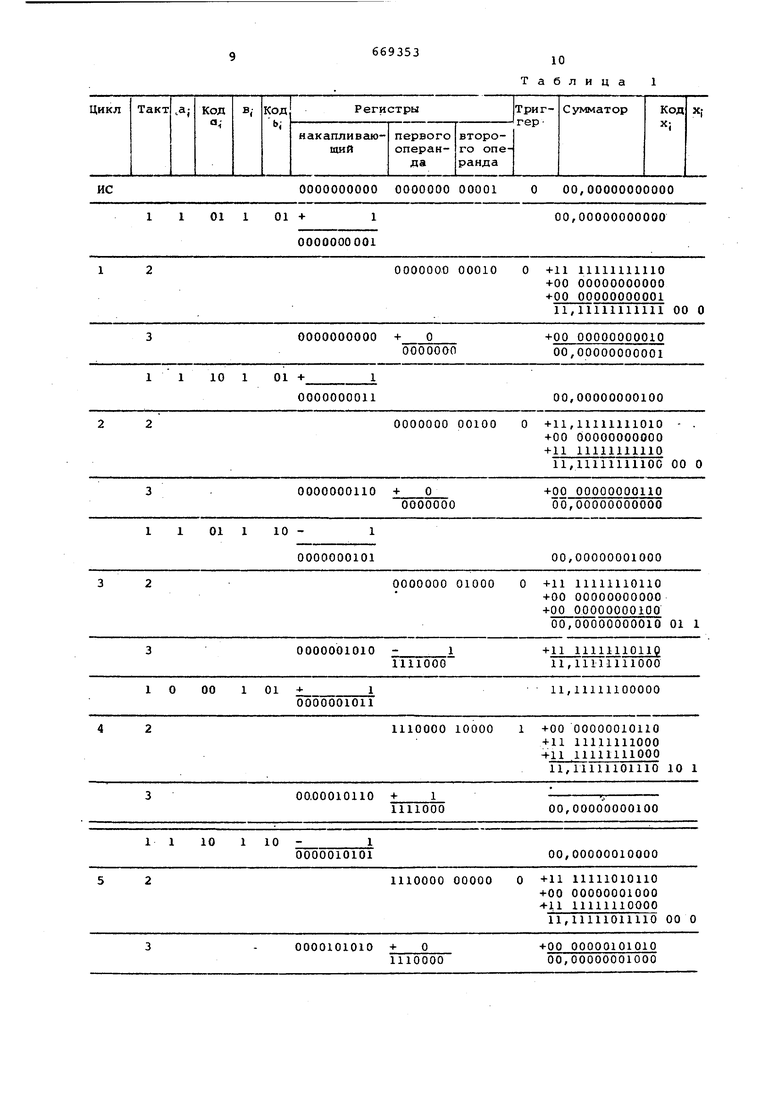

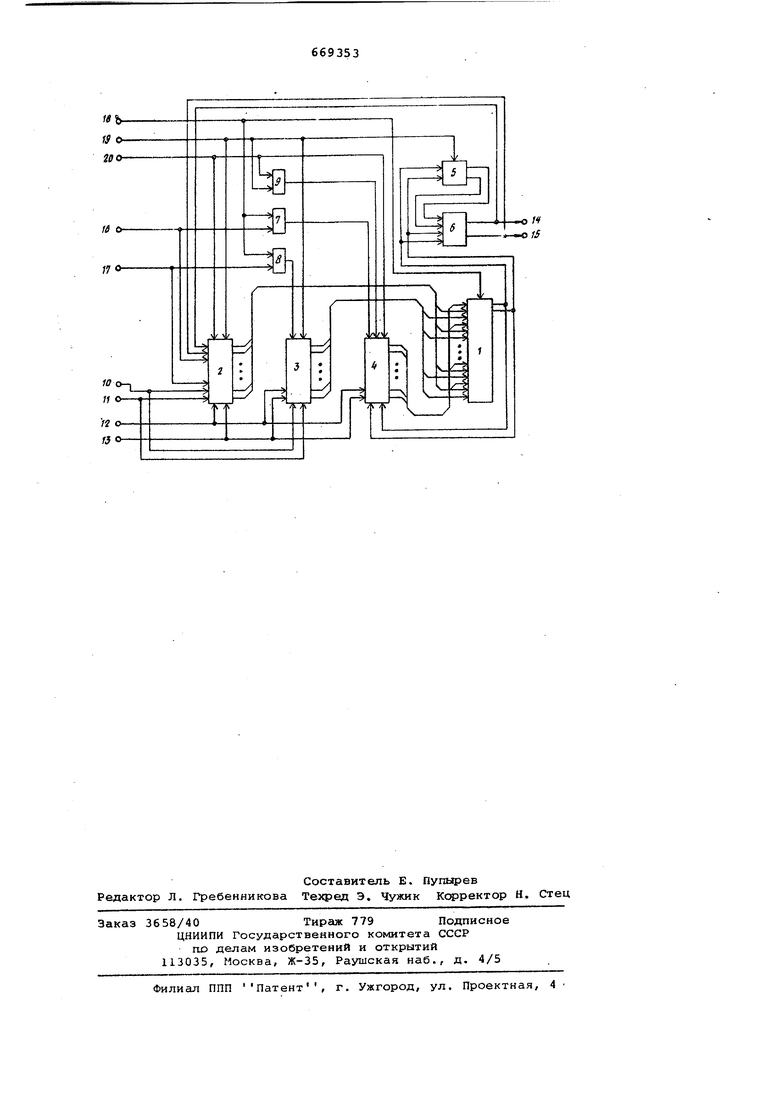

Таким образетл, время выполнения операции в этом устройстве равно Тцза 2л циклов. Перечисленные недостатки существенно снижают производительность устройства при работе в 11 еальном масштабе врамени, Особенно это проявляется в тех случаях, когда период поразрядного формирова|ния операндов вне устройства (например/ в измерительных приборах поразрядного уравновешивания) имеет большую продолжительность. При использовании известного устройства в качестве ячейки вычислител ной среды, информация от предыдущей ячейки в последующую передается после выполнения вычислений в предыдущей ячейке. Рассмотрим часть вычислительной среды, представляющей собой цепочку из К последовательно вкл ченных арифметических устройств. В течение первых п циклов происходит накопление операндов в первой ячейке, поскольку на ее входы операнды поступают в последовательном коде. Затем, в, течение п циклов происходит операция вычисления. Затем результат передается в последующую ячейку, поэтому дальше каждая ячейка вносит за держку в п циклов . Задержка, вносимая К устройствами, будет составлять п(К+1) циклов. Цель изобретения - увеличение быстродействия. Это достигается тем, что устройство содержит триггер, дешифратор, элемент ИЛИ и два элемента И, причем первый вход первого элемента И соеди йен с первым т.актирующим входом устройства, с тактируклдим входом сумматора и первым входом второго элемента И, Агорой вход первого элемента И Деление соединен с входом ройства и с первым управляющим входо регистра первого операнда, выход первого элемента И соединен с первым управляющим входом накапливающего регистра, второй управляющий вход которого соединен с выходом элемента ИЛИ, с первым входом которого сое динены второй тактирующий вход устро ства, тактирующий вход регистра второго операнда и тактируквдий вход три гера, второй вход элет1ента ИЛИ подключен К третьему тактнруквдему входу устройства и тактируквдему входу накапливающего регистра, третий и четвертый управляющие входы которого соединены соответственио с первым и вторым выходами сумматора, причем первый и второй выходы сумматора под ключены соответственно к первым и вт рым входам дешифратора и триггера, к третьему и четвертому входам дешиф ратора подключены первый и второй выхода триггера, а первый и второй выходы дешифратора подключены соответственно к первому и второму выхо дам устройства и к второму и третье му управляющим входам регистра перого операнда, к четвертому, пятому правляющим входам которого подключеы соответственно третий тактируюий вход устройства, и вход Умноение устройства, вход Умножеие устройства соединён с вторым ходом второго элемента И, выход оторого подключен к управляющему входу регистра второго операнда, к третьему и четвертому входам которого подключена первая группа информационных входов устройства, а к первому и второму входу накапливающего регистра подключена вторая группа информационных входов устройства, пятый и шестой управляющие входы регистра первого операнда соединены соответственно с вторым и третьим тактирующим входом устройства. На чертеже дана схема предлагаемого устройства. Устройство содержит (п+8) разрядный сумматор 1 (п-разрядность исходных операндов), (п+2) разрядный регистр 2 первого операнда, п разрядный регистр 3 второго операнда,{п+5) разрядный накапливающий регистр 4, триггер 5, дешифратор б, элементы И 7 и 8 и элемент ИЛИ 9, первую группу информационных входов 10 и 11, вторую группу информационных входов 12 и 13, первый и второй выходы 14 и 15 устройства, вход Деление 16 устройства, вход Умножение 17 устройства, первый, второй, третий тактирующие входы 18-20 устройства. Дешифратор 6 может быть построен в соответствии с системой переключательных функций вида (f, рд Р 9 где f - функция 1-го выхода (,2) дешифратора 6; р,д - соответственно значения старшего разряда сумматора 1 и значение состояния триггера 5. Исходные операции А и В и результат X представлены двоичным избыточным кодом с цифрами 1, О, 1 и имеют вид А . О: 2 : П -, в.Д х-Ь,-2- где а,- , в; , X; е {1, О, 1} Каждый разряд числа в избыточном представлении кодируется двумя цифрами из множества При этом циф-. ре 1 соответствует сигнал на входе 11 или 13, или на выходе 15. Цифре 1 со-i ответствует сигнал на входе 10 или 12, или на выходе 14. Цифре О соответствует отсутствие сигналов на входах 10, 11 и 12, 13 или на выходах 14 и 15. Коды операндов А к В поступают поразрядно ссоответственно на входы 10, 11 и 12, 13 одновременно, то ест в каждый момент времени на входы пос тупают разряды операндов с одинаковыми весами. На величины А и В накладываются следующие ограничения О 4 А 2 2 В : 1, Устройство работает слеяуквдим образом. Перед операцией вычисления на вхо да 16 и 17 поступает код операции, который удерживается до окончания операции. При этом операции деления соответствует сигнал на входе 16, операции умножения - на входе 17, а операции сложения соответствует отсу ствие сигналов на входах 16 и 17. К началу каждого i-ro цикла вычислений (, 2, ... п+З) на входы 10, 11 и 12, 13 поступают цифры очередных разрядов соответственно а; и в; . В каждом.цикле вычислений на тактирующие входы 18, 19 и 20 поочередно поступают соответственно тaктиp кяциe сигналы у, , у. и у . Деление (А/В). В исходном состоянии в младшем разряде регистра 3 записана единица, а остгшьные регистры, сумматор 1 и триггер 5 установлены в нулевое состояние. Перед началом вычислений на вход 16 кода операции поступает сигнал, который поступает на первый вхо элемента И 7 и на управляющий вход (n-l)-ro суммирующего разряда регист ра 2, открывая тем самым входы этого разряда. В первом такте цикла вычисления сигнал у, с входа 18 поступает через элемент И 7 на цепь приема кода регистра 4 и на цепь сдвига сум матора 1. В результате этого в младшем разряде регистра 4 происходит су мирование содержимого этого регистра с очередным разрядом BJ , то есть в регистре 4 происходит накопление делителя в, а содержимое сумматора 1 сдвигается на два разряда влево. Во втором такте цикла вычисления сигнал ijj с входа 19 поступает на цепь при ема кода триггера 5, через элемент ИЛИ 9 на цепь выдачи кода регистра 4 и на цепи выдачи кода и сдвига регис ров 2 и 3. В результате этого в триг гер 5 записывается предыдущее состоя ние старшего разряда сумматора 1, а в сумматоре 1 происходит суммирование содержимого этого блока с кодами, поступившими с выходов регистров 2-4 и одновременно с этим происходит сдвиг содержимого регистров 2 и 3 на один разряд влево (одновременное сум мирование в сумматоре 1 и запись пре дыдущего состояния старшего разряда этого блока в триггер 5, а также одновременная выдача кода из регистров 2 и 3 и сдвиг содержимого этих регистров возможны, так как бумматор 1 и регистры 2 и 3 являются сдвигающими, а следовательно, каждый их разряд должен бьггь построен на паре триггеров или на триггерах с внутренней задержкой). При этом код на выходе регистров 2 и 3 зависит от сигналов соответственно на входах 12, 13 и 10, 11, Бели присутствует сигнал на входе 10 или 12 (, ), то из регистров 3 и 2 выдается прямой код, а если сигнал на входе 11 или 13 (aj 1, ), то .ьщается дополнительный код. При отсутствии сигналов на входах 10, 11 или 12, 13 (aj JD, Bj 0), коды из регистров 3 и 2 не выдаются. Код на выходе регистра 4 зависит от предыдущего состояния стараего (знакового) разряда с матора 1. Если в этом разряде записан нуль (положительный знак), то из регистра 4 выдается дополнительный код, а если записана единица (отрицательный знак), -товыдается прямей код. При выдаче дополнительного кода из регистров 3 н 4 на входы сумматора выдается обратный код содержимого этих регистров, а «а входы свободных (не связанных с выходами .регистров 3 и 4} разрядов сумматора 1 поIдаются единичные сигналы и, кроме того, единичные сигналы подашэтся на соответствукйцие входы переноса младшего разряда сумматора 1, При выдаче дополнительного кода из регистра 2 на входы сумматора вьадается обратный код содержимого этого регистра, а на входы свободных разрядов сумматора 1 подается инверсное значение старшего разряда регистра 2 и, кроме того, единичное значение подается на соответотвукнаий вход переноса младшего разряда сумматора 1. .При выдаче прямого кода на свободные входы подаются единичные сигналы. Перед началом третьего такта цикла вычисления дешифратор 6 анализирует состояние триггера 5 и старшего разряда сумматора 1 и на выходах дешифратора. 6 появляется кед очередного разряда результата х; , который поступает на выходы 14 и 15 и на входы (n-l)-ro суммирующего разряда регистра 2. В третьем такте цикла вычислений сигнал yj с входа 20 поступает через элемент ИЛИ 9 на цепь выдачи кода регистра 4, поступает на цепь приема кода регистра 2 и на цепь сдвига регистра 4. При этом с регистра 4 на входы сумматора 1 передается код, соответствующий предыдущему состоянию старшего разряда сумматора 1, содержимое регистра 4 сдвигает ся на один разряд влево, а в (п-1)-м разряде регистра 2 производится суммирование содержимого регистра 2 с обратным значением кода х,- , То есть, если X)1 (сигнал на выходе 15), то к (п-1)-му разряду прибавляется единица, если (сигнал на выходе 14, то иэ (n-l)-ro разряда вычитает ся единица, а если Х| 0 (сигналы на выходах 14 и 15 отсутствуют), то регистр 2 не изменяет своего состояния Таким образом в регистре 2 производи ся накопление дополнительного кода результата X, На этом заканчивается один цикл вычислений. Разряд результата с весом 2 поступает на выходы результата через три цикла вычислений после поступления разрядов операндов с весами 2 Поэтому- для получения результата с точностью 2 необходимо выполнить (п+3) циклов вычислений, Рассмотрим работу устройства в режиме деления на примере. Пусть А в(11/32)зес, (0,lilOi)jj ,В (21/32 )ajc (0,11111) . Для этих значений операндов , поэтому необходимо вы полнить восемь циклов вычислений. Процесс вычислений иллюстрируется в табл. 1 состояний сумматора и регист ров устройства. Результат вычислений для этих значений операндов равен X (001,I0001)jj5 17/32)а. Умножение (А х В)-. В ИСХОДНОМ состоянии в (п+3)-м разряде регистра 4 записана единица а остальные регистры, сумматор 1 и триггер 5 установлен1ы в нулевое сос тояние. Перед началом вычислений на вход 17 кода операции поступает сиг нал, который поступает на первый вход элемента И 8 и на управляющий вход (п+1)-го суммирующего разряда регистра 2, открывая тем самым входы этого разряда. В первом такте ци ла вычислений сигнал у с входа 18 поступает через элемент И 8 на цепь приемоь кода регистра 3 и поступает на цепь сдвига сумматора 1. В резул тате этого содержимое сумматора 1 сдвигается на два разряда влево, а в младшем разряде регистра 3 происходит суммирование содержимого этог регистра с очередным разрядом та , то есть в регистре 3 происходит накопление множителя В. В двух оставшихся тактах цикла умножения устрой ство работает аналогично двум послед ним тактам цикла деления. При этом в регистре 2 производится накоплени множимого А, Рассмотрим работу устройства в режиме умножения на примере для тех же операндов. Процесс вычислений ил люстрируется в табл. 2 состояний су матора и регистров устройства. Результат вычислений для этих значени операндов равен X (000,n001)ujg . (7/32) . ложение (А + В). В исходном состоянии в (п+4)-м азряде регистра 4 и в младших разядах регистров 2 и 3 записаны единиы, а сумматор 1 и триггер 5 установены в нулевое состояние. Сигналы на ходах 16 и 17 отсутствуют. В первом акте вычислений сигнал у с входа 18 существляет сдвиг содержимогосуматора 1 на два разряда влево. В двух ставшихся тактах цикла сложения стройство работает аналогично двум оследним тактам цикла деления..При том в регистрах 2-4 происходит лишь, оответствующие сдвиги содержимого. Из рассмотренного примера видно/ то для получения результата с точносью 2 необходимо выполнить п+3 циклов вычислений. Отношение ыстродействия известного и предлааемого устройства, составляет Тиьб. 2п ТПРЙ. Если принять п а 32, что соответствует показателям современных ЦВМ, то Tyjg « IfS- fo ес:ть быстродействие предлагаемого устройства выше быстродействия известного устройства при работе в реальном Масштабе времени в 1,8 раз. Определим задержку, вносимую К устройствами при использовании их в , вычислительной среде. Как было показано, разряд результата с весом 2 поступает на выходы через три цикла вычислений после поступления разрядов операндов-с весами 2 . Так как очередной разряд, полученный на выходе устройства, обрабатывается другим устройством в следующем цикле, задержка, вносимая одним устройством, составляет четыре цикла. Задержка, вносимая К устройствами, будет составлять 4К-1 циклов. Таким образом, отношение быстродействия известного устройства и предлагаемого при использовании их в вычислительной среде составляет п( п 4К-1 4 При п % 32 использование в вычислительной среде предлагаемого устройства позволяет увеличить быстродействие .rio сравнению с известным устройством в 32/4 «8 раз. Таким образом, достигается цепь предлагаемого изобретения.

669353

10

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для деления | 1976 |

|

SU590738A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

0000000000 0000000 00001

ИС

00,00000000000

- 41 0000101010

е 2

- ..

0000000100 0000000 00000

чс

Пр ояолже ние т а бл. 1

00,00000100000

+11 iiiioioiioo

1100000 00000

+00 00000000000 +00 00000000000

0000000 00000

+11 11010110000 +00 ООООГОЙООООО +00 00000000000

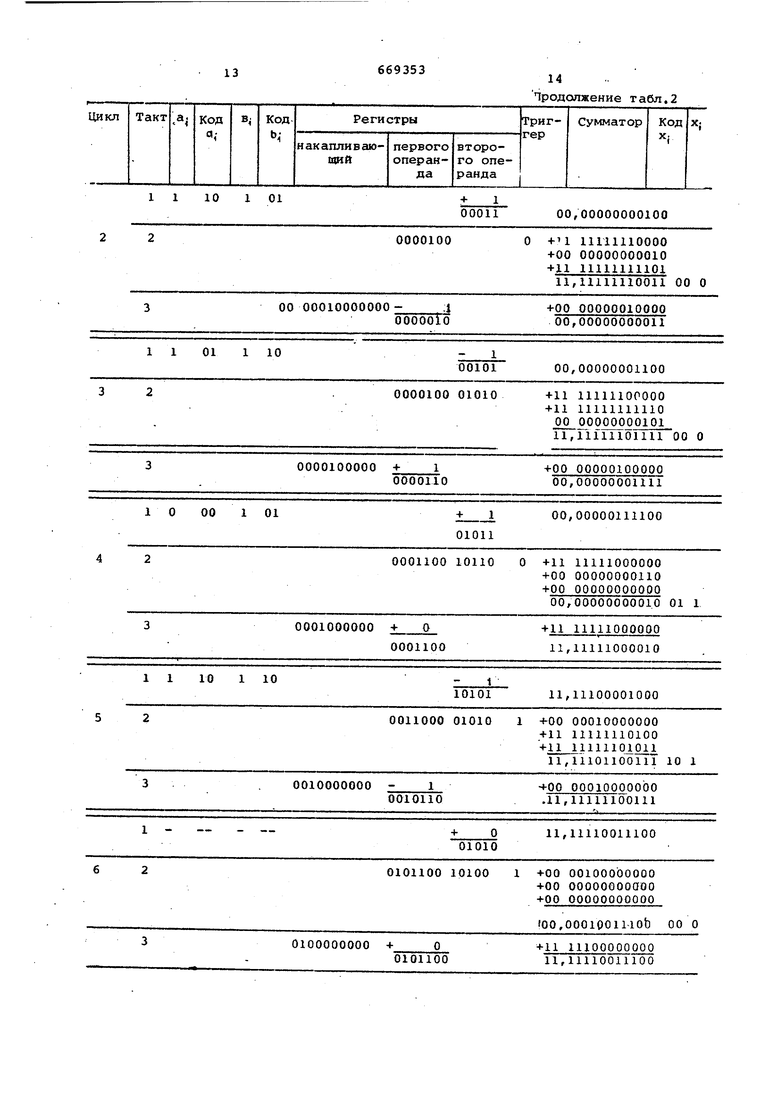

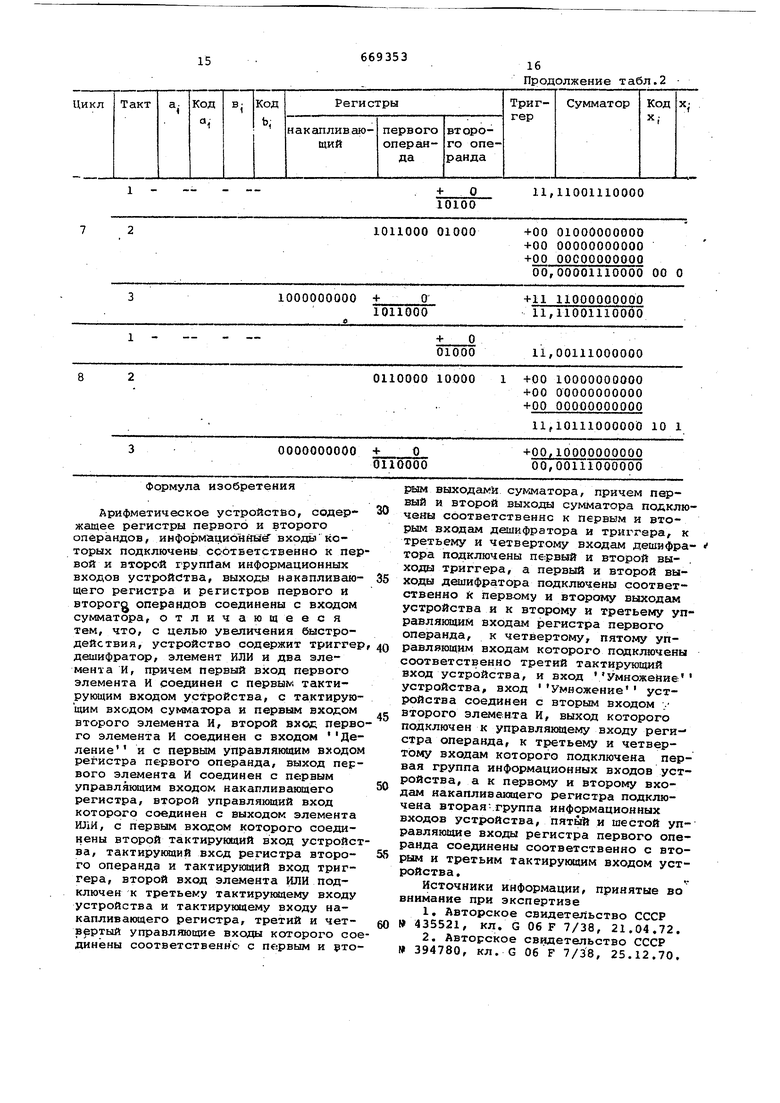

Та б л и ц а 2

00,00000000000

13

01

10

1 1

00010000000 10

1 1

01

0010000000 1 0100000000

669353

14 Чродояжение табл.2

00011

00,00000000100

fl linillOOOO +00 00000000010 +11 11111111101 11,11111110011 00 о

+00 00000010000

;l

оооооТо 00,00000000011

00,00000001100

00101

01010

-HI 11111100000 +11 11111111110 00 00000000101

11,11111101111 00 о

+11 11111000000

0001100 10110 +00 00000000110 +00 00000000000

+00 00010000000

01010 +11 11111110100 +11 111111OJ. 01.1. 11,11101100111 10 1

+00 00010000000 .11,11111100111

0010110

11,11110011100

1 +00 00100000000

10100 +00 00000000000 +00 00000000000

I00,0001001110b 00 о

+11 11100000000

0101100 11,11110011100

Такт

Цикл

1

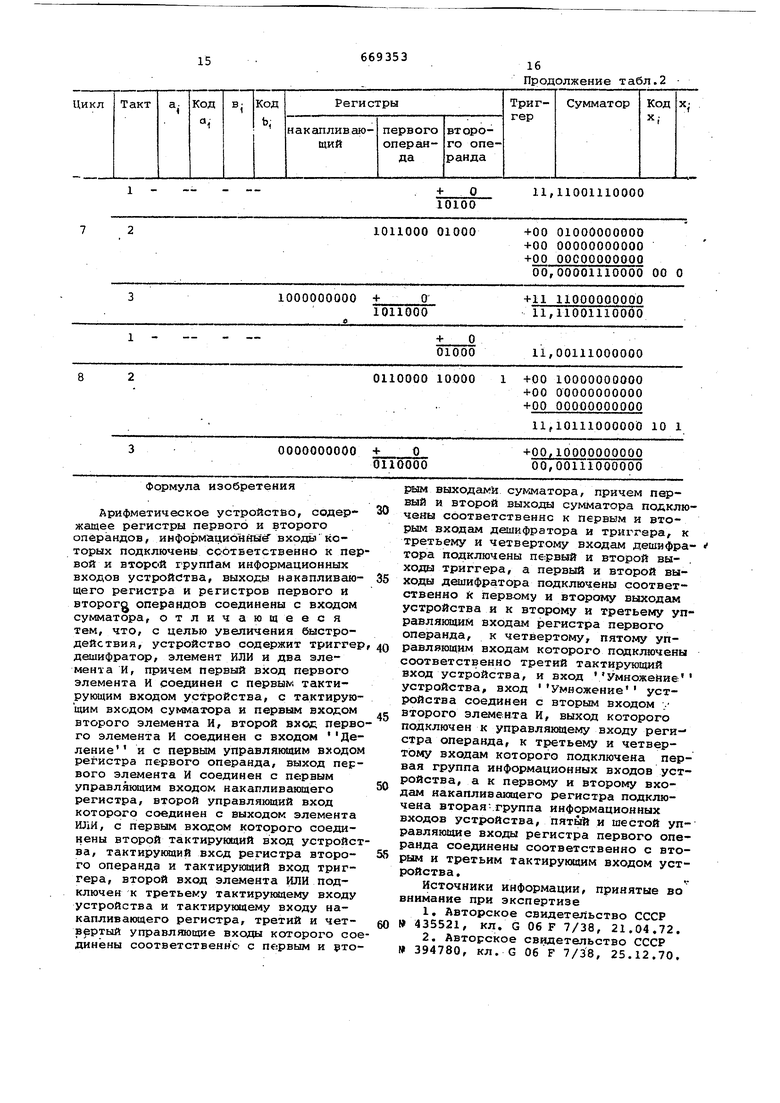

0000000000 Формула изобретения Арифметическое устройстйо, содержащее регистры первого и второго операндов, информацибнйЫё входыкоторых подключены соответственно к пер вой и второй группам информационных входов устройства, выходы накапливающего регистра и регистров первого и BTOporg операндов соединены с входом сумматора, отличающееся тем, что, с целью увеличения быстродействия, устройство содержит триггер дешифратор, элемент ИЛИ и два элемента И, причем первый вход первого элемента И соединен с первые тактирующим входом устройства, с тактирующим входом сумматора и первым входом второго элемента И, второй вхсщ перво го элемента И соединен с входом Де ление и с первым управляющим входом регистра первого операнда, выход пер вого элемента И соединен с первым управляющим входом накапливающего регистра, второй управляющий вход которого соединен с выходом элемента ШШ, с первым входом которого соединены второй тактирующий вход устройс ва, тактирующий вход регистра второго операнда и тактирующий вход триггера, второй вход элемента ИЛИ подключен к третьему тактируквдему входу устройства и тактирующему входу накапливающего регистра, третий и четвертый управляющие входы которого со динены СООТВетСТВеННс с П€;рВЫМ и 9ТО

11,11001110000

10100

+00 01000000000

01000 +00 00000000000 +00 00000000000 00,00001110000 00 о

10000

1 +00 10000000000 +00 00000000000 +00 00000000000

11,10111000000 10 1

+00,10000000000

о

0110000 00,00111000000 Ж1М выходами сумматора, причем первый и второй выходы сумматора подключены сЬответственнс к первым и вторым входам дешифратора и триггера, к третьему и четвертому входам дешифратора подключены первый и второй выходаа триггера, а первый и второй выходы дешифратора подключены соответственно к первому и второму выходам устройства и к второму и третьему управляющим входам регистра первого операнда, к четвертому, пятому управляющим входам которого подключены соответственно третий тактирующий вход устройства, и вход Умножение устройства, вход Умножение устройства соединен с вторым входом . второго элемента И, выход которого подключен к управлякнцему входу регистра операнда, к третьему и четвертому входам которого подключена первая группа информационных входов устройства, а к первому и второму входам накапливающего регистра подключена вторая-группа информационных входов устройства, пятьй и шестой управляющие входы регистра первого операнда соединены соответственно с вторым и третьим тактирующим входом устройства . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 435521, кл. G 06 F 7/38, 21.04.72. 2.Авторское свидетельство СССР 394780, кл. G 06 F 7/38, 25.12.70.

0

о/

.-«0/5

Авторы

Даты

1979-06-25—Публикация

1977-01-07—Подача