вого элемента ИЛИ, третий вход второго элемента И соединен с другими входами и выходами регистра числа, выход третьего элемента ИЛИ подключен к управляющим входам адресного блока и регистра числа, а выход пятого элемента ИЛИ - к другому входу формирователей разрядных токов, третьи входы четвертого и пятого элементов И являются соответственно входом записи и первым входом считывания устройства, яторы входом считывания которого является первый вход шестого элемента И, второй вход которого является входом опроса устройства и соединен е входом блока задержки, четвертый выход которого подключен к второму йходу третьего элемента И,первый выход второго триггера являетсявыходом сигнала неисправности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957276A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство без разрушения информации | 1978 |

|

SU750563A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее накопитель, одни из входов которого соединены с выходами формирователей разрядных токов, а другие входы - с выходами адресного блока, одни из входов которого являются адресными входами устройства, и регистр числа одни из входов и выходов которого подключены соответственно к в| 1ходам накопителя и к одним из входов формирователей разрядных токов, а другие входы и выходы являются информационными входами и выходами устройства соответственно, отличающ е е с я тем, -что, с целью пбвьпнения быстродействия и надежности устройства за счет блокировки записи ннформации при обнаружении неисправности, в него введены триггеры, блок задержки, блок контроля, элементы ИЛИ и элементы И, причем первые входы триггеров с первого по четвертый объединены и являются входом установки устройства, входом блокировки контроля которого является .второй вход первого триггера, выходы первого и второго элементов И подключены соответственно к первому и второму входам блока контроля, выход которого соединен с вторым входом второго триггера, первый выход которого подключен к первому входу третьего элемента И, а второй выход - к первым входам четвертого и пятого элементов И, вторые входы которых соединены с первым выходом блока задержки, второй выход которого подключен к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с другими входами адресного блока и с выходом первого триггера, выход шестого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и первым входом второго элемен та ИЛИ, второй вход которого подключен к первому входу первого триггера, а выход - к первому входу пятого триггера, второй вход третьего триггера соединен с выходом пятого элемента И, а выход - с первыми входами третьего элемента ИЛИ и седьмого О 4; элемента И, второй вход которого подключен к третьему выходу блока задержки, а выход - к первому входу четвертого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом четвертого элемента И. и с вторым входом пятого триггера, выход которого подключен к второму входу третьего элемента ИЛИ и первому входу пятого элемента ИЛИ, второй вход которого и третий вход третьего элемента ИЛИ соединены с выходом четвертого триггера, второй вход которого подключен к выходу пер

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и других вычислительных устройствах.

Известно 3запоминающее устройство с автономным контролем, содержащее регистр адреса, накопитель, схему управления, регистр выходного числа, схему контроля, сумматор, группу вентилей и вентили зон, регистры, счетчик адреса и собирательные схемы Cl3. ./

Недостатком этого устройства является пониженная надёжность.

Наиболее близким к предлагаемому изобретению является запоминающее устройство с автономным контролем, содержащее накопитель, усилители считьшания,регистр числа, формирователи токов записи, девифратор адреса, регистр адреса, блок обнаружения неисправности, шины записи, и чтения, выходные шины, элементы И, ИЛИ, дополнительный регистр, блок коррекции режима, причем первые входы накопителя соединены с выходами формирователей токов записи, а вторые входы - с выходами дешифратора.адреса, входы которого соединены с выходами регистра адреса, выходы накопителя соединены С входами усилителей считывания, выходы которых подключены к входам блока обнаружения неисправностей и одним из входов элементов И, выходы блока коррекции соединены с одними из входов дополнительного регистра 23.

Недостатком данного устройства является пониженная надежность записи и считывания информации за счет отсутствия контроля числовой информации и фиксации ошибок и за счет возможности записи искаженной инфор5 мации по правильным и искаженным адресам, а также отсутствия сигнализации о наличии неисправности. Введение дополнительных операций в блоке обнаружения неисправностей и блоке

О коррекции режима значительно удлиняет общее время цикла, снижая быстродействие запоминающего устройства в режимах записи и считывания с регенерацией .

15 Целью изобретения является повышение быстродействия и надежности устройства за счет блокировки записи информации при обнаружении неисправности.

20 Поставленная цель достигается тем что в запоминающее устройство с автономным контролем, содержащее накопитель, одни из входов которого соединены с выходами формирователей раз25 рядных токов, а другие входы - с выходами адресного блока, одни из входов которого являются адресными входами ycTpoftCTBa, и регистр числа, одни из входов и выходов которого

30 подключены соответственно к выходам накопителя и к одним из входов формирователей разрядных токов, а другие входы и выходы являются информационными входами и выходами устройст35 ва, введены триггеры, блок задержки, блок контроля, элементы ИЛИ и элементы И, причем первые входы триггеров с первого по четвертый объединены и являются-входом установки устройства

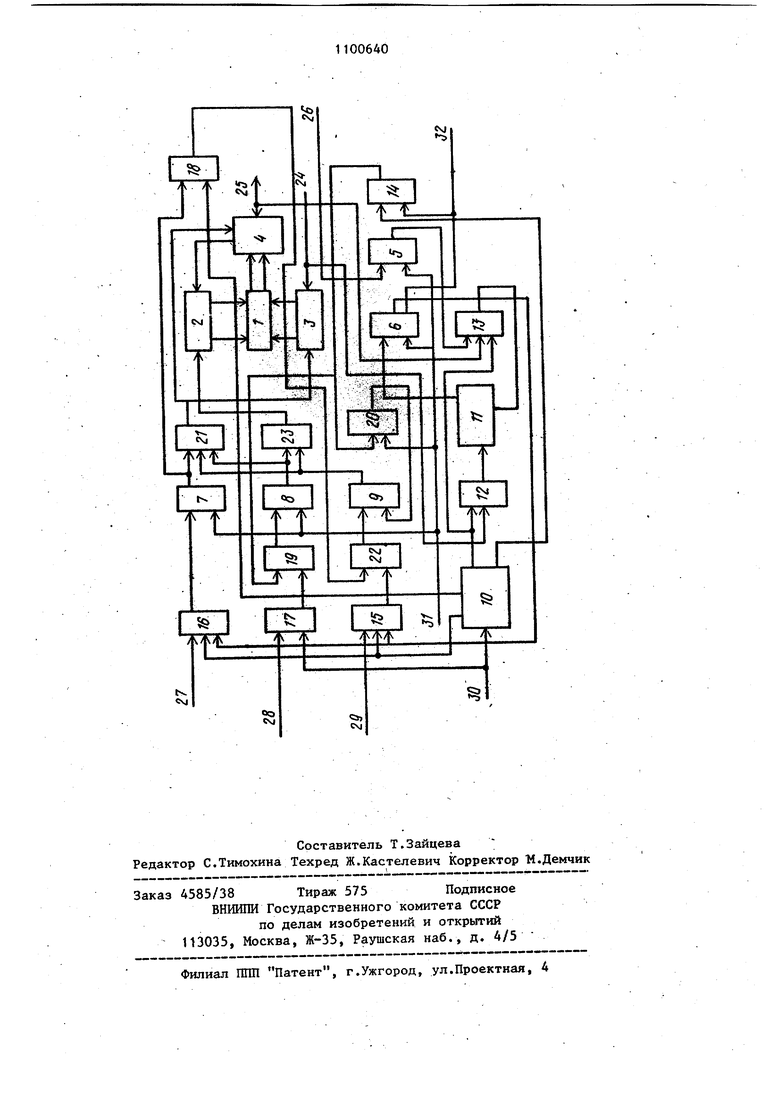

40 входом блокировки контроля которого является второй вход первого триггера, выходы первого и второго элементов И подключены соответственно к первому и второму входам блока контроля, выход которого соединен с вторым входом второго триггера, первый выход которого подключен к первому входу третьего элемента И, а второй выход - к первым входам четвертого и пятого элементов И, вторые входы которых соединены с первым выходом блока задержки, второй выход которого подключен к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с другими входами адресного блока и с выходом первого триггера, выход шестого элемента И подключен к первому входу первого элемента ИЛИ, вто рой вход которого соединен с выходом третьего элемента И и первым входом второго элемента ИЛИ, второй вход которого подключен к первому входу первого триггера, а выход - к первому входу пятого триггера, второй вход третьего триггера соединен с выходом пятого элемента И, а выход - с первыми входами третьего элемента ИЛИ и седьмого элемента И, второй вход которого подключен к третьему выходу блока задержки, а, выход - к первому входу четвертого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом четвёртого элемента И и с вторым входом пятого триггера, выход которого подключен к второму вхо ду третьего элемента ИЛИ и первому; входу пятого элемента ИЛИ, второй вход которого и вход третьего элемента ИЛИ соединены с выходом четвертого триггера, второй вход которого подключен к выходу первого элемента ИЛИ, третий вход второго элемента И соединен с другими входами и выходами регистра числа, выход третьего элемента ИЛИ подключен к управляющим входам адресного блока„ и. регистра числа, а выход пятого элемента ИЛИ - к другому входу формирователей разрядных токов, третьи входы четвертого и пятого элементов И являются соответственно входо записи и первым входом считывания устройства, вторым входом считывани которого является первый вход шесто го элемента И, второй вход которого является входом опроса устройства и соединен с входом блока задержки, четвертый выход которого подключен к второму входу третьего элемента И, первый выход второго триггера является выходом сигнала неисправности устройства. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит накопитель 1, формирователи 2 разрядных токов, адресный блок 3, регистр 4 числа, первый - пятый триггеры 5-9, блок 10 зaдepжкиJ блок 11 контроля, элементы И и с первого по седьмой 12-18 и первый - пятый элементы ИЛИ 19-23. На чертеже обозначены адресные входы 24, информационные входы и выходы 25 вход 26 блокировки контроля, первый 27 и второй 28 входы считывания, вход 29 записи, вход 30 опроса, вход 31 установки и выход 32 сигнала неисправности устройства. Устройство работает следующим образом. Перед началом работы в любом режиме (до прихода сигнала Опрос) все элементы и блоки устройства устанавливаются в исходное состояние сигналом Уст. О на входе 31. В режиме считывания со стиранием старой информации на вход 27 элемента И 16 поступает сигнал Считывание с гашением, а на вход 30 - сигнал Опрос. При отсутствии запрещающего потенциала с выхода триггера 6 этот сигнал проходит на триггер 7, устанавливая его в состояние 1 и разреша прием кода адреса в блок 3. Код адреса одновременно поступает через элемент И 12 на блок 11, в котором производится контроль правильности поступившего адреса по сигналу с второго выхода блока 10. При неправильном адресе триггер 6 устанавливается в состояние 1, блокируя этот режим, и на выход 32 подается сигнал Неисправность. При правильном адресе в блоке 3 возбуждаются соответствующие дешифраторы и формирователи, и из накопителя 1 на регистр 4 поступает код числа, которьй с выходов 25 передается в другие устройства ЦВМ (на чертеже не показаны), а во всех разрядах числа выбранного адреса (кроме контрольных) осуществляется запись О. После появления в регистре 4 кода числа по разрешающему потенциалу с выхода триггера 7 через элемент И 18 и элемент ИЛИ 22 сигнал с блока 10 устанавливает в состояние 1 триггер 9, разрешая запись правильных контрольных разрядов, соответствующих нулевому коду числа. В режиме считывания с регенерацие на входы 28 и 30 элемента И 17 посту пают сигналы Считывание и Опрос, которые через элемент. ИЛИ 19 устанавливают в единичное состояние триггер 8, разрешающий через элементы ИЛИ 21 и 23 работу блока 3, регистру 4 и формирователей 2 при регенерации. При поступлении неправиль ного адреса работа устройства в этом режиме блокируется и вьщается сигнал Неисправность на выход 32, а в случае неправильно считанного кода вьщается только сигнал Неисправность. Если код адреса соответст- . вует контрольным разрядам,то запускаются адресные формирователи (на чертеже не показаны) в блоке 3 и фор мирователи 2, осуществляя перезапись считанной информации. В режиме записи сигнал Опрос с выхода блока 10 по разрешающим потенциалам сигнала Запись на входе 29 и на выходе триггера 6 проходит через элемент И 15 и элемент ИЛИ 22. устанавливает в состояние 1 триггер 9, которьй позволяет осуществить, работу устройства в данном режиме, запуская через элементы ИЛИ 21 и 23 формирователи 2, блок 3 и регистр 4. При поступлении неправильного адреса работа устройст ва в данном режиме блокируется, как и при поступлении неправильного кода числа через элементы И 12 и 13 с помощью блока 11 и триггера 6. При этом в ячейке накопителя 1 сохраняется старая информация (не разрушает ся и не искажается), и устройство переходит в режим работы считывания с регенерацией. Если по программе работы отсутствует необходимость контроля поступающей из других устройств ЦВМ информации, то на вход 26 триггера 5 подается сигнал Блокировка контроля, запрещающий на элементе И 13 поступления кода числа на контроль. Если в процессе работы сигналом с блока 11 триггер 6 устанавливается в состояние 1 и требуется сохранить считанную информацию, то сигналом с блока 10 через элемент И 14 всегда блокируется работа устройства в режиме записи (через элемент ИЛИ 20 триггер 9 устанавливается в состояние О) и осуществляется регенерация уже считанной информации путем установки в состояние 1 триггера 8 (через элемент ИЛИ 19). Таким образом, предлагаемое запоминающее устройство с введенными в него триггерами 5-9, блоком 10 задержки, элементами И 12-18 и элементами Ш1И 19-23, позволяющими автономно осуществлять контроль на всех этапах всех режимов адресной, входной и считанной информации, оперативно автоматически вмешиваться в выполнение режимов, изменяя заданнь режим работы и тем предотвращая разрушение старой правильной информации и запись новой искаженной информации, значительно повышает надежность устройства. Кроме того, значительно повышается быстродействие устройства за счет совмещения операции контроля и подготовки следукщих операций, а также за счет оперативного контроля входной и выходной информации и отсутствия повторения предьвдуших режимов работы. Технико-экономическое преимущество предлагаемого устройства заключается в более высоком быстродействии и более высокой надежности по срав- нению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЗАПОМИНЛЮЩР.Е УСТРОЙСТВО | 0 |

|

SU353281A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-06-30—Публикация

1983-03-11—Подача