I

Изобретение относится к области цифровой вычислительной техники, в частности, к запоминающим устройствам, состоящим из нескольких независимых секций.

Известно устройство для управления памятью, состоящее из нескольких секций для повышения производительности машины fl|.

Известное устройство содержит адресный регистр, выходы старших разрядов которого соединены со входами преобразователя кода адреса и входами адресных коммутаторов, а младших - подключены к входам дешифратора.

Известное устройство обеспечивает возможиость выборки из памяти при одном обращении одновременно от I до п ячеек по последовательным адресам, начиная от адреса, указанного в команде. Количество выбираемых ячеек (формат обращения) задается кодом, поступающим на специальные входы устройства.

Для возможности одновременной передачи и приема из памяти слов, а также для управления форматом обращений помимо усложнения самого устройства управления памятью известного устройства необходимо существенное усложнение процессоров и вычислительной системы в цело.м. Поэтому применение известного устройства не позволяет повысить производительность, так как время выборки информации и время цикла у этого устройства не уменьшается по сравнению с отдельной секцией памяти (с отдельным блоком ).

Цель предлагаемого изобретения - повысить эффективное быстродействие секционированной памяти и тем самым повысить производительность тех машин, в которых обмен с памятью осуществляется одним словом.

Указанная цель достигается тем, что в устройство для управления блоками памяти введены формирователи признака готовности и выходные коммутаторы, управляющие входы которых соединены с соответствующими выходами дешифратора и формировате5лей признаков готовности, входы которых подключены к выходам адресных коммутаторов,

В настоящем изобретении обеспечивается опережающая выборка информации, заключающаяся в том, что при считывании по какому-либо адресу производится одновременно и обращение по п-1 адресам, образующим вместе с выбранным адресом некоторый непрерывный массив ячеек памяти.

например такон, когда выбранный адрес является первичной ячейкой массива.

Информация из этих, дополнительно опрашиваемых ячеек памяти подготавливается к выдаче. Если следующее считывание производится по адресу, который предварительно опрошен, то обращение отрабатывается за значительно меньшее время, чем время выборки из секции памяти.

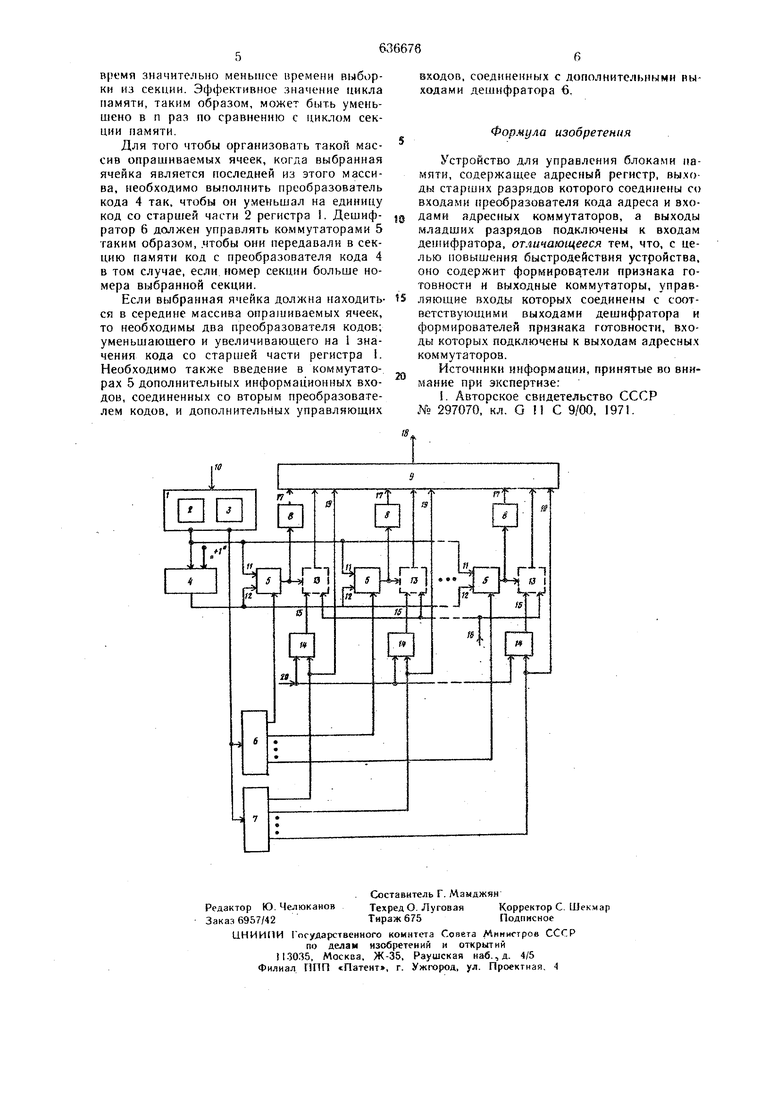

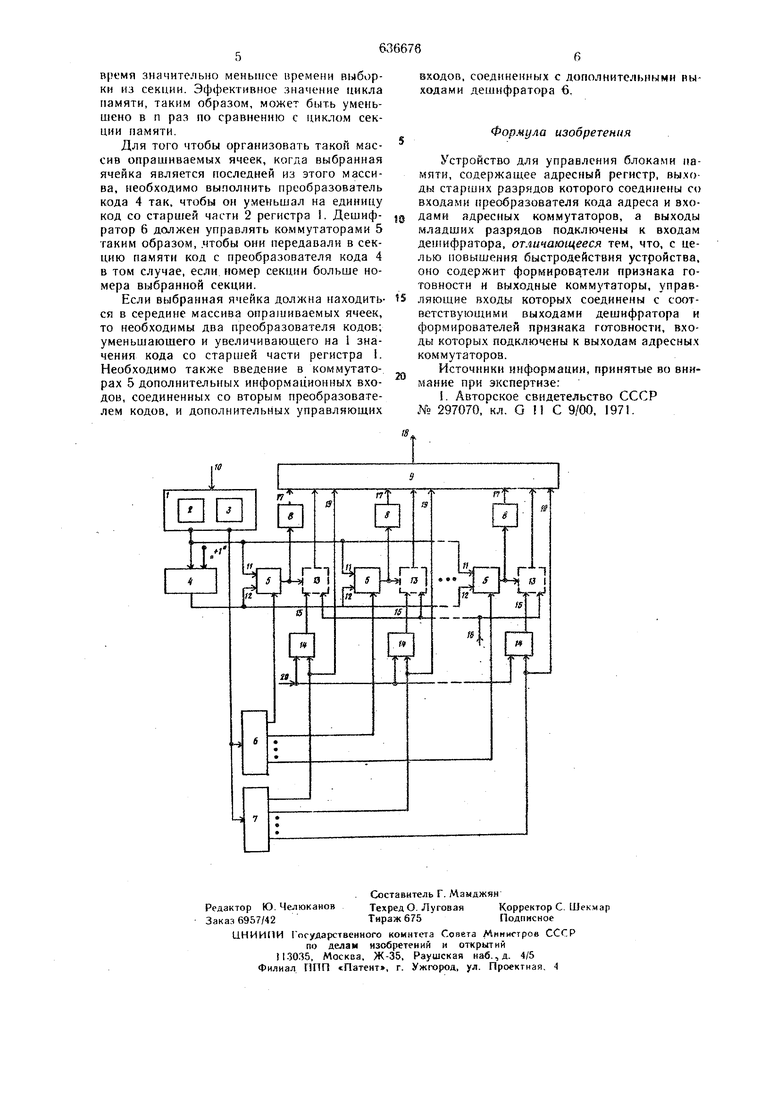

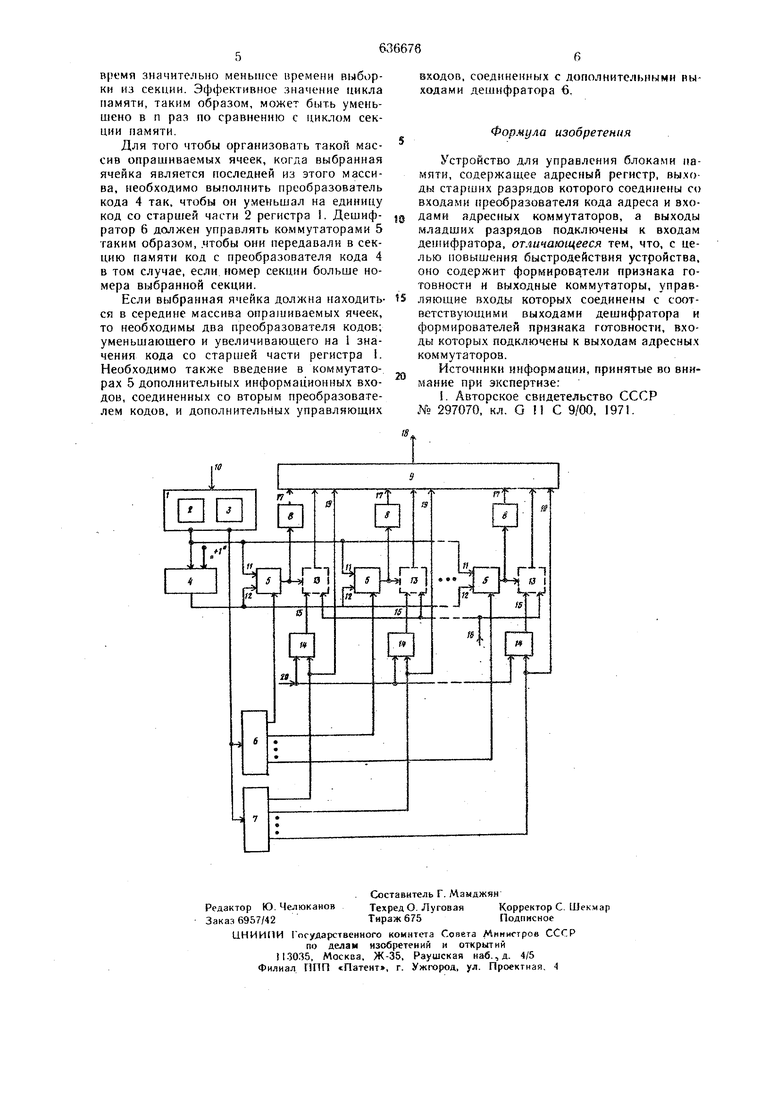

На чертеже представлена блок-схема предлагаемого устройства управления с таким массивом дополнительно опрашиваемых ячеек, когда выбираемая ячейка является первой в массиве, и для такой памяти, которая допускает смену хранимой информации.

Устройство содержит адресный регистр 1, разделенный на две части - cTapiuyio 2 и младшую 3; преобразователь 4 кода адреса для увеличения на единицу содержимого старшей части адресного регистра; п адресных коммутаторов 5 для передачи на входы п секций памяти и п формирователей п изиаков готовности информации, либо содержимого старшей части адресного регистра 2, либо выходного кода преобразователя 4 Кода адреса; дешифратор 6 сигналов управления сборками адресов; дешифратор 7 выбираемой секции для выработки управляющего сигнала, который определяет выбранную секцию памяти; формирователи 8 признаков готовности информации, которые, начиная с момента смены адреса для секции памяти, вырабатывают на время выборки из секции памяти сигнал, блокирующий выдачу информации через выходной коммутатор 9.

Входы адресного регистра 1 соединены с входными шинами 10 адреса.

Адресные коммутаторы 5, имеющие информационные входы П и 12, включены между выходом старшей части 2 адресного регистра, к которому подключены информационные входы П, и адрес.ными входами секций памяти 3.

Для осуществления записи информации введены схемы «И 14, которые одними свопми входами присоединены к дещифратору 7 выбираемой секции, а выходами - к входам 15 «-Запись в секцию секций памяти. По CHfHajiy, поступающему на вход 15, производится запись в секцию информации с информационных входов 16.

При отсутствии блокирующего сигнала или после его окончания на управляющем входе выходного коммутатора на информационные выходы 18 выдается информация из выбираемой секции памяти, которая определяется дешифратором 7 выбираемой секции, подающего сигнал на один из управляющих входов 19 выходных коммутаторов 9.

Для синхронизации записи информации один из входов схем «И 14 соединен с шиной 20 «Запись.

Дешифратор б сигналов управления построен так, что для всех адресных, коммутаторов, соответствующих тем секциям la fяти, номера которых меныме, чем кол, содержащийся в младшей части 3 адресного регистра 1, формируется управляющий сигнал для передачи адреса, поступающего с выхода преобразователя 4 -кода адреса, а для остальных адресных коммутаторов - управляющий сигнал для передачи кода адреса из старшей части 2 адресного регистра 1.

Устройство работает следующим образом.

Адресный регистр 1 принимает с входных тин 10 адрес очередного обращения, который можно представить в видеAn-f а,

S где а - содержимое младших разрядов адреса, указывающее на номер секции памяти, соответствующей данному адресу, 0. а -1; А - содержимое старищх ра; рядов адреса, указывающее на номер ячейки в выбранной секции памяти.

Преобразователь 4 кода адреса формирует величину А-И. Величина «а, содержащаяся в младшей части 3 регистра J, расшифровывается дещифратором 6 таким образом, что коммутаторы 5 передают на адресные входы секций памяти, номера кото. рых больше или равны «а, величину А, а на адресные входы остальных секций - величину А+1. Обращение производится постоянно ко всем секциям памяти. В результате 3 секции с номером «а выбирается

0 ячейка с адресом AU + а,..., в секции с номером п-1 - ячейка с адресом , в секции с номером О - ячейка с адресом п, в секции с номером а-1 - ячейка с адресом а + п-I, иначе говоря,

„ одновременно выбирается п последовательных ячеек, начиная с ячейки с адресом АЛ + а. Если в результате данного обращения сменился код на адресных входах секции памяти, в которой находится ячейка памяти Ajj-f а, то информация появится на информационных входах выходного коммутатора 9 через время выборки из секции памяти, поэтому формирователи 8 признаков готовности информации, начиная с момента смены кода адреса на адресных входах секций памяти, формируют сигналы,

поступающие на один из управляющих входов KOMMyTtiTopa 9, задерживающие выдачу информации из секции на время, равное времени выборки из секций. В связи с тем, что для большинства вычислительных процессов

д характерна большая вероятность обращений по последовательным и близкорасположенным адресам различных видов памяти (буферной, управляющей, оперативной), то большой процент (например, в некоторых типах управляющей, буферной памяти до

5 100%) приходится на такие обращения; когда код на адресных входах выбранной секции не изменяется при приеме обращения и информация выдается из памяти через время значительно меньшее времени выборки из секции. Эффективное значение цикла памяти, таким образом, может быть уменьшено в п раз по сравнению с циклом секции памяти. Для того чтобы организовать такой маесив опрашиваемых ячеек, когда выбранная ячейка является последней из этого массива, необходимо выполнить преобразователь кода 4 так. чтобы он уменьшал на единицу код со старшей части 2 регистра 1. Дешифратор 6 должен управлять коммутаторами 5 таким образом, .чтобы они передавали в секцию памяти код с преобразователя кода 4 в том случае, если номер секции больше номера выбранной секции. Если выбранная ячейка должна находиться в середине массива опра ииваемых ячеек, то необходимы два преобразователя кодов; уменьшающего и увеличиваюшего на i значения кода со старшей части регистра I. Необходимо также введение в коммутаторах 5 дополнительных информационных входов, соединенных со вторым преобразователем кодов, и дополнительных управляющих входов, соединенных с дополнительными выходами дешифратора 6, Формула изобретения Устройство для управления блоками памяти, содержащее адресный регистр, вы.ходы старших разрядов которого соединены со входами преобразователя кода адреса и входами адресных коммутаторов, а выходы младших разрядов подключены к входам дешифратора, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит формирова.тели признака готовности и выходные коммутаторы, управляющие входы которых соединены с соответствующими выходами дешифратора и формирователей признака готовностн, входы которых подключены к выходам адресных коммутаторов. Источники информации, принятые во внимание при экспертизе: i. Авторское свидетельство СССР № 297070, кл. Q II С 9/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1971 |

|

SU297070A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство контроля процесса бурения нефтяных и газовых скважин | 1986 |

|

SU1416943A1 |

Авторы

Даты

1978-12-05—Публикация

1976-07-14—Подача