fB(t},fB

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой фазовый детектор | 1980 |

|

SU1352615A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1990 |

|

SU1755360A1 |

| Устройство фазовой подстройки частоты | 1982 |

|

SU1251322A1 |

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

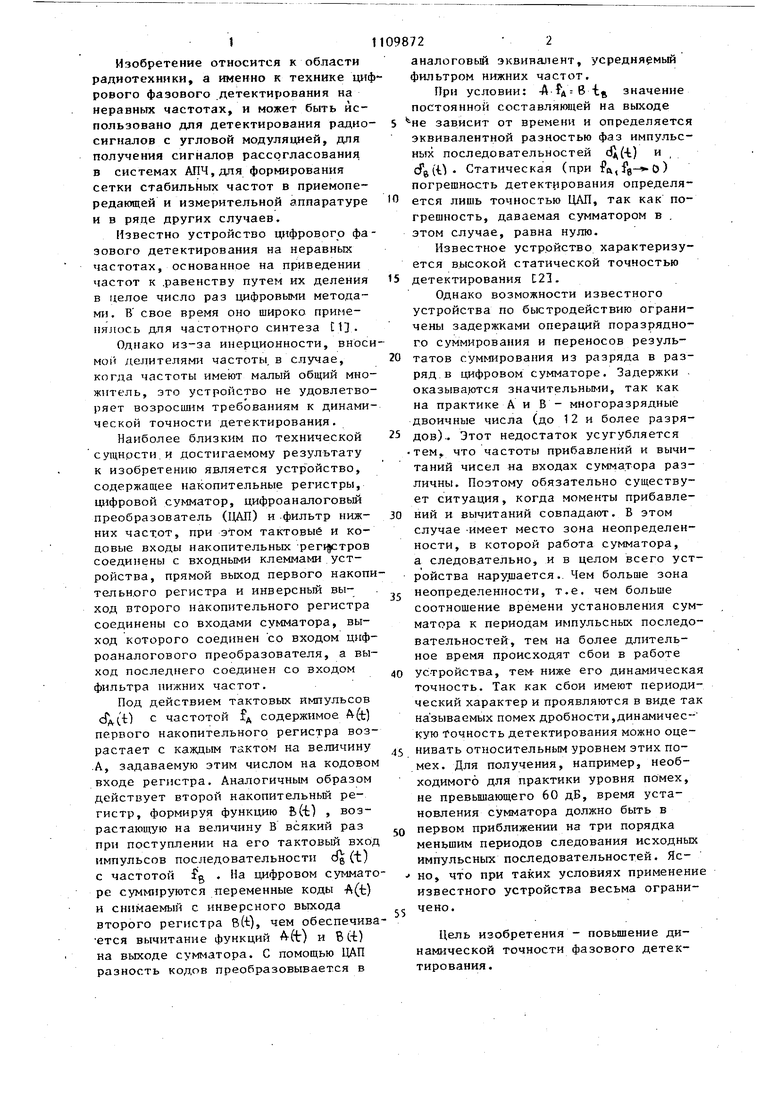

УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ФАЗОВОГО ДЕТЕКТИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ НА НЕРАВНЫХ ЧАСТОТАХ, содержащее накопительный регистр, кодовый вход которого соединен с кодовой входной клеммой, а тактовый вход - клеммой первой импульсной последовательности, и последовательно соединенные дифроаналоговьй преобразователь и фильтр нижних частот, отличающееся тем, что, с целью повьпиения динамической точности детектпропания, в него введен триггер, один из входов которого ссэрдинен с клеммой второй импульсной последовательности, другой вход - с выходом импульсов переполнения накопительного регистра, а выход - с входом старшего разряда 1щфроаналогового преобразователя, остальные входы которого поразрядно соединены с кодовым вгпходсм накопительного регистра.

Фиг.1

1

Изобретение относится к области радиотехники, а именно к технике цифрового фазового детектирования на неравных частотах, и может быть использовано для детектирования радиосигналов с угловой модуляцией, для получения сигналов рассогласования в системах АПЧ, для формирования сетки стабильных частот в приемопередающей и измерительной аппаратуре и в ряде других случаев.

Известно устройство цифрового фаэово.го детектирования на неравных частотах, основанное на приведении частот к .равенству путем их деления в целое число раз цифpoвы m методами. В свое время оно широко применялось Д.ПЯ частотного синтеза 1.

Однако из-за инерционности, вносиMoii делителями частоты, в случае, когда частоты имеют малый общий множитель, это устройство не удовлетворяет возросшим требованиям к динамической точности детектирования.

Наиболее близким по технической сущности.и достигаемому результату к изобретению является устройство, содержащее накопительные регистры, цифровой сумматор, цифроаналоговый преобразователь (ЦДЛ) и фильтр нижних частот, при этом тактовые и кодовые входы накопительных соединены с входными клеммами устройства, прямой выход первого накопительного регистра и инверсный выход второго накопительного регистра соединены со входами сумматора, выход которого соединен со входом цифроаналогового преобразователя, а выход последнего соединен со входом фильтра нижних частот.

Под действием тактовых импульсов ) с частотой д содержимое A(-t) первого накопительного регистра возрастает с каждым тактом на величину .А, задаваемую этим числом на кодовом входе регистра. Аналогичным образом действует второй накопительньп регистр, формируя функцию B(-t) , возрастающую на величину В всякий раз при поступлении на его тактовый вход импульсов последовательности cJg (t) с частотой fg . На цифровом сумматоре суммируются переменные коды A(t) и снимаемый с инверсного выхода второго регистра Blt), чем обеспечивается вычитание функций A-(-t) и В (-t) на выходе сумматора. С помощью ЦАП разность кодов преобразовывается в

9872 2

аналоговьй эквивалент, усредняемый фильтром нижних частот.

При условии: 4 значение постоянной составляюп1ей на выходе 5 не зависит от времени и определяется эквивалентной разностью фаз импульсных последовательностей d)(-t) и , cTglO- Статическая (при fa,) погрешность детектирования определя0 ется лишь точностью ЦАП, так как погрешность, даваемая сумматором в . этом случае, равна нулю.

Известное устройство характеризуется высокой статической точностью

5 детектирования 121.

Однако возможности известного устройства по быстродействию ограничены задержками операций поразрядного суммирования и переносов резуль20 татов суммирования из разряда в разряд в цифровом сумматоре. Задержки . оказываются значительными, так как на практике А и В - многоразрядные двоичные числа (до 12 и более разря5 дов).. Этот недостаток усугубляется тем, что частоты прибавлений и вычитаний чисел на входах сумматора различны. Поэтому обязательно существует ситуация, когда моменты прибавле0 НИИ и вычитаний совпадают. Б этом случае -имеет место зона неопределенности, в которой работа сумматора, а следовательно, и в целом всего устройства нару,шается.. Чем больше зона

J5 неопределенности, т.е. чем больше

соотношение времени установления сумматора к периодам импульсных последовательностей, тем на более длительное время происходят сбои в работе

0 ус тройства, тем- ниже его динамическая точность. Так как сбои имеют периодический характер и проявляются в виде так называемых помех дробности,динамичесКУЮ Точность детектирования можно оце5 нивать относительным уровнем этих помех. Для получения, например, необходимого для практики уровня помех, не превьшающего 60 дБ, время установления сумматора должно быть в

0 первом приближении на три порядка меньшим периодов следования исходных импульсных последовательностей. Яс но, что при таких условиях применение известного устройства весьма ограничено.

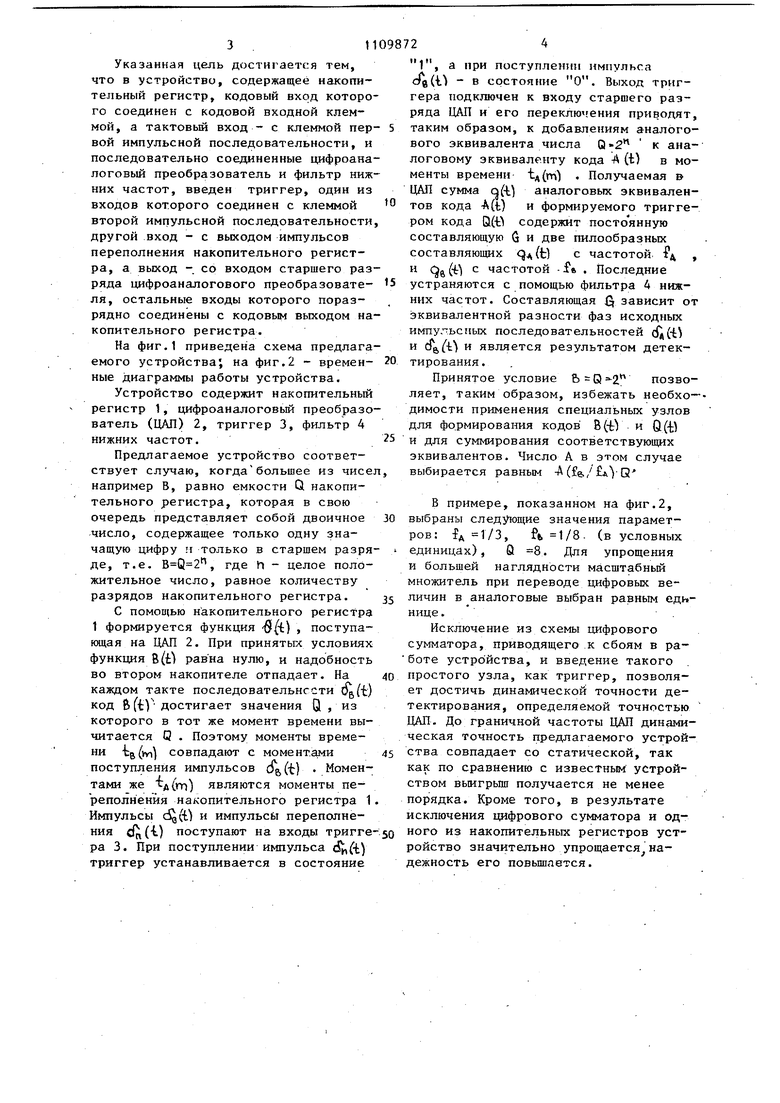

Цель изобретения - повышение динамической точности фазового детектирования. Указанная цель достигается тем, что в устройство, содержащее накопительный регистр, кодовый вход которого соединен с кодовой входной клеммой, а тактовый вход - с клеммой первой импульсной последовательности, и последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, введен триггер, один из входов которого соединен с клеммой второй импульсной последовательности, другой вход - с выходом импульсов переполнения накопительного регистра, а выход -. со входом старшего разряда цифроаналогового преобразователя, остальные входы которого поразрядно соединены с кодовым выходом накопительного регистра. На фиг.1 приведена схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройства. Устройство содержит накопительный регистр 1, цифроаналоговый преобразователь (ЦАП) 2, триггер 3, фильтр 4 нижних частот. Предлагаемое устройство соответствует случаю, когдабольшее из чисел например В, равно емкости Q накопительного регистра, которая в свою очередь представляет собой двоичное число, содержащее только одну значащую цифру п только в старшем разряде, т.е. , где h - целое положительное число, равное количеству разрядов накопительного регистра. С помоп(ью накопительного регистра 1 формируется функция ) поступающая на ЦАП 2. При принятых условиях функция B(t) равна нулю, и надобность во втором накопителе отпадает. На каждом такте последовательности Og,(t) код 6 ft) достигает значения Q , из которого в тот же момент времени вычитается Q . Поэтому моменты времени (hi совпадают с моментами поступления импульсов (t) Моментами же (01) являются моменты переполнения накопительного регистра 1 Импульсы и импульсы переполнения cfn(t) поступают на входы триггера 3. При поступлении импульса cSt,ft) триггер устанавливается в состояние 11 24 1, а при поступлении импульса cfe(i) в состояние О. Выход триггера подключен к входу старшего разряда ЦАП и его переключения приводят, таким образом, к добавлениям аналогового эквивалента числа Q-2 к аналоговому эквиваленту кода (t) в моменты времени 1д(т) . Получаемая в ЦАП сумма Q( аналоговых эквивалентов кода -A(t) и формируемого триггером кода El(t содержит постоянную составляющую G и две пилообразных составляющих cjv (t) с частотой f и Qj (-tl с частотой - f . Последние устраняются с помощью фильтра 4 нижних частот. Составляющая Q зависит от :эквивапентной разности фаз исходных импульсных последовательностей d(-t и и является результатом детектирования. Принятое условие позволяет, таким образом, избежать необходимости применения специальных узлов для формирования кодов 8(-tV и Q(-|;) и для суммирования соответствуюшзих эквивалентов. Число А в этом случае выбирается равным -А (fe, В примере, показанном на фиг.2, выбраны следующие значения параметров: IA 1/3, fb 1/8. (в условных единицах), Q 8. Для упрощения и большей наглядности масштабный множитель при переводе цифровых величин в аналоговые выбран равным единице.. Исключение из схемы цифрового сумматора, приводящего к сбоям в работе устройства, и введение такого простого узла, как триггер, позволяет достичь динамической точности детектирования, определяемой точностью ЦАП. До граничной частоты ЦАП динамическая точность предлагаемого устройства совпадает со статической, так как по сравнению с известным устройством вьигрыш получается не менее порядка. Кроме того, в результате исключения цифрового сумматора и одного из накопительных регистров устройство значительно упрощается надежность его повьш1лется.

fA(i)

AW

fM

B(t) Q(t)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПОДАЧИ КОМПОНЕНТОВ ТОПЛИВА В КАМЕРУ ТРЕХКОМПОНЕНТНОГО ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ | 2012 |

|

RU2490500C1 |

| Катодное реле | 1921 |

|

SU250A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3913028, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1984-08-23—Публикация

1981-12-05—Подача