(5А) ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

1

Изобретение относится к радиотехнике и может быть использовано для детектирования радиосигналов с угло вой модуляцией, получения сигналов рассогласования в системах АПЧ, формировании сетки стабильных частот в приемопередающей и измерительной аппаратуре и в ряде других случаев.

Известно устройство цифрового фазового детектирования на неравных частотах, основанное на приведении частот к равенству путем их деления в целое число раз с помощью цифрового делителя частоты с переменным коэффициентом деления f 1 3Недостатком этого устройства является инерционность, вносима.я делителями частоты в случае, когда частоты некратны и имеют малый общий множитель.

Наиболее близким по технической сущности и достигаемому результату является устройство для приведения частоты к равенству, которое снабжено делителем частоты с переменным коэффициентом деления, состоящим из делителя частоты а целое число раз и накопительного регистра, осуществляющего изменение на единицу коэффициента деления Делителя частоты 21.В результате работы делителя из О циклов деления раз будет установлен коэффициент деления и (Q-a) раз коэффициента деления NO, при этом средний коэффициент деления (N) равен

tNo-)(Q-o)

Nгде N - коэффициент деления частоты, представляющий собой, например, десятичную дробь;

N - целая часть коэффициента деления,

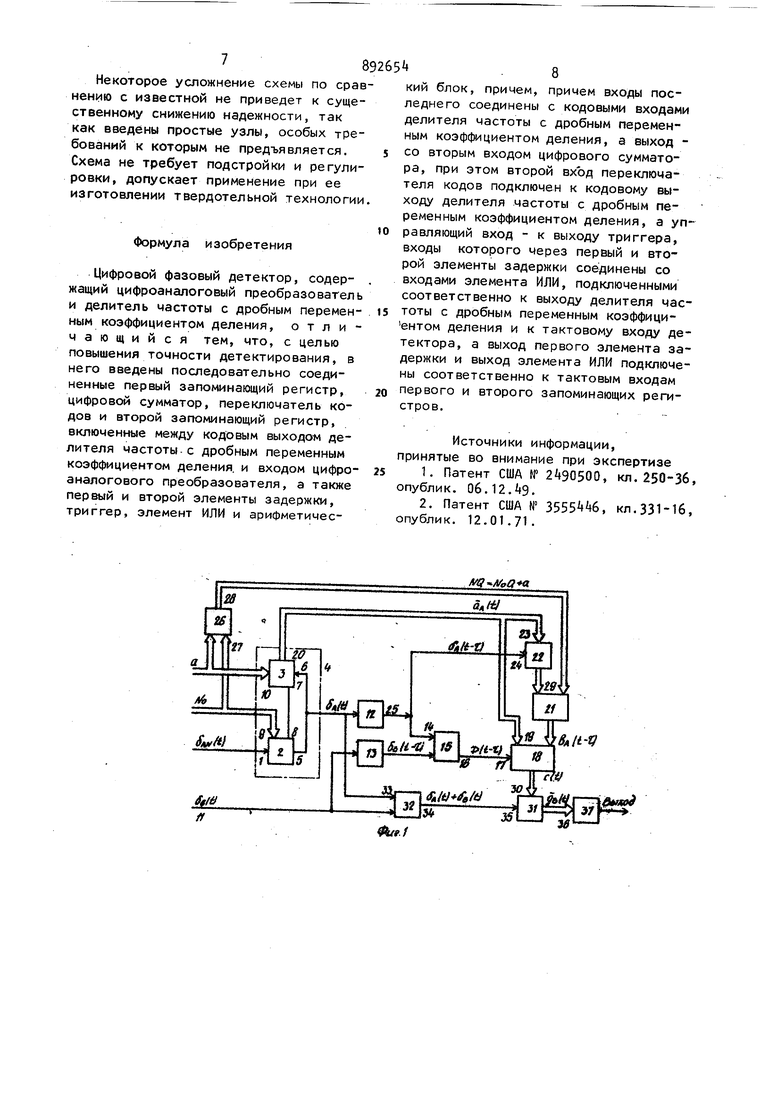

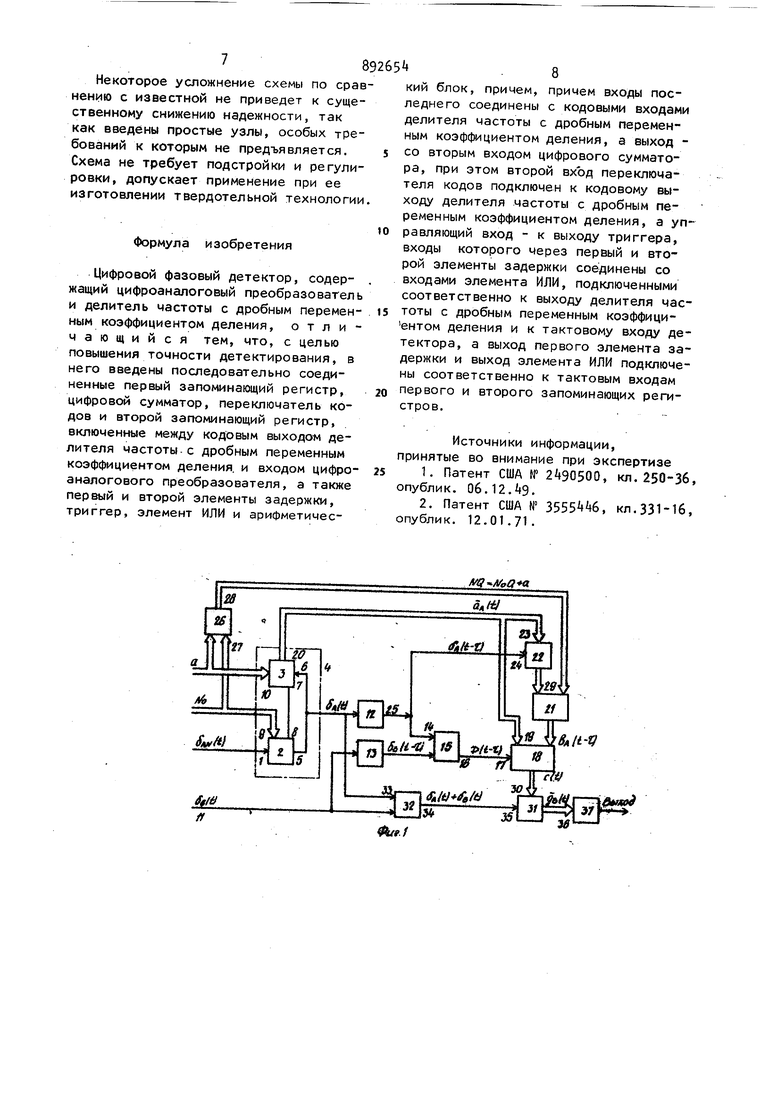

а - число, на которое возрастает срдержимое накопительного регистра с каждым тактом другой импульсной последовательности с меньшей частотой. 3 В результате деления частоты средние значения частот будут равными, но мгновенные значения частот будут различаться. Различие частот приводит к возникновению помехи дробности, которая снижает точность цифрового фазово го детектора. Для компенсации помехи дробности переменный код, снимаемый с накопительного регистра, преобразовывается в аналоговую форму и затем в суммирующем устройстве складывается с выходным сигналом фазового детектора. Точность компенсации помехи дробности, т.е. точность цифрового фазового детектирования, обеспечиваемая известным устройством, определяется точностью установки и стабильностью коэффициентов, передавая ФД, ЦАП и весовые коэффициенты при суммироваНИИ, поддержание которых на высоком уровне связано с известными трудностями. На практике не удается достичь устойчивой компенсации помех дробности до уровня ниже 0 дБ, что чаше все го оказывается недостаточным. К тому же, указанная величина ослабления помех достигается за счет тщательной настройки и регулировки соответствующих узлов схемы, что снижает экономические показатели при производст ве. Цель изобретения - повышение точности цифрового фазового детектирова ния . 1 Поставленная цель достигается тем что в известный цифровой фазовый детектор, содержащий цифроаналоговый преобразователь и делитель частоты с дробным переменным коэффициентом деления, введены последовательно соеди ненные первый запоминающий регистр, цифровой сумматор, переключатель кодов и второй запоминающий регистр, включенные между кодовым выходом дел теля частоты с дробным переменным ко эффициентом деления и входом цифроаналогового преобразователя, а также первый и второй элементы задержки, триггер, элемент ИЛИ и арифметический блок, причем входы последнего соединены с кодовыми входами делителя частоты с дробным переменным коэф фициентом деления, а выход - со вторым входом цифрового сумматора, при этом второй вход переключателя кодов подключен к кодовому выходу делителя частоты с дробным переменным коэффи) циентом деления, а управляющий вход к выходу триггера, входы которого через первый и второй элементы задержки соединены со входами элемента ИЛИ, подключенными соответственно к выходу делителя частоты с дробным переменным коэффициентом деления, соединенному с тактовым входом детектора, а выход первого элемента задержки и выход элемента ИЛИ подключены соответственно к тактовым входам первого и второго запоминающих регистров. На фиг. 1 показана структурная схема цифрового фазового детектора; на фиг, 2 - временные диаграммы работы устройства. Устройство содержит тактовый вход 1 делителя частоты (ДЧ), делитель 2 частоты в целое число раз, накопительный регистр 3 (НР) , делитель 1 частоты с дробным переменным коэффициентом деления (ДПКД), выход 5 ДЧ, тактовый вход 6 HP, выход 7 импульсов переполнения HP, управляющий вход 8 ДЧ для изменения его коэффициента деления на единицу, кодовый вход 9 ДЧ для задания целочисленной части N коэффициента деления, кодовый вход 10 HP для задания дробной части а коэффициента N, тактовый вход 11 устройства для импульсной последовательности с меньшей частотой, первый 12 и второй 13 элементы задержки, входы триггера, триггер 15, выход 16 триггера, управляющий вход 17 переключателя кодов, переключатель 18 кодов, кодовые входы 19 переключателя кодов, кодовый выход 20 HP, цифровой сумматор 21, первый запоминающий регистр 22, кодовый вход 23 первого запоминающего регистра, тактовый вход 2k первого запоминающего регистра, выход 25 первого элемента задержки, арифметический блок 26, входы 27 арифметического блока, выход 28 арифметического блока, входы 29 цифрового сумматора, кодовый вход 30 второго запоминающего регистра, второй запоминающий регистр 31, элемент ИЛИ 32, входы 33 элемента ИЛИ, выход 3 элемента ИЛИ, тактовый вход 35 второго запоминающего регистра, вход 36 цифроаналогового преобразователя (ЦАП) ЦАП 37. Одна из импульсных последовательностей (Гд (t) с большей частотой Гд, как и в известном устройстве, поступает на тактовый вход 1 делителя 2 частоты совместно с накопительным ре гистром 3, образующим делитель k час тоты с дробным переменным коэффициен том деления (ДПКД). Импульсы с выхо да 5 делителя 2 поступают на тактовы вход 6 регистра 3. а выход 7 импульсов переполнения регистра связан с управляющим входом 8 делителя частоты для изменения его коэффициента де ления на единицу. Целочисленная HQ и дробная а части коэффициента деления N задаются этими числами соответ ственно на кодовых входах 9 и 10 делителя и регистра. При переполнении регистра коэффициент деления делителя вместо NQ принимает значение на время одного цикла деления. В результате чередования целочисленных коэффициентов NQ и получают дро ный (в среднем) коэффициент N Np+a/Q где Q - емкость накопительного регистра. Импульсные последовательности dA(t), полученные в результате деления частоты rfe (t) меньшей ча тотой fg и поступающие на вход 11 ус .ройства, через элементы 12 и 13 задержки с постоянными времени JT возде ствуют на входы Н триггера 15. Сигнал D(f) с выхода 16 триггера посту пает на управляющий вход 17 переключателя 18 кодов, на один из кодовых входов 19 которого поступает код ад(1), снимаемый с инверсных выходов 20 накопительного регистра 3, а на другой код Бд(1-С)ад(1-Г)+ NQ, полу ченный в результате суммирования в цифровом сумматоре 21 постоянного чи ла NQ с переменным кодом ад (1-г), снимаемым с первого запоминающего регистра 22, подключенного кодовым входом 23 к выходу 20 регистра 3. Регистр 22 тактируется импульсами (rft(t-Tr), для чего его тактовый вход 2 подключается к выходу 25 первого элемента 12 задержки. Для получения кода NQ NoQ+a служит арифметический блок 26. На его входы 27 поступают исходные числа N и а, а результирующее число с его выхода 28 передается на один из входов 29 цифрового сумматора 21. Полярность подключения управляющего входа 17 переключателя кодов 18 выбирается такой. чтобы на его выход передавался код Ьд(1-т) с момента по ступления очередного импульса последовательности (t-T) до момента поступления очередного импульса последовательности сГд ) на входы 1 4 триггера 15- На остальных интервалах времени на выход переключателя передается код a(t-Tr). На кодовом входе 30 второго запоминающего регистра 31 присутствует таким образом код c(t)raд(t-c)+NQЗD(t-r)+aд(t-C)-D(t-r), Второй запоминающий регистр 31 тактируется суммарной импульсной последовательностью (f(t)+cf(t), получае мой с помощью элемента ИЛИ 32. Для этого входы 33 элемента ИЛИ соединены со входами элементов задержек, а ее выход 3 подключен к тактовому входу 35 упомянутого регистра. Выходной код ) регистра 31 поступает на вход 36 ЦАП 37 и преобразовывается в аналоговый эквивалент. Площадь под функцией ) на интервале времени, равном периоду Tjj импульсной последовательности (t) на любом участке функции, остается постоянной. Объясняется это тем, что приращения площади за счет изменений периода Т/, равные Сд-д)Тв компенсируются смещением функции ) по оси кодов на величину, ределяемую функцией 30(t). Помеха п.. дробности таким образом полностью исключается. Аналоговая величина, соответствующая постоянной составляющей (з-о кода g(t), является результатом цифрового фазового детектирования и выделяется далее известными методами путем фильтрации гармоник частоты f. Как видно из фиг. 2, переходные процессы в цифровых схемах, предшествующих второму запо1 нающему регистру, не влияют на вид функции gg(t). На фиг. 2 эт отражено участками функций O(t-P), ) и с (t), показанными пунктиром. Постоянная времени ТГ должна равняться или превышать время записи числа в регистр 31. Точность компенсации помех дробности, т.е. точность цифрового фазового детектирования, в предлагаемом устройстве определяется лишь точностью ЦАП. Учитывая высокую точность последних (десятиразрядный ЦАП, например, имеет погрешность, не превышающую 10) можно заключить, что выигрыш, даваемый предлагаемым устройством по сравнению с известным, составит величину не менее порядка. Некоторое усложнение схемы по срав нению с известной не приведет к существенному снижению надежности, так как введены простые узлы, особых требований к которым не предъявляется. Схема не требует подстройки и регулировки, допускает применение при ее изготовлении твердотельной технологии Формула изобретения Цифровой фазовый детектор, содержащий цифроаиапоговый преобразовател и делитель частоты с дробным перемен ным коэффициентом деления, отли чающийся тем, что, с целью повышения точности детектирования, в него введены последовательно соединенные первый запоминающий регистр, цифровой сумматор, переключатель кодов и второй запоминающий регистр, включенные между кодовым выходом делителя частоты с дробным переменным коэффициентом деления, и входом цифро аналогового преобразователя, а также первый и второй элементы задержки, триггер, элемент ИЛИ и арифметичес/ /H jg g

i

/г/ кий блок, причем, причем входы последнего соединены с кодовыми входами делителя частоты с дробным переменным коэффициентом деления, а выход со вторым входом цифрового сумматора, при этом второй вход переключателя кодов подключен к кодовому выходу делителя частоты с дробным переменным коэффициентом деления, а управляющий вход - к выходу триггера, входы которого через первый и второй элементы задержки соединены со входами элемента ИЛИ, подключенными соответственно к выходу делителя частоты с дробным переменным коэффициентом деления и к тактовому входу детектора, а выход первого элемента задержки и выход элемента ИЛИ подключены соответственно к тактовым входам первого и второго запоминающих регистров. Источники информации, принятые во внимание при экспертизе 1. Патент США № 2 90500, кл, 250-36, опублик. Об.12.9. 2. Патент США № , кл.ЗЗЫб, опублик. 12.01.71.

Авторы

Даты

1981-12-23—Публикация

1980-04-18—Подача