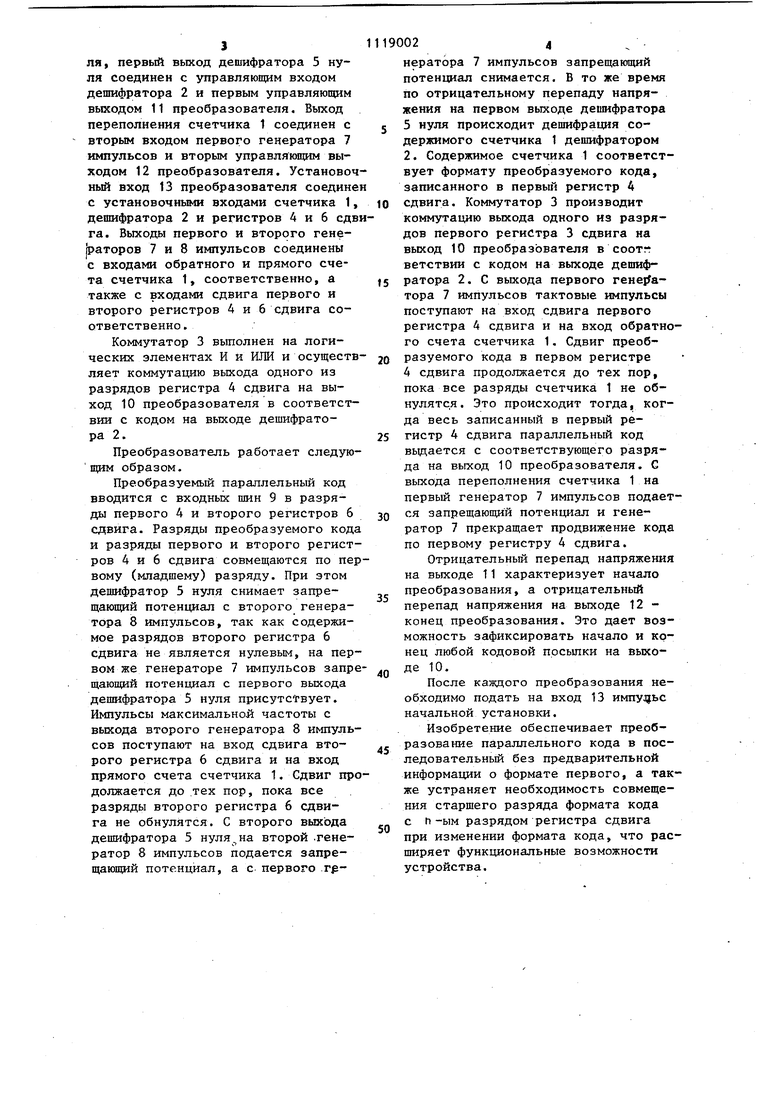

1 . Изобретение относится к импульс ной технике и может найти применение в системах передачи данных по цифровым каналам с преобразованием параллельного кода в последовательный. Известен преобразователь параллельного кода в последовательный, содержащий регистр сдвига, дешифратор нуля, выходы которого соединены с выходами разрядов регистра сдвига, за исключением старшего, генератор импульсов, управляющий вход которого соединен с выходом дешифратора нуля, а выход генерато ра импульсов соединен с входом сдвига, выход старшего разряда регистра сдвига соединен с информационным выходом преобразователя L Недостаток данного преобразоват ля состоит в невозможности преобра зования чисел с различными форматами (различным числом разрядов). Наиболее близким к изобретению является преобразователь параллель ного кода в последовательный, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствуннцими входными шинами первый генератор импульсов, выход которого соединен с входом сдвига первого регистра сдвига,, дешифратор нуля, первый выход которого со динен с первым входом первого гене ратора импульсов, а входы с выхода ми разрядов регистра сдвига, и ком татор, выходы которого соединены с соответствующими разрядами регистр сдвига Г 2 3. Недостатками известного преобра зователя являются сложность записи в регистр сдвига кода при изменени его формата (т.е. сложность совмещения старшего разряда формата код с ti-ым разрядом регистра сдвига п изменении первого), необходимость предварительной информации о форма те преобразуемого кода. Цель изобретения - расширение, функциональных возможностей преобразователя. Поставленная цель достигается тем, что в преобразователь параллел ного кода в последовательный, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами первый генератор импульсов, выход к 022 торого соединен с входом сдвига первого регистра сдвига, дешифратор нуля, первьпЧ выход которого соединен с первым входом первого генератора импульсов, и коммутатор введены счетчик, дешифратор, второй генератор импульсов и второй регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, а выходы - с входами дешифратора нуля, первый вьпсод которого подключен к первому управляющему выходу преобразователя и управляющему входу дешифратора, а второй выход соединен с входом второго генератора импульсов, выход которого соединен с входом сдвига второго регистра сдвига и входом прямого счета счетчика, вход обратного счета которого соединен с выходом первого генератора импульсов, при этом выход переполнения счетчика подключен к второму входу первого генератора импульсов и второму управляющему выходу преобразователя, а выходы разрядов счетчика соединены с входами дешифратора, выходы которого соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами разрядов первого регистра сдвига, кроме выхода младшего разряда, а выход коммутатора соединен с вькодом преобразователя, кроме того, установочные входы первого и второго регистров сдвига, счетчика и дешифратора подключены к установочному входу преобразователя. На чертеже приведена блок-схема преобразователя. Выходы разрядов счетчика 1 соединены с входами дешифратора 2, выхо- . ды которого соединены с управляющими входами коммутатора 3. Информационные входы последнего соединены с выходами разрядов первого регистра 4 сдвига, кроме младшего разряда. Входы дешифратора 5 нуля соединены с выходами разрядов второго регистра 6 сдвига. Первьй вход первого генератора 7 импульсов и вход.втог рого генератора 8 импульсов соединены соответственно с первым и вторым выходами дешифратора 5 нуля. Входы разрядов регистров 4 и 6 сдвига соединены с соответствующими входными шинами 9, выход коммутатора 3 соединен с выходом 10 преобразовате 3 ля, первый выход дешифратора 5 нуля соединен с управляющим входом дешифратора 2 и первым управляющим выходом 11 преобразователя. Выход переполнения счетчика 1 соединен с вторым входом первого генератора 7 импульсов и вторым управляющим выходом 12 преобразователя. Установо ный вход 13 преобразователя соедин с установочными входами счетчика 1 дешифратора 2 и регистров 4 и 6 сд га. Выходы первого и второго гене раторов 7 и 8 импульсов соединены с входами обратного и прямого счета счетчика 1, соответственно, а также с входами сдвига первого и второго регистров А и 6 сдвига соответственно. Коммутатор 3 выполнен на логических элементах И и ИЛИ и осущест ляет коммутацию выхода одного из разрядов регистра 4 сдвига на выход 10 преобразователя в соответст вии с кодом на выходе дешифратора 2. Преобразователь работает следую щим образом. Преобразуемый параллельный код вводится с входных шин 9 в разряды первого 4 и второго регистров 6 сдвига. Разряды преобразуемого код и разряды первого и второго регист ров 4 и 6 сдвига совмещаются по пе вому (младшему) разряду. При этом дешифратор 5 нуля снимает запрещающий потенциал с второго генератора 8 импульсов, так как содержимое разрядов второго регистра 6 сдвига не является нулевым, на пер вом же генераторе 7 импульсов запр щающий потенциал с первого выхода дешифратора 5 нуля присутствует. Импульсы максимальной частоты с выхода второго генератора 8 импуль сов поступают на вход сдвига второго регистра 6 сдвига и на вход прямого счета счетчика 1. Сдвиг пр должается до .тех пор, пока все разряды второго регистра 6 сдвига не обнулятся. С второго выхода дешифратора 5 нуля,на второй .генератор 8 импульсов подается запрещающий потенциал, а с первого т 024нератора 7 импульсов запрещающий потенциал снимается. В то же время по отрицательному перепаду напряжения на первом выходе дешифратора 5 нуля происходит дешифрация содержимого счетчика 1 дешифратором 2. Содержимое счетчика 1 соответствует формату преобразуемого кода, записанного в первьй регистр А сдвига. Коммутатор 3 производит коммутацию выхода одного из разрядов первого регистра 3 сдвига на выход 10 преобразователя в соответствии с кодом на выходе дешифратора 2. С выхода первого reaei aтора 7 импульсов тактовые импульсы поступают на вход сдвига первого регистра 4 сдвига и на вход обратного счета счетчика 1. Сдвиг преобразуемого кода в первом регистре 4 сдвига продолжается до тех пор, пока все разряды счетчика 1 не обнулятся . Это происходит тогда, когда весь записанный в первый регистр 4 сдвига параллельный код вьщается с соответствующего разряда на выход 10 преобразователя. С выхода переполнения счетчика 1 на первый генератор 7 импульсов подается запрещающий потенциал и генератор 7 прекращает продвижение кода по первому регистру 4 сдвига. Отрицательный перепад напряжения на выходе 11 характеризует начало преобразования, а отрицательный перепад напряжения на выходе 12 конец преобразования. Это дает возможность зафиксировать начало и конец любой кодовой посылки на выходе 10. После каждого преобразования необходимо подать на вход 13 импуд}ьс начальной установки. Изобретение обеспечивает преобразование параллельного кода в последовательный без предварительной информации о формате первого, а также устраняет необходимость совмещения старшего разряда формата кода с h-ым разрядом регистра сдвига при изменении формата кода, что расширяет функциональные возможности устройства.

1.

« ЛЧЖ

/IV Л Ч&.

с.

L

/IV /14 . /bf

PIMJJ-IJM li

/IV ЛЧ « ф ДЬм

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1159165A1 |

| Преобразователь параллельного кода в последовательный | 1988 |

|

SU1603529A2 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243098A1 |

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU860056A1 |

| Преобразователь кодов | 1986 |

|

SU1363480A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь комбинаторно-деся-ТичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU809566A1 |

| Преобразователь кодов | 1989 |

|

SU1619410A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ, содержащий первый регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, первый генератор импульсов, выход которого соединен с входом сдвига первого регистра сдвига, депмфратор нуля, первый вькод которого соединен с первым входом первого генератора импульсов, и коммзп-атор, о тлйчающийс я тем, что, с целью расширения функциональных возможностей, в него введены счетчик, ;дешифратор, второй генератор импульсов и второй регистр сдвига, входы разрядов которого соединены с соответствующими входными шинами, а выходы - с входами дешифратора нуля, первый выход которого подi ключен к первому управляющему выходу преобразователя и управляющему входу дешифратора, а второй выход соединен с входом второго генератора импульсов, выход которого соединен с входом сдвига второго регистра сдвига и входом прямого счета счетчика, вход обратного счета которого соединен с выходом первого генератора импульсов, при этом : выход переполнения счетчика подключен к второму входу первого генератора импульсов и второму управляющему выходу преобразователя, а выходы разрядов счетчика соединены с (Л входами дешифратора, выходы которого соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами разрядов первого регистра сдвига, кроме выхода младшего разряда, а выход коммутатора соединен с выходом преобразователя, кроме того, тановочные входы первого и второго О регистров сдвига, счетчика и дешифо кэ ратора подключены к установочному входу преобразователя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-04-15—Подача