t124

Изобретение относится к вычислиельной технике и может быть испольовано Б системах передачи и преобраования цифровых данных.

Цель изобретения - повышение бысродействия .

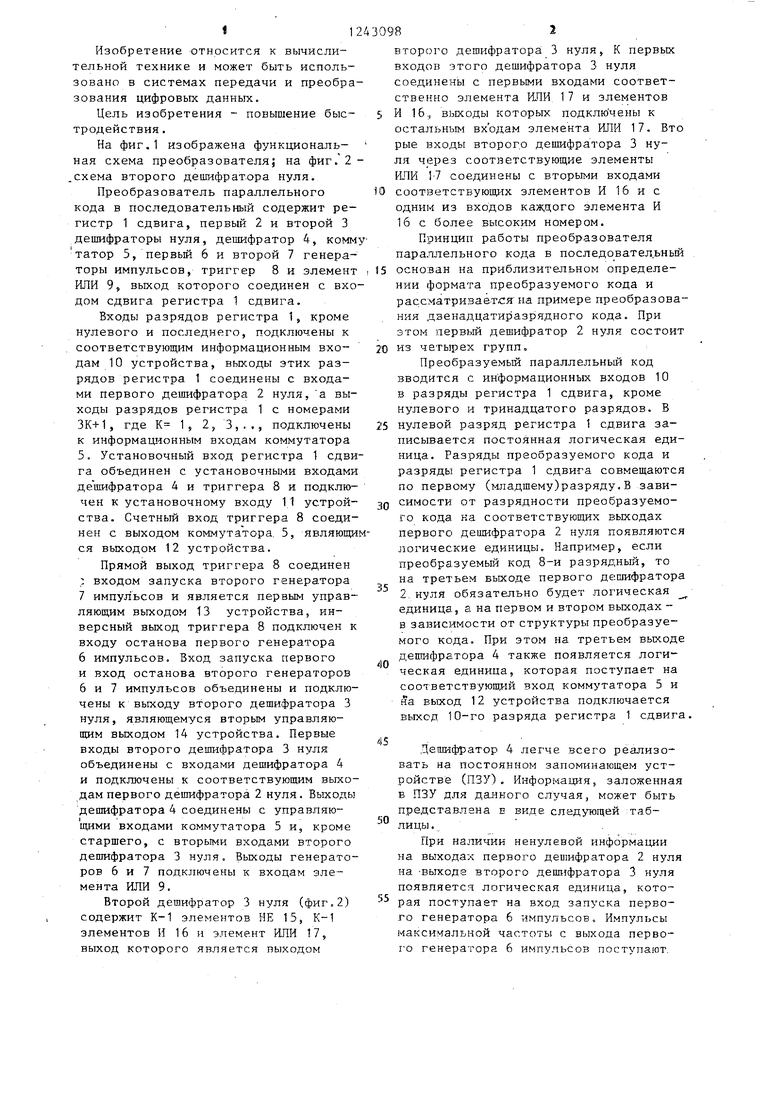

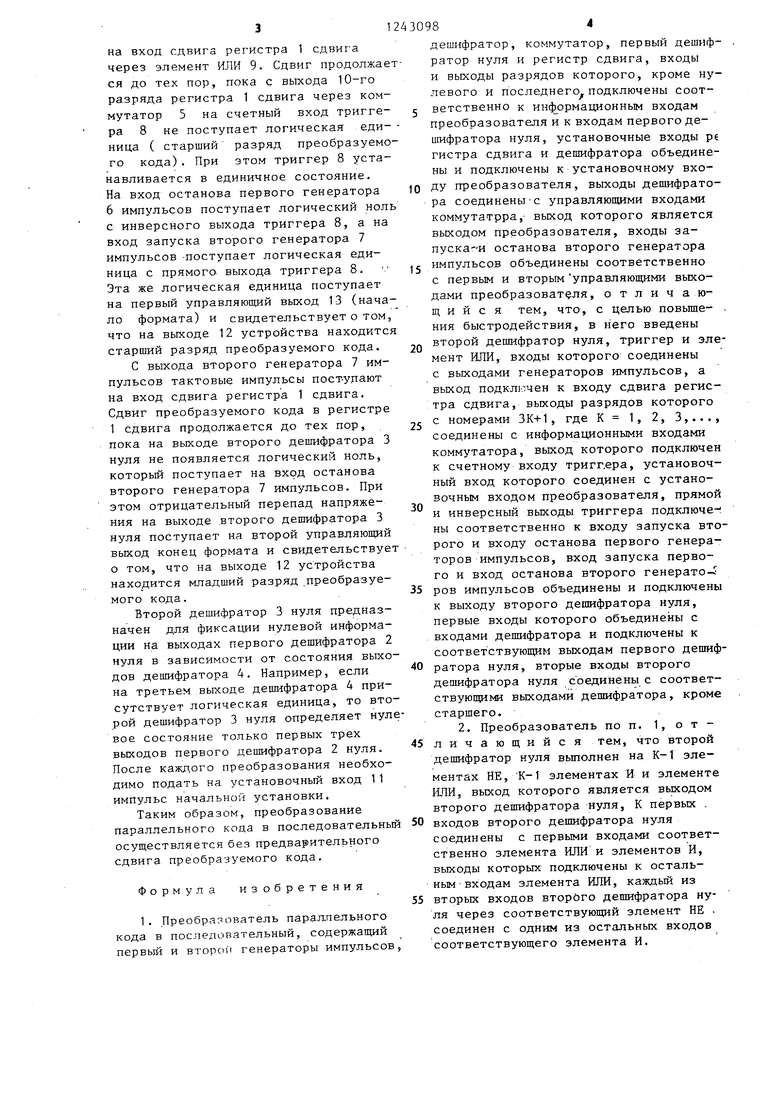

На фиг.1 изображена функциональая схема преобразователя; на фиг. 2 - схема второго дешифратора нуля.

Преобразователь параллельного кода в последовательный содержит регистр 1 сдвига, первый 2 и второй 3 дешифраторы нуля, дешифратор 4, коммутатор 5, первый 6 и второй 7 генераторы импульсов, триггер 8 и элемент i ИЛИ 9, выход которого соединен с входом сдвига регистра 1 сдвига.

Входы разрядов регистра 1, кроме нулевого и последнего, подключены к соответствующим информационным входам 10 устройства, выходы этих разрядов регистра 1 соединены с входами первого дешифратора 2 нуля, а выходы разрядов регистра 1 с номерами ЗК+1, где К 1, 2, 3,.., подключены к информационным входам коммутатора 5. Установочный вход регистра 1 сдвига объединен с установочными входами дешифратора 4 и триггера 8 и подключен к установочному входу 11 устройства. Счетный вход триггера 8 соединен с выходом коммутатора. 5, являющимся выходом 12 устройства.

Прямой выход триггера 8 соединен : входом запуска второго генератора 7 импульсов и является первым управляющим выходом 13 устройства, инверсный выход триггера 8 подключен к входу останова первого генератора 6 импульсов. Вход запуска первого и вход останова второго генераторов 6 и 7 импульсов объединены и подключены к выходу второго дешифратора 3 нуля, являющемуся вторым управляющим выходом 14 устройства. Первые входы второго дешифратора 3 нуля объединены с входами дешифратора 4 и подключены к соответствующим выходам первого дешифратора 2 нуля. Выходы дешифратора 4 соединены с управляю- входами коммутатора 5 и, кроме старшего, с вторыми входами второго депзифратора 3 нуля. Выходы генераторов 6 и 7 подключены к входам элемента ИЛИ 9,

Второй дешифратор 3 нуля (фиг,2) содержит К-1 элементов НЕ 15, К-1 элементов И 16 и элемент ИЛИ 17, выход которого является выходом

81

второго дешифратора; 3 нуля, К первых входов этого дешифратора 3 нуля соединены с первыми входами соответственно элемента ИЛИ 17 и элементов И 16,, выходы которых подключены к остальным вх одам элемента ИЛИ 17. Вто рые входы второго дешифратора 3 нуля через соответствующие элементы ИЛИ 1-7 соединены с вторьми входами соответствуюпщх элементов И 16 и с одним из входов каж,дого элемента И 16 с более высоким номером.

П ринцип работы преобразователя параллельного кода в последовател.ьный основан на приблизительном определении формата преобразуемого кода и рарсматривается на примере преобразования двенадцатиразрядного кода. При этом первый дешифратор 2 нуля состоит из четырех групп.

Преобразуемый параллельный код вводится с информационных входов 10 в разряды регистра 1 сдвига, кроме нулевого и тринадцатого разрядов. В нулевой разряд регистра 1 сдвига записывается постоянная логическая единица. Разряды преобразуемого кода и разряды регистра 1 сдвига совмещаются по первому (младшему)разряду.В зави- симости: от разрядности преобразуемого кода, на соответствующих выходах первого дешифратора 2 нуля появляются логические единицы. Например, если преобразуемый код 8-и разрядный, то на третьем выходе первого дешифратора 2, нуля обязательно будет логическая единица, а на первом и втором выходах - в зависимости от структуры преобразуемого кода. При этом на третьем выходе дешифратора 4 также появляется логическая единица, которая поступает на соответствуюш га вход коммутатора 5 и на выход 12 устройства подключается выход 10-го разряда регистра 1 сдвига.

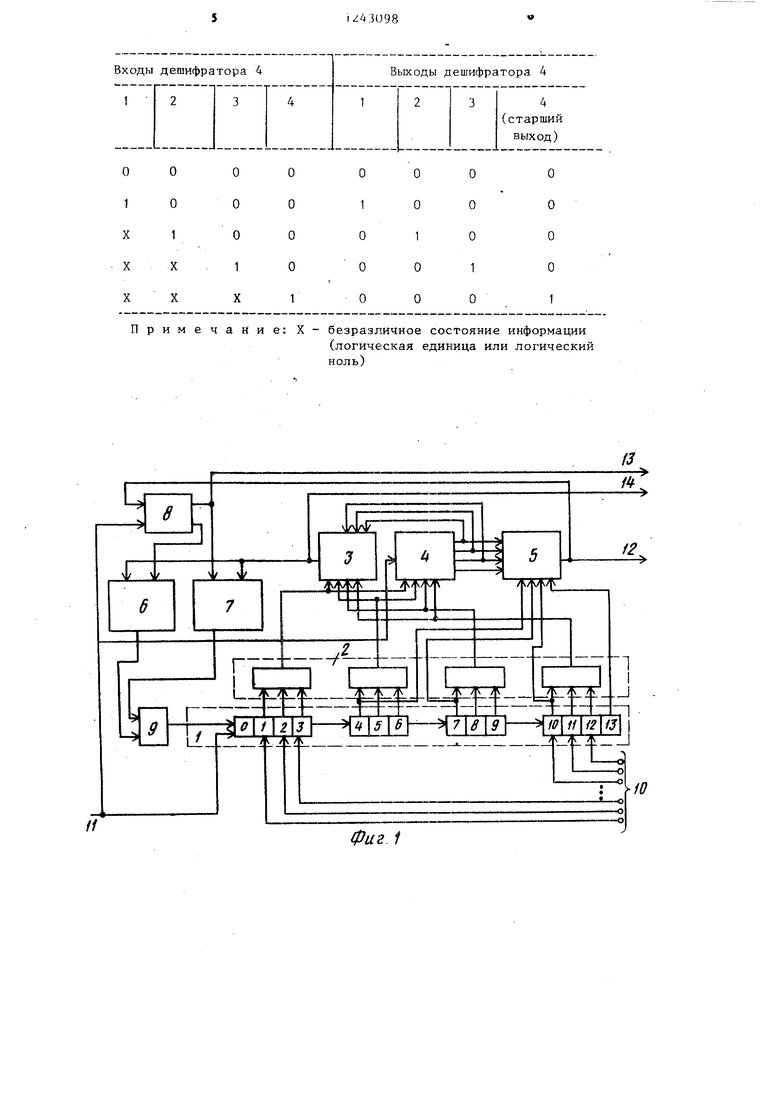

Дешифратор 4 легче всего реализовать на постоянном запоминающем устройстве (П,ЗУ) . Информация, заложенная в ПЗУ для далного случая, может быть представлена Е виде следующей таблицы.

При наличии ненулевой информации на выходах первого дешифратора 2 нуля на -выходе второго дешифратора 3 нуля появляется логическая единица, которая поступает на вход запуска первого генератора 6 импульсов. Импульсы максимальной частоты с выхода первого генератора 6 импульсов поступают.

на вход сдвига регистра 1 сдвига через элемент ИЛИ 9. Сдвиг продолжае ся до тех пор, пока с выхода разряда регистра 1 сдвига через коммутатор 5 на счетный вход триггера 8 не поступает логическая еди- ница ( старший разряд преобразуемого кода). При этом триггер 8 устанавливается в единичное состояние. На вход останова первого генератора 6 импульсов поступает логический нол с инверсного выхода триггера 8, а на вход запуска второго генератора 7 импульсов -поступает логическая единица с прямого выхода триггера 8. Эта же логическая единица поступает на первый управляющий выход 13 (начало формата) и свидетельствует о том, что на выходе 12 устройства находитс старший разряд преобразуемого кода.

С выхода второго генератора 7 импульсов тактовые импульсы поступают на вход сдвига регистра 1 сдвига. Сдвиг преобразуемого кода в регистре 1 сдвига продолжается до тех пор, пока на выходе второго дешифратора 3 нуля не появляется логический ноль, который поступает на вход останова второго генератора 7 импульсов. При этом отрицательный перепад напряжения на выходе .второго дешифратора 3 нуля поступает на второй управляющий выход конец формата и свидетельствует о том, что на выходе 12 устройства находится младший разряд преобразуемого кода.

Второй дешифратор 3 нуля предназначен для фиксации нулевой информации на выходах первого Дешифратора 2 нуля в зависимости от состояния выходов дешифратора 4. Например, если на третьем выходе дешифратора 4 присутствует логическая единица, то второй дешифратор 3 нуля определяет нулевое состояние только первых трёх выходов первого дешифратора 2 нуля. После каждого преобразования необходимо подать на установочный вход 11 импульс начальной установки.

Таким образом, преобразование параллельного кода в последовательный осуществляется без предварительного сдвига преобразуемого кода.

Формула изобретения

1 . Преобразователь парал.пельного кода в последовательный, содержащий первый и второй генераторы импульсов,

2430984

дешифратор, коммутатор, первый дешифратор нуля и регистр сдвига, входы и выходы разрядов которого, кроме нулевого и последнего, подключены соот- 5 ветственно к информационным входам преобразователя и к входам первого дешифратора нуля, установочные входы ре гистра сдвига и дешифратора объединены и подключены к установочному вхо- 10 ДУ преобразователя, выходы дешифратора соединены-с управляющими входами коммутатрра,- выход которого является выходом преобразователя, входы за- пуска-и останова второго генератора j импульсов объединены соответственно с первым и вторым управляющими выходами преобразователя, о т л и ч а ю- щ и и с я тем, что, с целью повыше- . ния быстродействия, в него введены 2Q второй дешифратор нуля, триггер и элемент ИЛИ, входы которого соединены с выходами генераторов импульсов, а выход подключен к входу сдвига регистра сдвига, выходы разрядов которого 25 с номерами ЗК+1, где К 1, 2, 3,..., соединены с информационными входами коммутатора, выход которого подключен к счетному входу триггера, установочный вход которого соединен с установочным входом преобразователя, прямой и инверсный выходы триггера подключены соответственно к входу запуска второго и входу останова первого генераторов импульсов, вход запуска первого и вход останова второго генерато- 35 ров импульсов объединены и подключены к выходу второго дешифратора нуля, первые входы которого объединены с входами дешифратора и подключены к соответствующим выходам первого дешиф- 40 ратора нуля, вторые входы второго

дешифратора нуля соединены с соответствующими выходами дешифратора, кроме старшего.

2. Преобразователь по п. 1, о т - 45 личающийся тем, что второй дешифратор нуля вьтолнен на К-1 элементах НЕ, К-1 элементах И и элементе ИЛИ, выход которого является выходом второго дешифратора нуля, К первых . 50 входов второго дешифратора нуля

соединены с первыми входами соответственно элемента ИЛИ и элементов И, выходы которых подключены к остальным-входам элемента ИЛИ, каждый из 55 вторых входов вторйго дешифратора нуля через соответствующий элемент НЕ . соединен с одним из остальных входов соответствующего элемента И.

30

Фиг 1

Редактор И.Дербак

Составитель О.Ревинский

Техред О.Сопко , Корректор О.Луговая

Заказ 3716/55Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1130355 Москва, 1-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г,Ужгород,ул.Проектная,4

Фи.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1988 |

|

SU1603529A2 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1159165A1 |

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Преобразователь параллельного кода в последовательный | 1989 |

|

SU1619407A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

| Преобразователь кодов | 1986 |

|

SU1363480A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| Преобразователь код-ШИМ | 1987 |

|

SU1462488A1 |

Изобретение относится к вычислительной технике, может быть использовано в системах передачи и преобразования цифровых данных и позволяет повысить быстродействие. Преобразователь содержит регистр 1 сдвига, первый дешифратор 2 нуля, дешифратор 4, коммутатор 5, первый 6 и второй 7 генераторы импульсов. Введение второго деишфратора 3 нуля, триггера 8 и , элемента ИЛИ 9 обеспечивает преобразование без предварительного сдвига информации путем приблизительного определения формата преобразуемого кода на выходах первого дешифратора 2 нуля. 1 3.п. ф-лы, 2 ил. О9 СХ)

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU860056A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-11—Подача