VI

VI .N СО

СА (Л

Изобретение относится к вычислительной технике и может быть использовано для построения блоков микропрограммного управления ЭВМ.

Цель изобретения - сокращение емко- сти памяти микрокоманд.

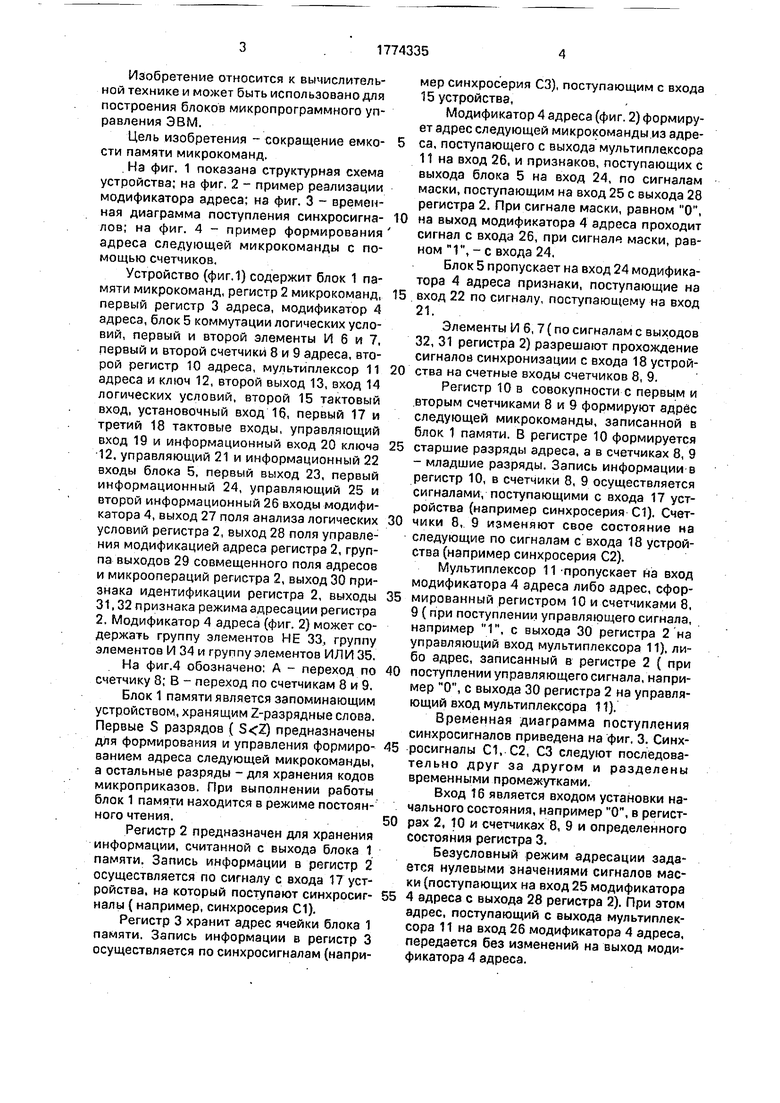

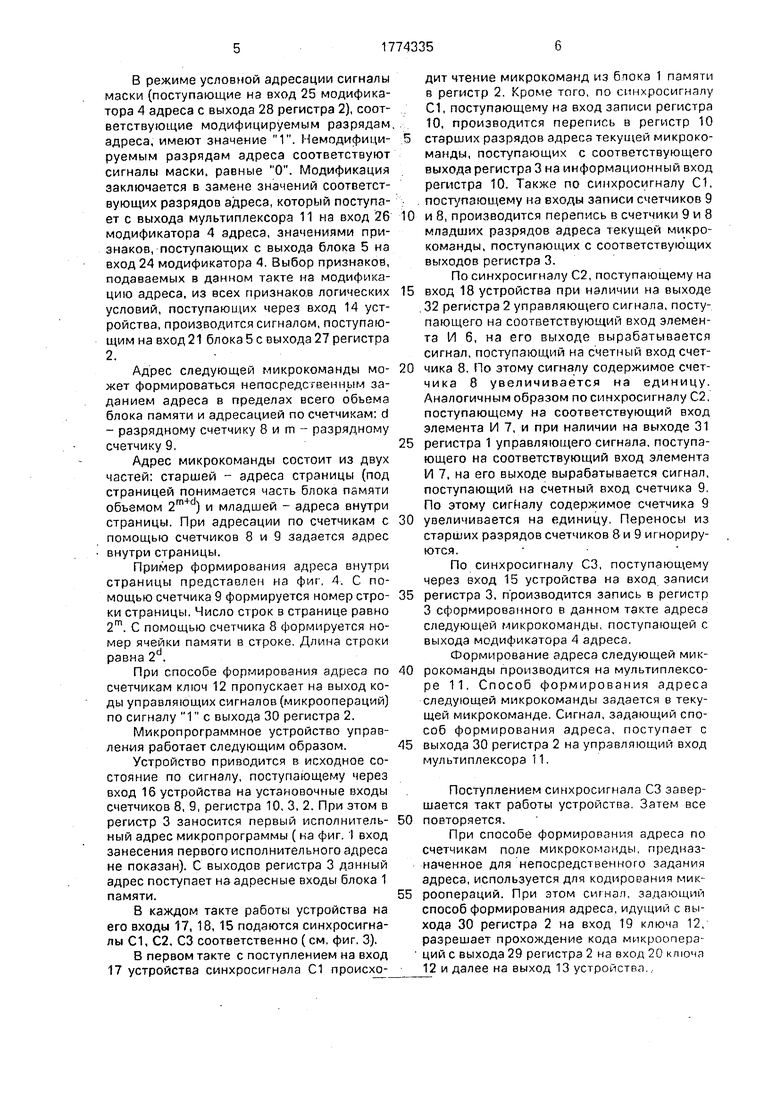

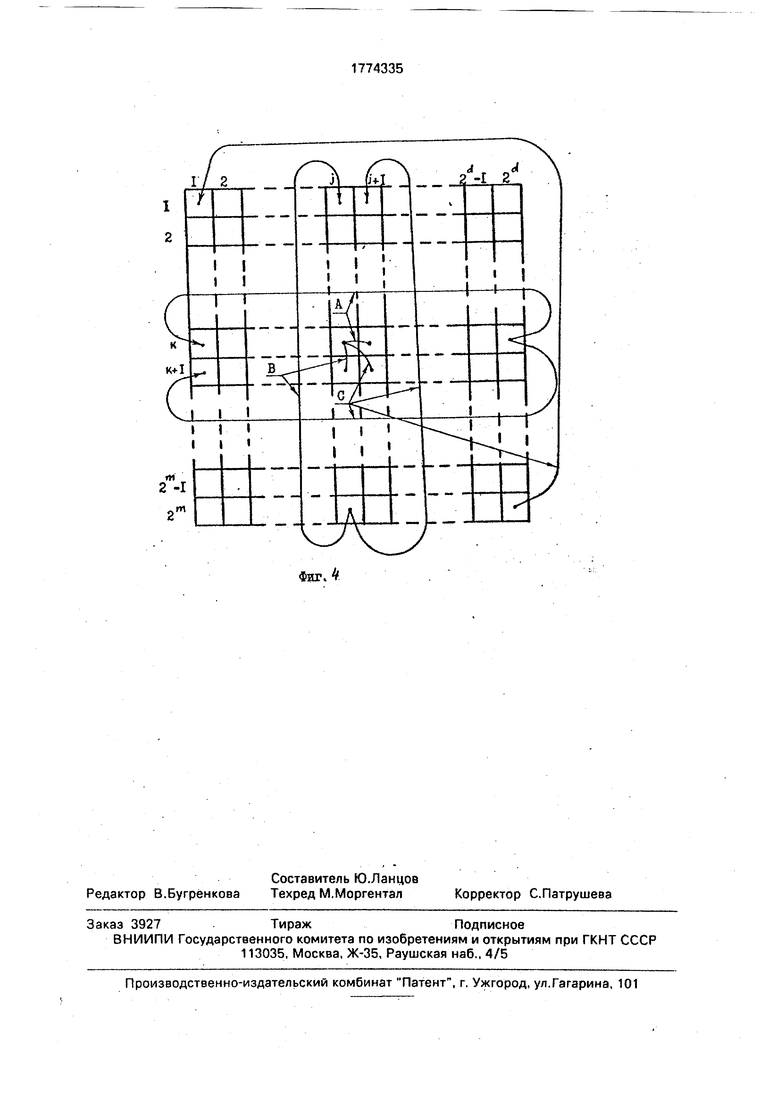

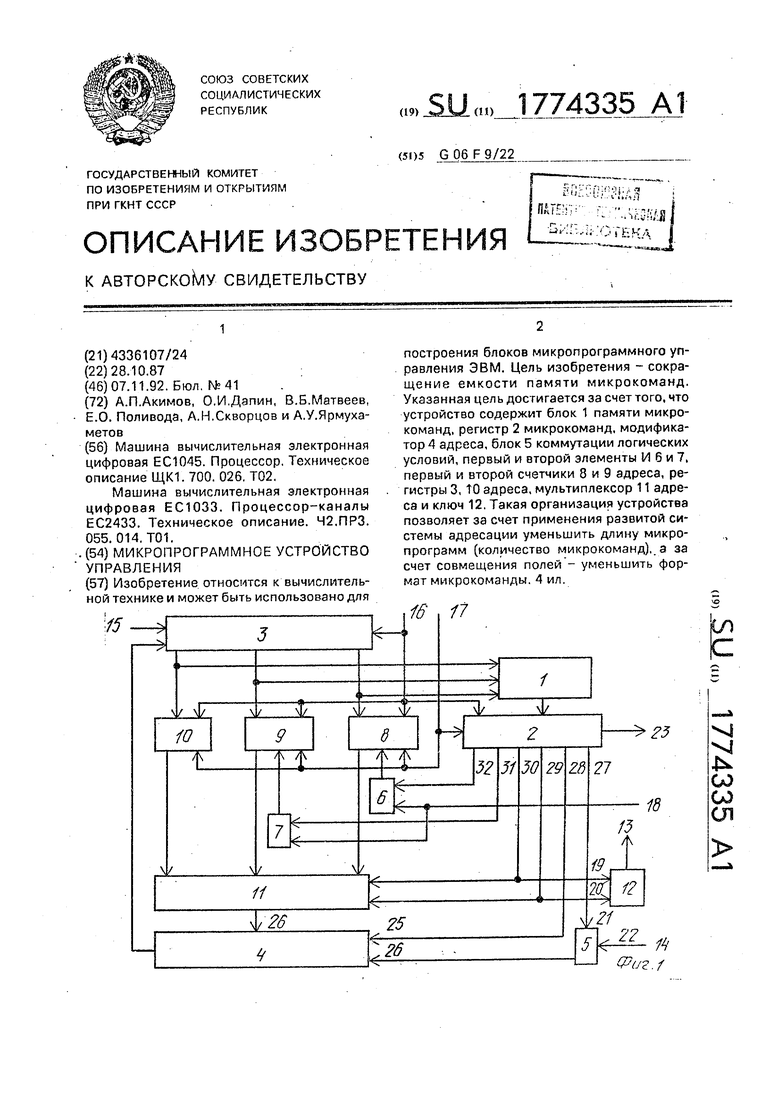

На фиг. 1 показана структурная схема устройства; на фиг. 2 - пример реализации модификатора адреса; на фиг. 3 - временная диаграмма поступления синхросигна- лов; на фиг. 4 - пример формирования адреса следующей микрокоманды с помощью счетчиков.

Устройство (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, первый регистр 3 адреса, модификатор 4 адреса, блок 5 коммутации логических условий, первый и второй элементы И б и 7, первый и второй счетчики 8 и 9 адреса, второй регистр 10 адреса, мультиплексор 11 адреса и ключ 12, второй выход 13, вход 14 логических условий, второй 15 тактовый вход, установочный вход 16, первый 17 и третий 18 тактовые входы, управляющий вход 19 и информационный вход 20 ключа 12, управляющий 21 и информационный 22 входы блока 5, первый выход 23, первый информационный 24, управляющий 25 и второй информационный 26 входы модификатора 4, выход 27 поля анализа логических условий регистра 2, выход 28 поля управления модификацией адреса регистра 2, группа выходов 29 совмещенного поля адресов и микроопераций регистра 2, выход 30 признака идентификации регистра 2, выходы 31,32 признака режима адресации регистра 2. Модификатор 4 адреса (фиг. 2) может содержать группу элементов НЕ 33, группу элементов И 34 и группу элементов ИЛИ 35.

На фиг.4 обозначено: А - переход по счетчику 8; В - переход по счетчикам 8 и 9. Блок 1 памяти является запоминающим устройством, хранящим Z-разрядные слова. Первые S разрядов ( ) предназначены для формирования и управления формиро- ванием адреса следующей микрокоманды, а остальные разряды - для хранения кодов микроприказов. При выполнении работы блок 1 памяти находится в режиме постоянного чтения.

Регистр 2 предназначен для хранения информации, считанной с выхода блока 1 памяти. Запись информации в регистр 2 осуществляется по сигналу с входа 17 устройства, на который поступают синхросиг- налы (например, синхросерия С1).

Регистр 3 хранит адрес ячейки блока 1 памяти. Запись информации в регистр 3 осуществляется по синхросигналам (например синхросерия СЗ), поступающим с входа 15 устройства,

Модификатор 4 адреса (фиг. 2) формирует адрес следующей микрокоманды из адреса, поступающего с выхода мультиплексора 11 на вход 26, и признаков, поступающих с выхода блока 5 на вход 24, по сигналам маски, поступающим на вход 25 с выхода 28 регистра 2. При сигнале маски, равном О, на выход модификатора 4 адреса проходит сигнал с входа 26, при сигналя маски, равном 1,-с входа 24.

Блок 5 пропускает на вход 24 модификатора 4 адреса признаки, поступающие на вход 22 по сигналу, поступающему на вход 21.

Элементы И 6,7 (по сигналам с выходов 32, 31 регистра 2) разрешают прохождение сигналов синхронизации с входа 18 устройства на счетные входы счетчиков 8, 9.

Регистр 10 в совокупности с первым и вторым счетчиками 8 и 9 формируют адрес следующей микрокоманды, записанной в блок 1 памяти. В регистре 10 формируется старшие разряды адреса, а в счетчиках 8, 9 - младшие разряды. Запись информации в регистр 10, в счетчики 8, 9 осуществляется сигналами, поступающими с входа 17 устройства (например синхросерия С1). Счетчики 8, 9 изменяют свое состояние на следующие по сигналам с входа 18 устройства (например синхросерия С2).

Мультиплексор 11 -пропускает на вход модификатора 4 адреса либо адрес, сформированный регистром 10 и счетчиками 8, 9 (при поступлении управляющего сигнала, например 1, с выхода 30 регистра 2 на управляющий вход мультиплексора 11), либо адрес, записанный в регистре 2 ( при поступлении управляющего сигнала, например О, с выхода 30 регистра 2 на управляющий вход мультиплексора 11).

Временная диаграмма поступления синхросигналов приведена на фиг, 3. Синхросигналы С1, С2, СЗ следуют последовательно друг за другом и разделены временными промежутками.

Вход 16 является входом установки начального состояния, например Он, в регистрах 2, 10 и счетчиках 8, 9 и определенного состояния регистра 3.

безусловный режим адресации задается нулевыми значениями сигналов маски (поступающих на вход 25 модификатора 4 адреса с выхода 28 регистра 2). При этом адрес, поступающий с выхода мультиплексора 11 на вход 26 модификатора 4 адреса, передается без изменений на выход модификатора 4 адреса.

В режиме условной адресации сигналы маски (поступающие на вход 25 модификатора А адреса с выхода 28 регистра 2), соответствующие модифицируемым разрядам адреса, имеют значение 1. Немодифицируемым разрядам адреса соответствуют сигналы маски, равные О. Модификация заключается в замене значений соответствующих разрядов адреса, который поступает с выхода мультиплексора 11 на вход 26 модификатора 4 адреса, значениями признаков, поступающих с выхода блока 5 на вход 24 модификатора 4. Выбор признаков, подаваемых в данном такте на модификацию адреса, из всех признаков логических условий, поступающих через вход 14 устройства, производится сигналом,поступающим на вход 21 блока 5 с выхода 27 регистра 2.

Адрес следующей микрокоманды может формироваться непосредственным заданием адреса в пределах всего объема блока памяти и адресацией по счетчикам; d - разрядному счетчику бит- разрядному счетчику 9.

Адрес микрокоманды состоит из двух частей: старшей - адреса страницы (под страницей понимается часть блока памяти объемом 2m+d) и младшей - адреса внутри страницы. При адресации по счетчикам с помощью счетчиков 8 и 9 задается адрес внутри страницы.

Пример формирования адреса внутри страницы представлен на фиг. 4. С помощью счетчика 9 формируется номер строки страницы. Число строк в странице равно 2т. С помощью счетчика 8 формируется номер ячейки памяти в строке. Длина строки равна 2 .

При способе формирования адреса по счетчикам ключ 12 пропускает на выход коды управляющих сигналов (микроопераций) по сигналу 1 с выхода 30 регистра 2.

Микропрограммное устройство управления работает следующим образом.

Устройство приводится в исходное состояние по сигналу, поступающему через вход 16 устройства на установочные входы счетчиков 8, 9, регистра 10, 3, 2. При этом в регистр 3 заносится первый исполнительный адрес микропрограммы ( на фиг. 1 вход занесения первого исполнительного адреса не показан). С выходов регистра 3 данный адрес поступает на адресные входы блока 1 памяти.

В каждом такте работы устройства на его входы 17, 18, 15 подаются синхросигналы С1, С2, СЗ соответственно ( см, фиг. 3),

В первом такте с поступлением из вход 17 устройства синхросигнала С1 происходит чтение микрокоманд из бпокз 1 памяти в регистр 2. Кроме того, по синхросигналу С1, поступающему на вход записи регистра 10, производится перепись в регистр 10 5 старших разрядов адреса текущей микрокоманды, поступающих с соответствующего выхода регистра 3 на информационный вход регистра 10. Также по синхросигналу С1, поступающему на входы записи счетчиков 9 10 и 8, производится перепись в счетчики 9 и 8 младших разрядов адреса текущей микрокоманды, поступающих с соответствующих выходов регистра 3.

По синхросигналу С2, поступающему на 15 вход 18 устройства при наличии на выходе 32 регистра 2 управляющего сигнала, поступающего на соответствующий вход элемента И 6, на его выходе вырабатывается сигнал, поступающий на счетный вход счет0 чика 8. По этому сигналу содержимое счет- чика 8 увеличивается на единицу. Аналогичным образом по синхросигналу С2, поступающему на соответствующий вход элемента 1/1 7, и при наличии на выходе 31

5 регистра 1 управляющего сигнала, поступающего на соответствующий вход элемента I/I 7, на его выходе вырабатывается сигнал, поступающий на счетный вход счетчика 9, По этому сигйалу содержимое счетчика 9

0 увеличивается на единицу. Переносы из старших разрядов счетчиков 8 и 9 иг нориру- ются.

По синхросигналу СЗ, поступающему через вход 15 устройства на вход записи

5 регистра 3, производится запись в регистр 3 сформированного в данном такте адреса следующей микрокоманды, поступающей с выхода модификатора 4 адреса.

Формирование адреса следующей мик0 рокоманды производится на мультиплексоре 11. Способ формирования адреса следующей микрокоманды задается в текущей микрокоманде. Сигнал, задающий способ формирования адреса, поступает с

5 выхода 30 регистра 2 на управляющий вход мультиплексора 11.

Поступлением синхросигнала СЗ завершается такт работы устройства. Затем все

0 повторяется.

При способе формирования адреса по счетчикам поле микрокоманды, предназначенное для непосредственного задания адреса, используется для кодирования мик5 роопераций. При этом сигнал, задающий способ формирования адреса, идущий с выхода 30 регистра 2 на вход 19 ключа 12, разрешает прохождение кода микроопераций с выхода 29 регистра 2 на вход 20 ключа 12 и далее на выход 13 устройства

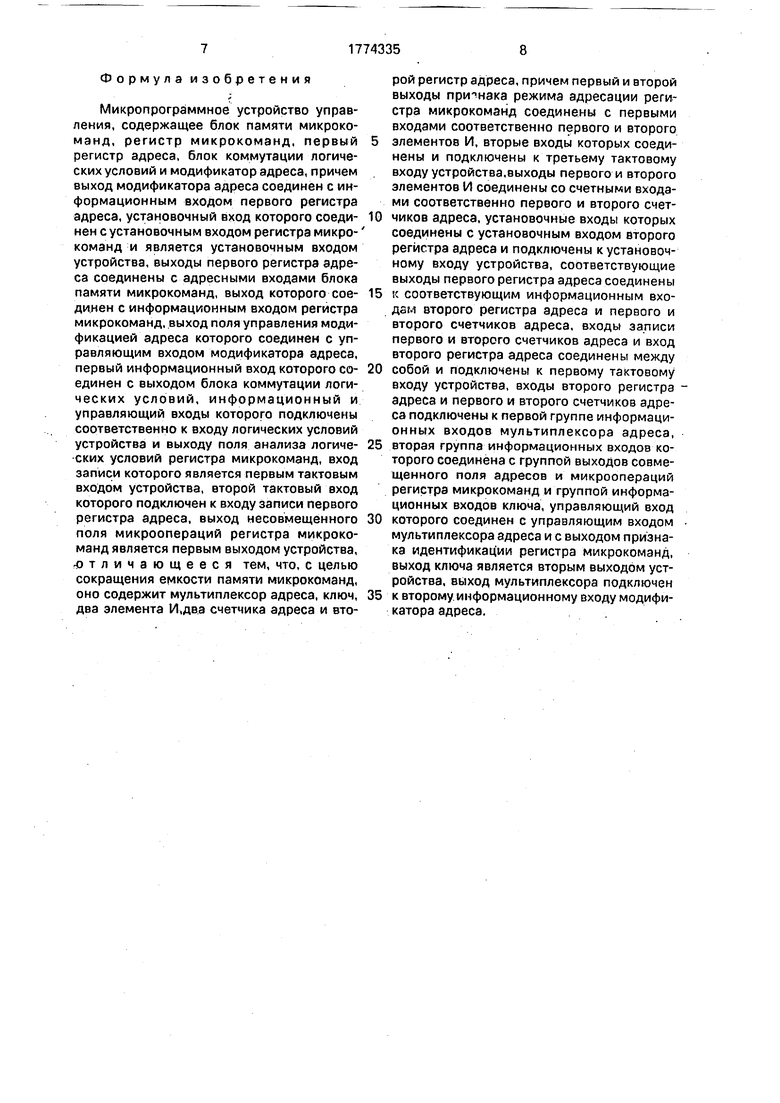

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, первый регистр адреса, блок коммутации логических условий и модификатор адреса, причем выход модификатора адреса соединен с информационным входом первого регистра адреса, установочный вход которого соеди- нен с установочным входом регистра микрокоманд и является установочным входом устройства, выходы первого регистра адреса соединены с адресными входами блока памяти микрокоманд, выход которого сое- динен с информационным входом регистра микрокоманд, выход поля управления модификацией адреса которого соединен с управляющим входом модификатора адреса, первый информационный вход которого со- единен с выходом блока коммутации логических условий, информационный и управляющий входы которого подключены соответственно к входу логических условий устройства и выходу поля анализа логиче- ских условий регистра микрокоманд, вход записи которого является первым тактовым входом устройства, второй тактовый вход которого подключен к входу записи первого регистра адреса, выход несовмещенного поля микроопераций регистра микрокоманд является первым выходом устройства, -отличающееся тем, что, с целью сокращения емкости памяти микрокоманд, оно содержит мультиплексор адреса, ключ, два элемента И,два счетчика адреса и второй регистр адреса, причем первый и второй выходы признака режима адресации регистра микрокоманд соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены и подключены к третьему тактовому входу устройства,выходы первого и второго элементов И соединены со счетными входами соответственно первого и второго счетчиков адреса, установочные входы которых соединены с установочным входом второго регистра адреса и подключены к установочному входу устройства, соответствующие выходы первого регистра адреса соединены it соответствующим информационным входам второго регистра адреса и первого и второго счетчиков адреса, входы записи первого и второго счетчиков адреса и вход второго регистра адреса соединены между собой и подключены к первому тактовому входу устройства, входы второго регистра адреса и первого и второго счетчиков адреса подключены к первой группе информационных входов мультиплексора адреса, вторая группа информационных входов которого соединена с группой выходов совмещенного поля адресов и микроопераций регистра микрокоманд и группой информационных входов ключа, управляющий вход которого соединен с управляющим входом мультиплексора адреса и с выходом признака идентификации регистра микрокоманд, выход ключа является вторым выходом устройства, выход мультиплексора подключен к второму информационному входу модификатора адреса.

Синхросигнал С2 (ьход 18)

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1767500A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

Изобретение относится к вычислительной технике и может быть использовано для -# построения блоков микропрограммного управления ЭВМ. Цель изобретения - сокращение емкости памяти микрокоманд. Указанная цель достигается за счет того, что устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, модификатор 4 адреса, блок 5 коммутации логических условий, первый и второй элементы И 6 и 7, первый и второй счетчики 8 и 9 адреса, регистры 3, ТО адреса, мультиплексор 11 адреса и ключ 12. Такая организация устройства позволяет за счет применения развитой системы адресации уменьшить длину микропрограмм (количество микрокоманд), а за счет совмещения полей - уменьшить формат микрокоманды. 4 ил.

Сикхглсилшл СЗ , (вход 15) MI,,

«Orr

Фиг. 3

Авторы

Даты

1992-11-07—Публикация

1987-10-28—Подача