I

Изобретение относится к цифровой вычислительной технике и дискретной автоматике.

Известен счетчик, содержащий счетный вход и разряды, каждый из которых содаржит первый и второй коцмутациоиные триггеры и триггер памяти причем счетный вход соединен со входами всех азрядов, а выход переноса каждого разряда соединен со входами всех последующих разрядов Cl.

Недостаток этого счетчика - большое число соединений выходов младnoix разрядов со входами старших, что увеличивает его сложность.

Наиболее близок к предлагаемому счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, выход переноса каждой группы соединен с тактовьми всех последующих групп, а в каждой группе

5-входы первого коммутационного триггера старшего разряда соединены попарно с первыми вьгходами триггеров памяти и вторыми выходами первых коммутационных триггеров всех предшествующих разрядов данной группы, а ft -входы первого коммутационного триггера старшего разряда соединены попарно с выходами переноса всех предшествующих разрядов в данной группе, кроме того R -входы коммутационных триггеров каждого разряда, кроме старшего, соединены попарно с выходами переноса всех предшествуняцих разрядов в данной группе, тактовые входы группы соединены с Rвходами коммутационных триггеров всех разрядов данной группы, а выход переноса старшего разряда группы соединен с выходом переноса данной группы С23.

Этот счетчик отличается высоким быстродействием и меньшим числом меяфазрядных связей по сравнению с другими устройствами.

Недостатком этого счетчика является его сложность, что связано с относительно большим числом межразрядных внутригрупповых связей и большим числом входов первого коммутационного триггера старшего разряда.

Для построения группы из /праэрядов с одним тактовым входом потребуется 2(h-l) 5 -входов и входов первого коммутационного триг191791

гера CTapDierb разряда. При использо Iвании логических элементов И-НЕ с максимально коэффициентом объединения по входам 8 можно построить . группу только из четырех разрядов.

Целью изобретения является упро щение счетчика.

Поставленная цель достигается тем, что в счетчике с параллельным пере0 носом, содержащем счетный вход и

(1 -разрядов, каждь1й из которых содержит первый и второй коммутационные триггеры и триггер памяти, первый выход первого коммутационного.

15 триггера соединен с 5 -входом второго коммутационного триггера, второй выход которого соединены с К входамн первого коммутационного триггера памяти, второй выход перво0 го коммутационного триггера соединен с 5 -входом триггера памяти, выход которого соединен с 5 -йходом первого коммутационного триггера, первые R -входы первого и второго

5 коммутационных триггеров всех разрядов соединены со счетным входом, причем первый выход второго коммутационного триггера каждого разряда, кроме разрядов со второго по 1с-и,

0 соединен со вторым R -входом первого коммутационного триггера всех последующих разрядов и со вторым R -. входом коммутационного триггера каждого последукяцего разряда, кроме старшего, выход триггера памяти и второй выход первого коммутационного триггера первого разряда соединены попарно с S -входами первого коммутационного триггера старшего разряда, первый выход второго коммутационного триггера каждого из разрядов со второго по 1с-и соединен с вспомогательным R-входом первого коммутационного триггера следующего разряда, первый выход второго коммутационного триггера каждого из разрядов со второго по X-и соединен с дополнительным 5 -входом первого коммутационнрго триггера следующего разряда, а первый выход второго ком-

мутационного триггера каждого из

разрядов с (.V-ll-ro по (ь-1) -и соединен с соответствующим вспомогательным 5 -входом первого коммутационного триггера старшего разряда. ного триггера старшего 1 -го разряда.

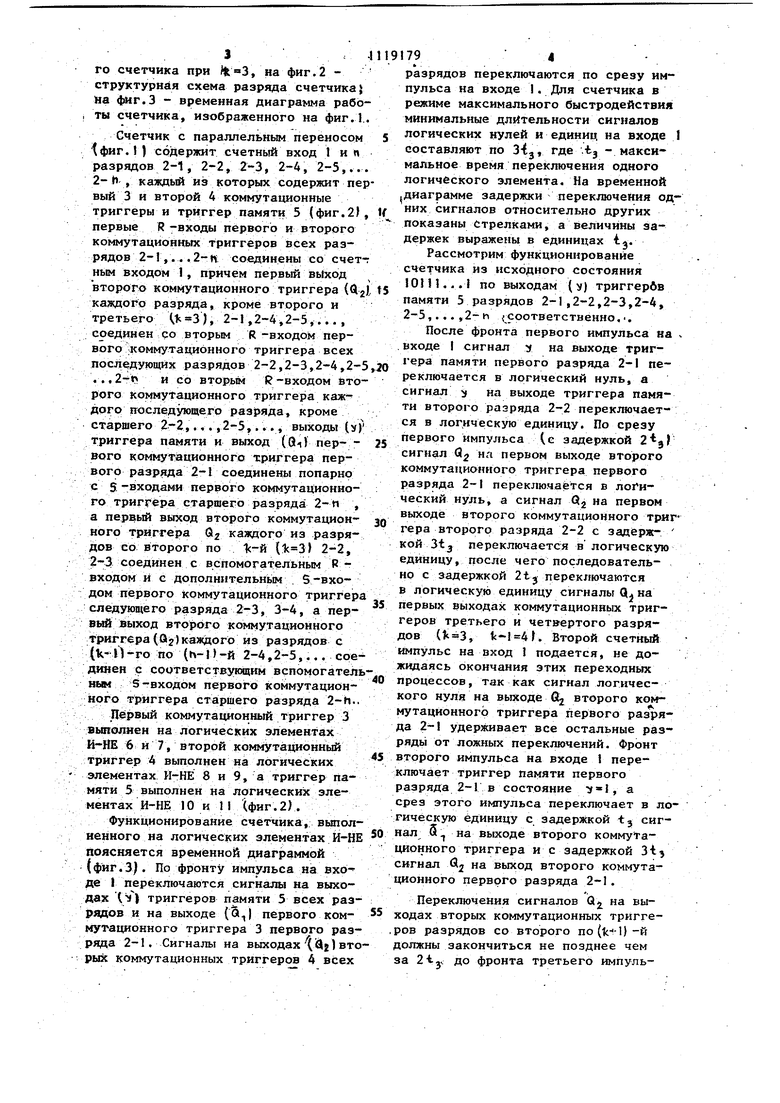

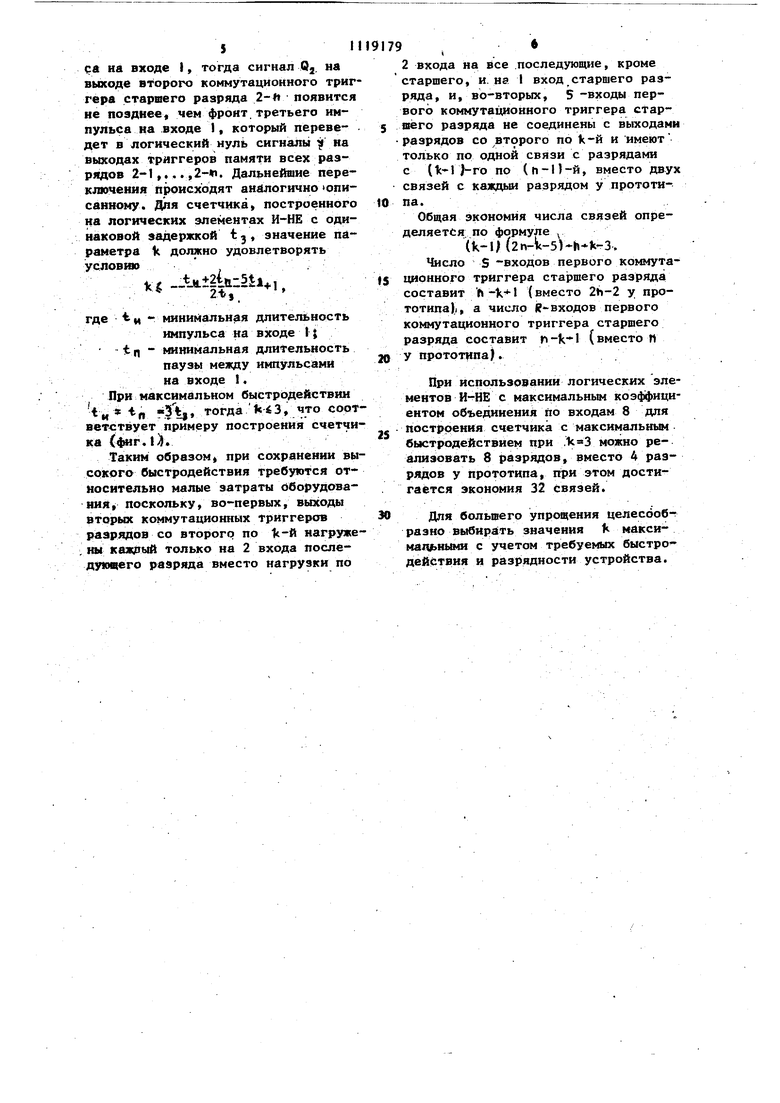

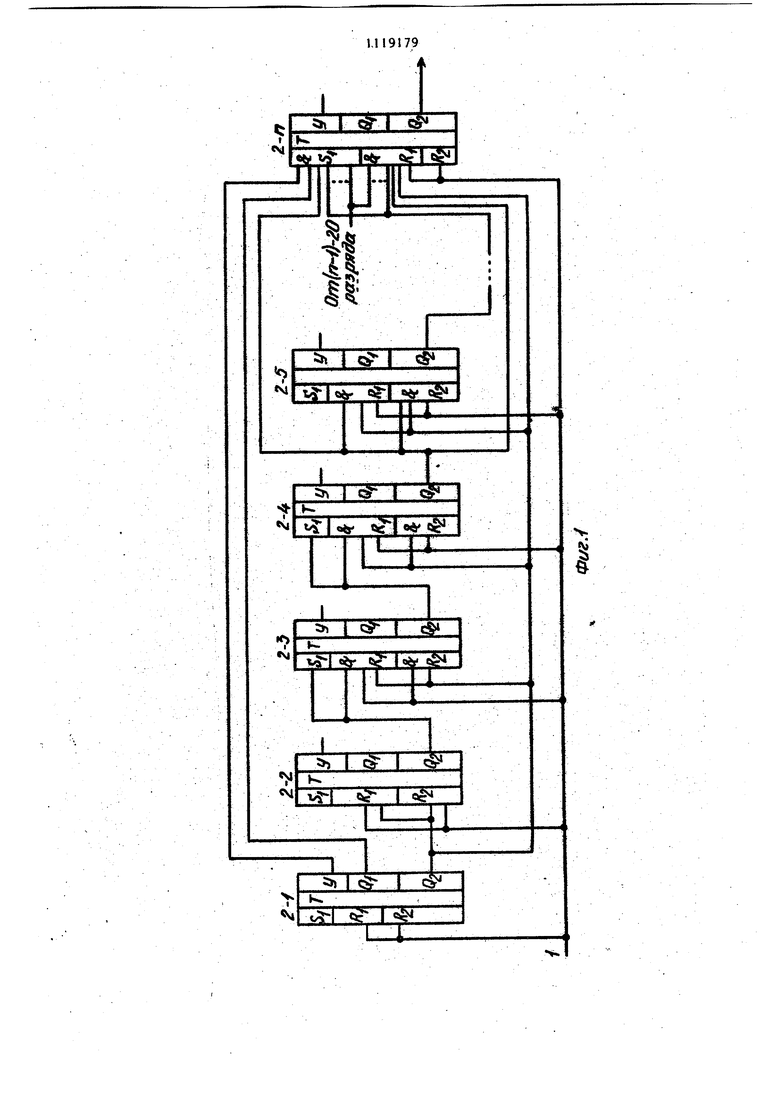

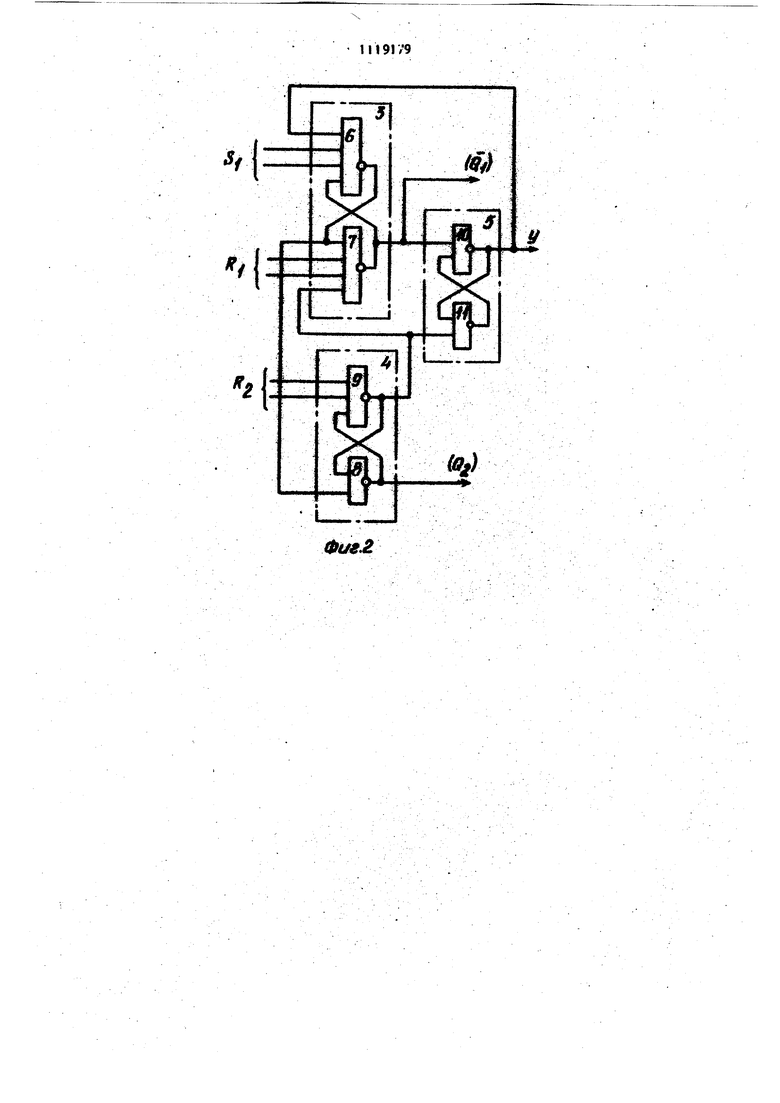

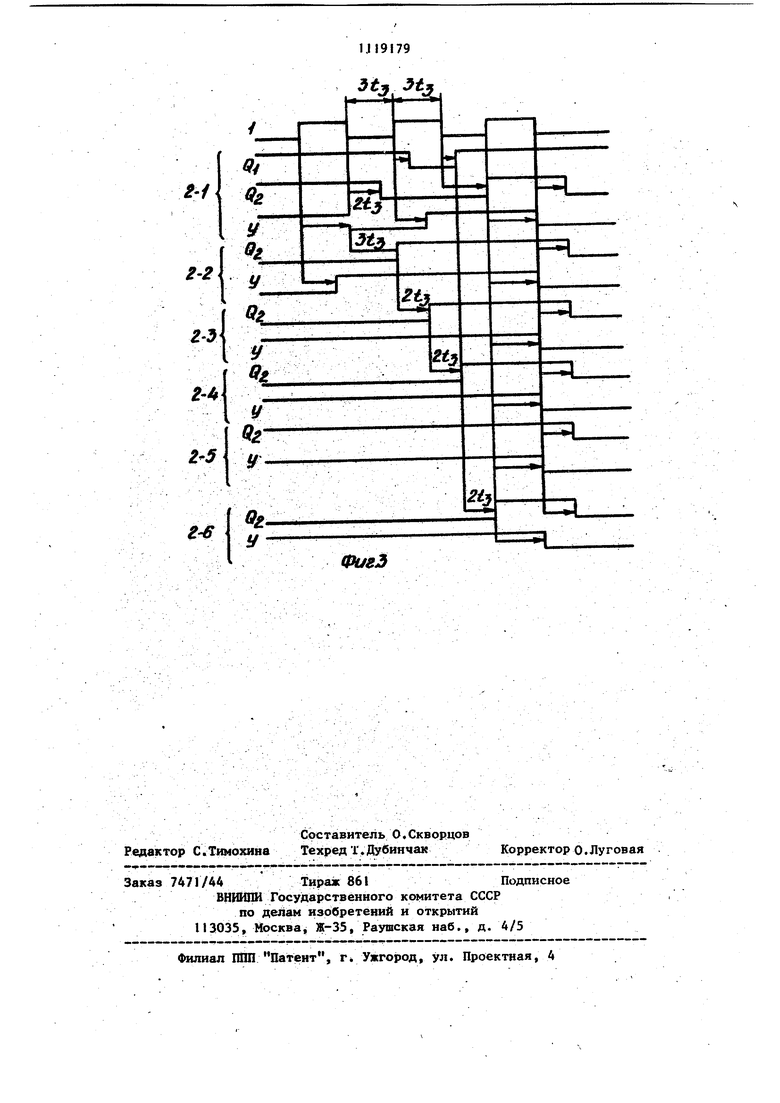

На фиг.1 изображен пример построения структурной,схемы г -разрядна 3 . . го счетчика при , на фиг.2 структурная схема разряда счетчика} На фиг.З - временная диаграмма рабо ты счетчика, изображенного на фиг.1. Счетчик с параллельным переносом фиг.) содержит счетный вход 1 и п разрядов 2-1, 2-2, 2-3, 2-4, 2-5,.. 2-h , каждый из которых содержит пер вый 3 и второй 4 коммутационные триггеры и триггер памяти 5 (фиг.2) первые R-входы первого и второго коммутационных триггеров всех разрядов 2-1 ,.. .2-й соединены со счет ным входом 1, причем первый выход второго коммутационного триггера (г каждого разряда, кроме второго и третьего ), 2-1 ,2-4,2-5,... , соединен со вторым R -входом первого -коммутационного триггера всех последующих разрядов 2-2,2-3,2-4,2..,2-Г и со вторьм I -входом вто рого Коммутационного триггера каждого последующего разряда, кроме старшего 2-2,.,. ,2-5,..., выходы (у) триггера памяти и выход (Qi) пер- вого коммут;ационного триггера первого разряда 2-1 соединены попарно с 5-входами первого коммутационного триггера старшего разряда 2-и , а первый выход второго коммутационного триггера г каждого из разрядов со второго по (1с-3 , 2-3 соединен с вспомогательным R входом и с дополнительньм . 5-входом первого коммутационного триггер следующего разряда , 3-4, а первый выход второго коммутационного триггера(Qj)каждого из разрядов с ( по (h-)-и 2-4,2-5,... сое динен с соответствующим вспомогател ным S-входом первого коммутационного триггера старшего разряда 2-h. Первый коммутационный триггер 3 выполнен на логических элементах 6 и 7, в то рой коммутационный триггер 4 выполнен на логических элементах Й-НЕ 8 и 9, а триггер памяти 5 выполнен на логических злементах И-НЕ; 10 и 1 Сфиг.2). Функционирование счетчика, выпол ненного на логических элемейтах И-НЕ поясняется временной диаграммой (фиг.З). По фронту импульса на входе I переключаются сигналы на выходах триггеров памяти 5 всех разрздов и на выходе ( первого комМУТационного триггера 3 первого разряда 2-1. Сигналы на выходах д Sj 1 вто рык коммутационных триггеров 4 всех 79 4 разрядов переключаются по срезу импульса на входе I. Для счетчика в режиме максимального быстродействия минимальные длительности сигналов логических нулей и единиц на входе 1 составляют по З-С, где .-Ьз - максимальное время переключения одного логического злемента. На временной .диаграмме задержки переключения одних сигналов относительно других показаны Стрелками, а величины задержек выражены в единицах . Рассмотрим функционирование счетчика из исходного состояния iOMl... по выходам {у) триггеров памяти 5 разрядов 2-1,2-2,2-3,2-4, 2-5,...,2-п { соответственно.-. После фронта первого импульса на входе I сигнал у на выходе триггера памяти первого разряда 2-1 переключается в логический нуль, а сигнал 3 на выходе триггера памяти второго разряда 2-2 переключается в логическую единицу. По срезу первого импульса (с задержкой сигнал (З на первом выходе второго коммутационного триггера первого разряда 2-1 переключается в логический нуль, а сигнал Qj на первом выходе второго коммутационного триггера второго разряда 2-2 с задержкой Jt переключается в логическую единицу, после чего последовательно с задержкой 2tj перекх1ючаются в логическук единицу сигналы Q,. на первых выходах коммутационных триггеров третьего и четвертого разрядов (, . Второй счетный импульс на вход 1 подается, не дожидаясь окончания зтих переходных процессов, так как сигнал логического нуля на выходе 62 второго коммутацНонногр триггера первого разряда 2-1 удерживает все остальные разряды от ложных переключений. Фронт второго импульса на входе 1 переключает триггер памяти первого разряда 2-1 в состояние -yl, а срез этого импульса переключает в логическую единицу с задержкой tj сигнал на выходе второго коммутационного триггера и с задержкой 3 сигнал (2 на выход второго коммутационного первого разряда 2-1. Переключения сигналов 0. на выходах вторых коммутационных триггеров разрядов со второго по(|с--1)-й должны закончиться не позднее чем за до фронта третьего импуль5Iй на входе I, тогда сигнал Qj. на выходе Btopotx) коммутационного триг гера старшего разряда 2-ft появится не позднее чем фронт.третьего нмпульса на входе 1, который переведет в логический муль сигналы i на выходах триггеров памяти всех разрядов 2-1,,,. ,2-. Дальнейшие переключения Происходят аналогично описанному. Для счетчика, построенного на логических элементах И-НЕ с одинаковой задержкой t, значение должно удовлетворять раметра условпо .«tidiiiSii где - минимальная длительность импульса на входе I{ t п ьшннмальная длительность паузы между импульсами на входе I. При максимальном быстродействии Ч„ п «ЗЛ,, тогда ki3, что соот ветствует примеру построения счетчи ка (г.1/}. Таким образом при сохранении вы сокого быстродействия требуются относительно малые затраты оборудования, поскольку, во-первых, выходы вторых коммутационных триггеров разрядов со второго по It-и нагруже ны каасрый только на 2 входа последующего разряда вместо нагрузки по 2 входа на все .последующие, кроме старшего, и. на 1 вход старшего разряда , и, во-вторых, 5 -входы первого коммутационного триггера сТаршёго разряда не соединены с выходами разрядов со дторого по k-й и имеют только по одной связи с разрядами с (1с-1 )-го по (h-И-й, вместо двух связей с каждый разрядом у прототипа. Общая экономия числа связей определяется по формуле , (К-и (2n-t-5V h lc-3. Число S -входов первого коммутационного триггера старшего разряда составит h-l. (вместо 2h-2 у прототипа)/, а число i -входов первого коммутационного триггера старшего разряда составит h-k-l (вместо м у прототипа). При использовании логических элементов И-НЕ с максимальным коэффициентом объединения по входам 8 для построения счетчика с максимальным быстродействием при .1.3 можно реализовать 8 разрядов, вместо 4 разрядов у прототипа, при этом достигается экономия 32 связей. Для большего упрощения целесообразно выбира1ть значения Я максимальными с учетом требуемых быстро действия и разрядности устройства.

ФиеЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный счетчик с параллельным переносом | 1976 |

|

SU788388A1 |

| Счетное устройство | 1980 |

|

SU953741A1 |

| Счетчик с параллельным переносом | 1974 |

|

SU507943A1 |

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| СЧЕТЧИК | 1991 |

|

RU2028028C1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ, содержащий счетный вход и П разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, первый выход первого коммутационного триггера соединен с 5 -входом второго коммутационного триггера, ьторой выход которого соединен с К -входами первого коммутационного триггера и триггера памяти, второй выход первого коммутационного триггера соединен с 5-входом триггера памяти, вькод которогЬ соединен с S входом первого коммутационного триг-., гера, первые R -входы первого и второго коммутационных триггеров всех разрядов соединены со счетным входом, первый выход второго коммутационного триггера каждого разряда, кроме разрядов со второго по k -и, соединен со вторым R-входок первого коммутационного триггера всех последующих разрядов и со вторым R- входом второго коммутационного триггера каждого последующего разряда, кроме старшего, выход триггера памяти и второй выход первого коммутационного триггера первого разряда соединены попарно с S- входами первого коммутационного триггера старшего разряда, а первый выход второго коммутационного триггера каждого из разрядов со второго по Ic -и соединен с вспомогательным R -входом первого коммутационно7 го триггера следующего разряда, о т л и ч а ющ и и с я тем, что, с целью упрощения, первый выход второго коммутационного триггера каждого из разрядов со второго по 1с-й соединен с дополнительным S входом первого коммутационного триггера следующего разряда, а первь СО выход второго коммутационного триггера каждого из разрядов с {1(-1 )-го vl по (n-0-й соединен с соответствуюсо щим вспомогательным S -входом первого коммутационного триггера старшего разряда.

| J | |||

| ДВОИЧНЫЙ СЧЕТЧИК | 0 |

|

SU340099A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетчик | 1977 |

|

SU705688A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-29—Подача