(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления кубического корня | 1980 |

|

SU1084786A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Устройство для извлечения квадратного корня | 1973 |

|

SU544960A1 |

| Устройство для извлечения квадратного корня | 1987 |

|

SU1425662A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

1

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления квадратного корня.

Известно устройство для вычисления квадратного корня, содержащее генератор импульсов, вычитающий счетчик, управляемый делитель,-индикатор нуля, два триггера и логические элементы 1J.

Недостаток этого устройства заключается в относительной сложности его реализации, так как аппаратурные затраты зависят от разрядности счетчиков, входящих в состав устройства.

Наиболее близким техническим рещением к предлагаемому является устройство для вычисления квадратного корня, содержащее четыре регистра, два сумматора, триггер, элемент задержки, четыре элемента И, инвертор, элемент ИЛИ и блок управления 2.

Недостаток устройства заключается в сложности его реализации.

Цель изобретения - упрощение устройства.

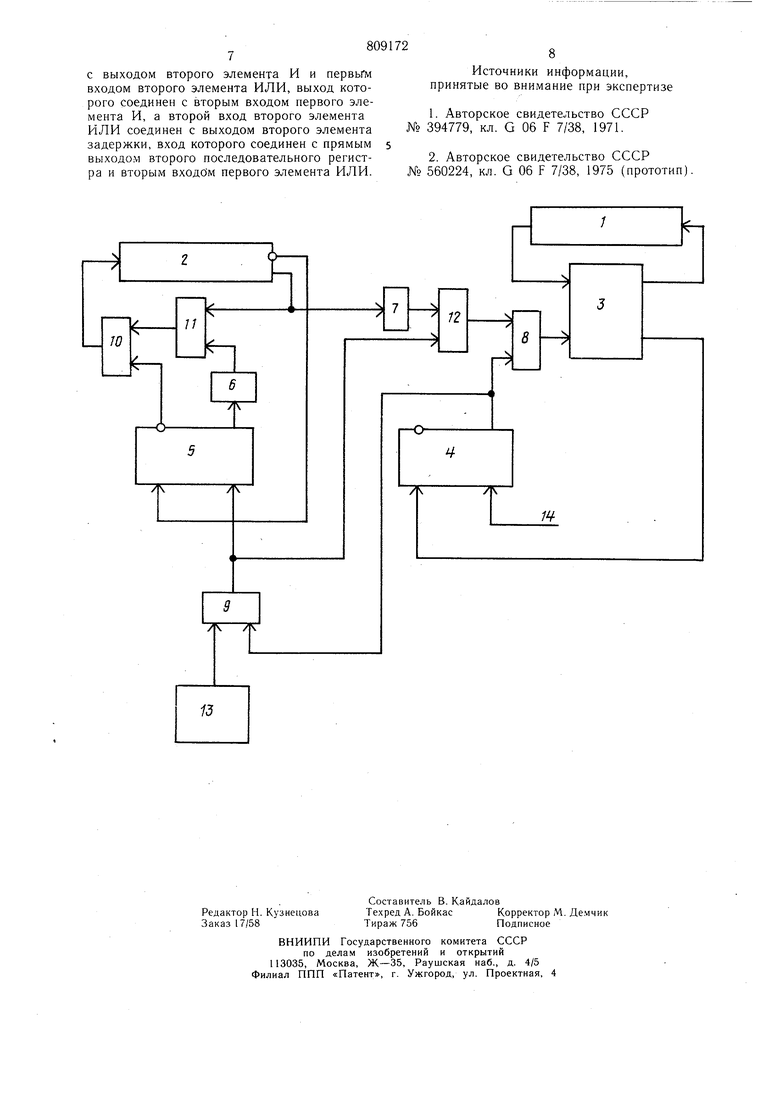

Поставленная цель достигается тем, что в устройстве для вычисления квадратного корня, содержащем два последовательных регистра, сумматор, два триггера, два элемента задержки, три элемента И, два элемента ИЛИ и генератор импульсов, причем сумматор подключен первым входом к выходу первого последовательного регистра, вторым входом - к выходу первого элемента И, первым выходом - к входу первого последовательного регистра и вторым выходом - к нулевому входу первого триггера, единичный вход которого подключен к управляющей шине устройства, а единичный выход - к первому входу первого элемента И и к первому входу второго элемента И, второй вход которого подключен к выходу генератора импульсов, вход второго последовательного регистра соединен с выходом третьего элемента И, первый вход которого соединен с выходом первого элемента ИЛИ, второй триггер соединен нулевым выходом с вторым

входом третьего элемента И, а единичным выходом - с первым элементом задержки, выход которого соединен с первым входом первого элемента ИЛИ, нулевой вход второго триггера соединен с инверсным выходом второго последовательного регистра, а единичный вход - с выходом второго элемента И и первым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, а второй вход второго элемента ИЛИ соединен с выходом второго элемента задержки, вход которого соединен с прямым выходом второго последовательного регистра и вторым входом первого элемента ИЛИ. На чертеже изображена структурная схема устройства для вычисления квадратного корня. Устройство содержит два последовательных регистра 1 и 2, сумматор 3, два триггера 4 и 5, два элемента задержки 6 и 7, три элемента И 8-10, два; элемента ИЛИ 11 и 12, генератор 13 импульсов и управляющую шину 14. Вы.од регистра 1 соединен с первым входом сумматора 3, первый выход которого соединен с входом регистра 1. Второй выход сумматора 3 соединен с нулевым входом триггера 4, единичный выход которого соединен с первыми входами элемента И 8 и 9. Второй вход сумматора 3 соединен с выходом элемента 8 И. Триггер 5 соединен единичным выходом с входом элемента 6 задержки, выход которого соединен с первым входом элемента 11 ИЛИ. Вход регистра 2 соединен с выходом элемента 10 И, первый вход которого соединен с выходом элемента 11 ИЛИ. Инверсный выход регистра 2 соединен с нулевым входом триггера 5, нулевой выход которого соединен с вторым ВХОДОМ элемента 10 И. Прямой выход регистра 2 соединен с входом элемента 7 задержки и вторым входом элемента 1 1 ИЛИ. Элемент 12 ИЛИ соединен выходом с вторым входом элемента 8 И, первым входом - с выходом элемента 9 И и единичным входом триггера 5, вторым входом - с выходом элемента 7 задержки. Выход генератора импульсов 13 соединен с вторым входом элемента 9 И. Управляющая щина 14 подключена к единичному входу триггера 4. Устройство для вычисления квадратного корня работает следующим образом. В.исходном состоянии триггеры 4 и 5 находятся в нулевом состоянии. Элемент 10 И открыт по второму входу единичным сигналом нулевого выхода триггера 5, а элементы И 8 и 9 закрыты по первому входу нулевым сигналом единичного выхода триггера 4. Цепь циркуляции последовательного кода в регистре 1 замкнута через одноразрядный сумматор 3, а в регистре 2 - через элемент 10 И и элемент 11 ИЛМ. В регистр 1 записывается последовательно, начиная с младших разрядов, дополнительный двоичный код подкоренного выражения, который запоминается динамическим способом в замкнуто цепи регистр 1 -сумматор 3. регистр 2 в исходном состоянии очищен. Запуск устройства осуществляется подачей единичного сигнала на управляющую шину 14, который устанавливает триггер 4 в единичное состояние. Триггер 4 в единичном состоянии открывает элементы И 8 и 9, подключая выход элемента 12 ИЛИ к второму входу сумматора 3 и выход генератора импульсов 13 - к единичному входу триггера 5 соответственно. Первый выходной импульс генератора 13 устанавливает триггер 5 в единичное состояние и через элемент 12 ИЛИ и элемент 8 И поступает на второй вход сумматора 3 на первый вход которого поступает первый разряд дополнительного кода подкоренного выражения с выхода регистра 1. Сумматор 3 выполняет последовательно, начиная с младших разрядов, суммирование импульса с выхода элемента 8 И с дополнительным кодо.м подкоренного выражения, увеличивая его на единицу. В это время триггер 5 возвращается в нулевое состояние импульсом первого разряда инверсного выхода регистра 2. Переключение триггера 5 из единичного состояния в нулевое приводит к формированию на выходе элемента 10 И импульсного сигнала. Действительно, элемент задержки 6 поддерживает на первом входе элемента 1 1 ИЛИ единичный сигнал, который действует через элемент 11 ИЛИ на первом входе элемента 10 И одновременно с единичным сигналом нулевого выхода триггера 5 в течение времени, необходимого для формирова ния на выходе элемента 10 И импульсного сигнала, который записывается в регистр 2 по месту первого разряда. Таким образом, на первом щаге вычислений содержимое регистров 1 и 2 увеличивается на единицу. Второй выходной импульс генератора 13 вновь устанавливает триггер 5 в единичное состояние и через элемент 12 ИЛИ и элемент 8 И поступает на второй вход сумматора 3 во время считывания с выхода регистра 1 сигнала младшего разряда дополнительного двоичного кода предыдущего щага вычислений. Двоичный код предыдущего щага вычислений, сформированный в регистре 2, задерживается элементом 7 задержки на время обработки одного разряда сумматором 3 и через элемент 12 ИЛИ и элемент 8 И .поступает на второй вход сумматора 3, начиная с момента времени считывания второго разряда дополнительного двоичного кода с выхода регистра 1. Если двоичный код регистра 2 на i - 1 щаге вычислений обозначить через у,-, , то элемент 7 задержки обеспечивает умножение этого кода на два, а элемент 12 ИЛИ формирует сумму 2у,-.. + , так как число 2у - четное, а выходной импульс генератора 13 на каждом шаге вычислений поддерживает единичный код в первом разряде выходного кода элемента 12 ИЛИ. Двоичный код 2yi + 1 с выхода элемента 12 ИЛИ через элемент 8 И поступает на второй вход сумматора 3, где суммируется с дополнительным кодом предыдущего шага вычислений регистра 1. Таким образом в регистре 1 на i шлге вычислений накапливается сумма Х( 2 -Хо + (2;Хо -дополнительный код подкоренного выражения Хв; п -количество разрядов регистра 1. В регистре 2 на шаге вычислений накапливается двоичная сумма, равная количеству шагов вычислений У; i ,(2) двоичный код регистра 2 на i шаге вычислений; i - количество шагов вычислений. Действительно, формирование импульсного сигнала на выходе элемента 10 И в момент перехода триггера 5 из единичного состояния в нулевое обеспечивает двоичный счет шагов вычислений следующим образом. Триггер 5 в единичном состоянии, в которое его устанавливает выходной импульс генератора 13, закрывает элемент 10 И по второму входу, разрывая этим цепь циркуляции кодов в регистре 2. Поэтому младшие разряды двоичного кода регистра 2 стираются до тех пор, пока триггер 5 не вернется в нулевое состояние, в которое его вернет первый , считая с младшего разряда, импульс на инверсном выходе регистра 2. Во время перехода триггера 5 из единичного состояния в нулевое, как описано ранее, на выходе элемента 10 И сформируется импульс, который записывается по месту первого нуля двоичного кода регистра 2. После возврата триггера 5 в нулевое состояние цепь циркуляции кодов в регистре 2 замыкается и остальные разряды двоичного кода регистра 2 переписываются с выхода на вход без изменения. Для четырехразрядного регистра 2, например, имеем после первого шага двоичный код 0001, который во втором шаге преобразуется в код 0(J10, так как единица в младшем разряде стирается, а первый нуль в коде 0001 содержится во втором разряде, который возвращает триггер 5 в нулевое состояние, при котором во втором разряде формируется импульс единичного кода. В дальнейщем двоичный код 0010 на третьем щаге преобразуется в регистре 2 в код ООП, на четвертом шаге - в код 0100 и т.д. вычисления продолжаются до переполнения регистра 1, когда на К шаге вычислений накопленная сумма Х будет удовлетворять неравенству Из (1) и (2) следует, что равенство (3) имеет место при выполнении соотношения Хо Z(2y;., + 1), «1 у« К Выражение (4) с учетом известного соотношенияу; . +1) преобразуется к виду у. К Wo гдеу -двоичный код регистра 2 на К шаге вычислений. В случае переполнения регистра 1, когда имеет место соотношение (3), на втором выходе сумматора 3 появляется сигнал переноса из п-го разряда, который, поступая на нулевой вход триггера 4, сбрасывает его в нулевое состояние. Триггер 4 в нулевом состоянии закрывает по первому входу элементы И 8 и 9, запрещй я поступление сигналов на второй вход сумматора 3 и единичный вход триггера 5 соответственно. В регистре 2 фиксируется двоичный код результата вычисления квадратного корня. Технико-экономические преимущества устройства для вычисления квадратного корня заключаются в простоте реализации и высокой точности вычислений. Устройство для вычисления квадратного корня содержит меньше блоков на два регистра и один сумматор, чем в известном. Формула изобретения Устройство для вычисления квадратного корня, содержащее два последовательных регистра, сумматор, два триггера, два элемента задержки, три элемента И, два элемента ИЛИ и генератор импульсов, причем сумматор подключен первым входом к выходу первого последовательного регистра, вторым входом - к выходу первого элемента И, первым выходом - к входу первого последовательного регистра и вторым выходом - к нулевому входу первого триггера, единичный вход которого подключен к управляющей шине устройства, а единичный выход- к первому входу первого элемента И и к первому входу второго элемента И, второй вход которого подключен к выходу генератора импульсов, отличающееся тем, что, с целью упрощения устройства, вход второго последовательного регистра соединен с выходом третьего элемента И, первый вход которого соединен с выходом первого элемента ИЛИ, второй триггер соединен нулевым выходом с вторым входом третьего элемента И, а единичным выходом - с первым элементом задержки, выход которого соединен с первым входом первого элемента ИЛИ, нулевой вход второго триггера соединен с инверсным выходом второго последовательного регистра, а единичный вход -

с выходом второго элемента И и первым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, а второй вход второго элемента ИЛИ соединен с выходом второго элемента задержки, вход которого соединен с прямым выходом второго последовательного регистра и вторым входом первого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-02-28—Публикация

1979-05-14—Подача