ошибок адреса и данных, коррекция выдаваемых на выход 21 устройства считанных данных. Тестирование позво1

Изобретение относится к вычислительной технике и может быть применено для автоматизированного обнаружения неисправностей и сбоев в информационных и адресных, цепях блоков памяти.

Целью изобретения является повышение достоверности контроля.

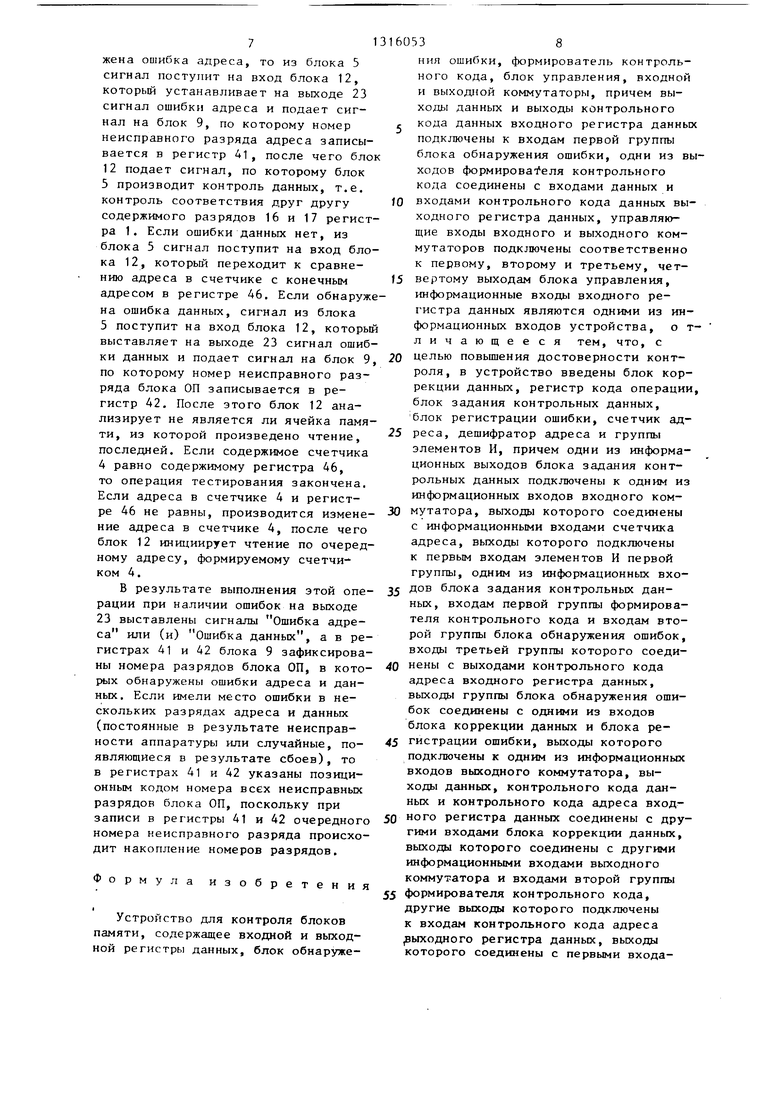

На фиг. 1 приведена функциональная схема предложенного устройства; на фиг. 2-5 - функциональные схемы соответственно формирователя контрольного кода, блока обнаружения ошибки, блока регистрации ошибки и блока задания контрольных данных,

Устройство содержит (фиг, 1) входной и выходной 2 регистры данных, регистр 3 кода операции, счетчик 4 адреса, блок 5 обнаружения ошибки, формирователь 6 контрольного кода, блок 7 задания контрольных данных, блок 8 коррекции данных, блок 9 регистрации ошибки, входной 10 и выходной 11 коммутаторы, блок 12 управления, дешифратор 13 адреса, первую 14 и вторую 15 группы элементов И. На фиг. 1 обозначены группы разрядов 16 данных, разрядов 17 контрольного кода данных и разрядов 18 контрольного кода адреса регистров 1 и 2 данных, адресные входы 19, одни из информационных входов 20 и выходов 21, вход 22, синхронизации, управляющие входы 22., контрольный 23, адресные 24 и управляющие 25 выходы, другие информационные выходы 26 и входы 27 устройства,

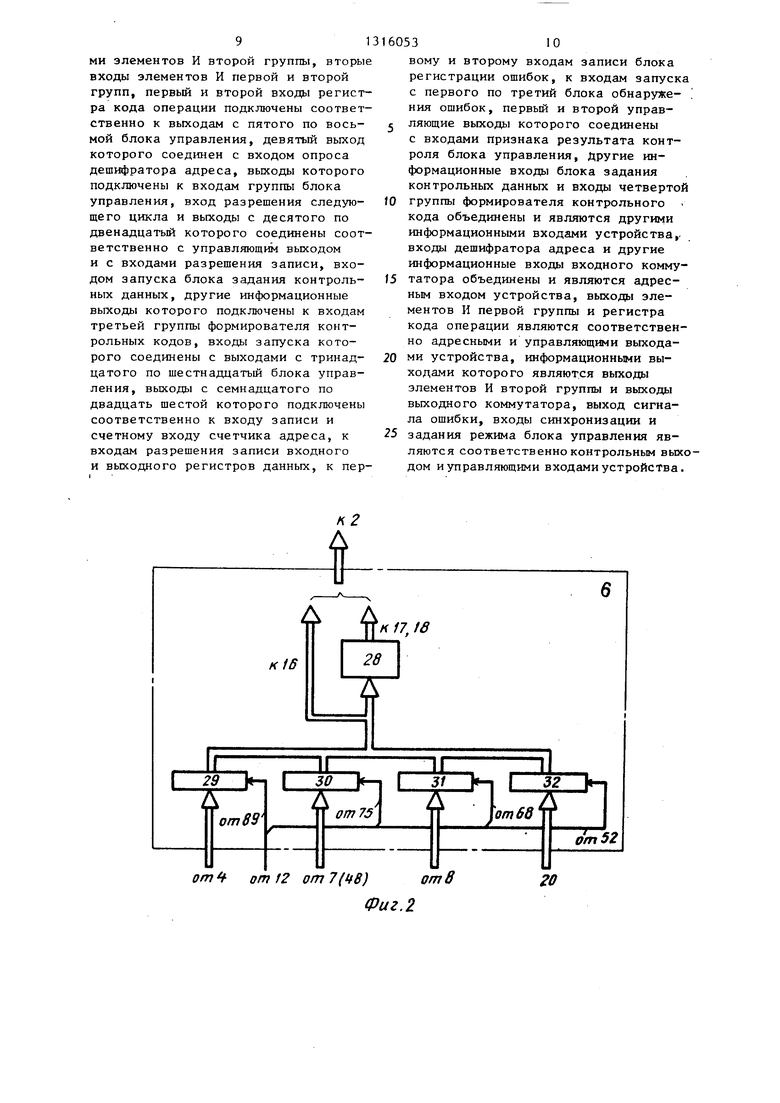

Формирователь 6 контрольного кода содержит (фиг. 2) блоки 28 свертки по модулю два и группы элементов И 29-32.

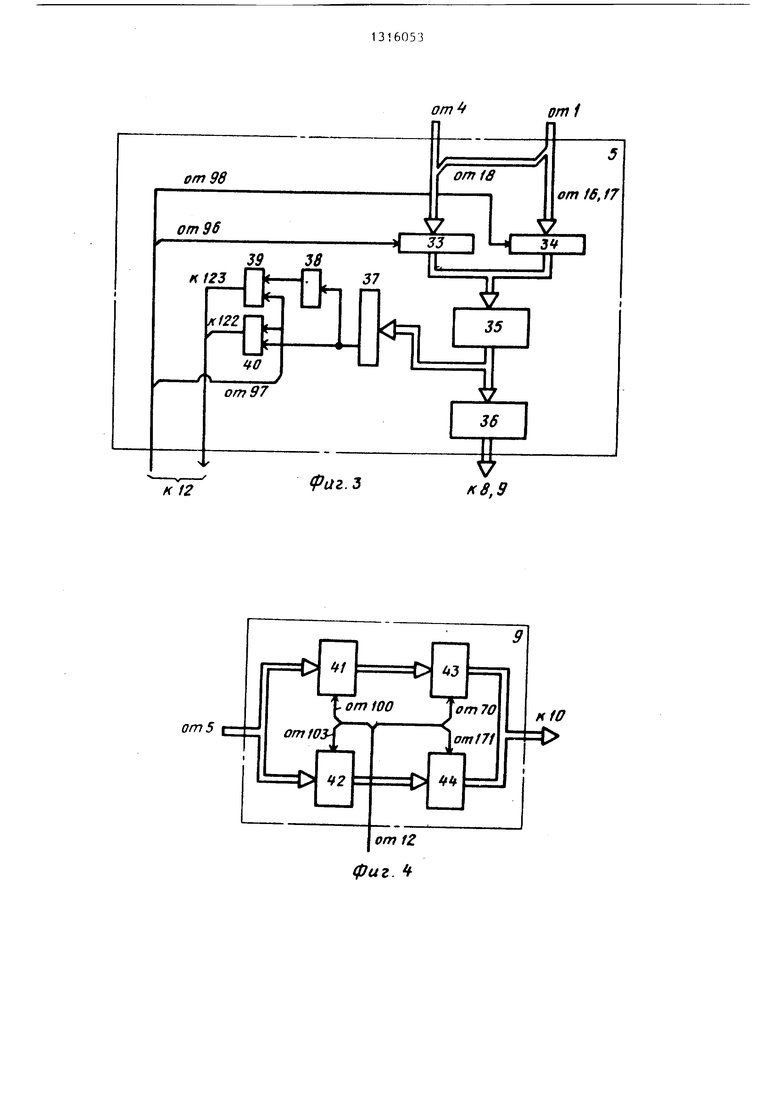

Блок 5 обнаружения ошибки содержит (фиг. 3) группы элементов И 33 и ЗА, блок 35 свертки по модулю два дешифратор 36 номера неисправного

ляет обнаруживать постоянные неисправности аппаратуры и случайные сбои в блоке памяти, 5 ил.

О

5

0

5

0

5

0

5

разряда, элемент ШШ 37, элемент НЕ 38 и элементы И 39 и 40.

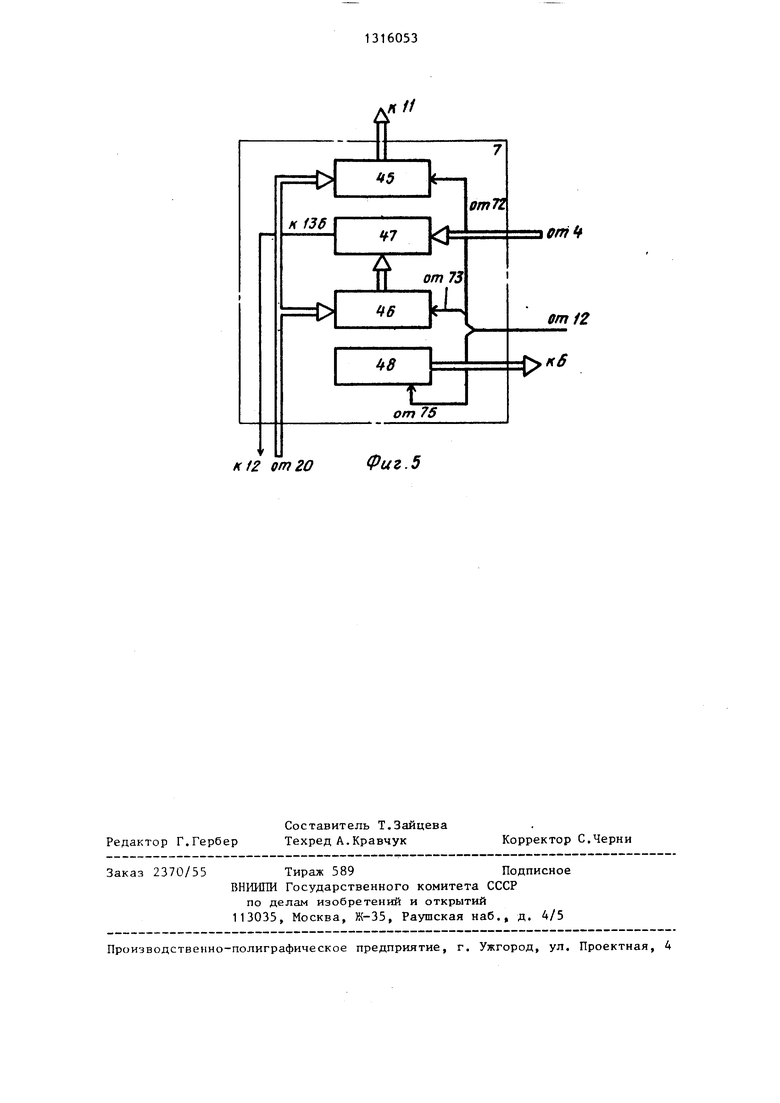

Блок 9 регистрации ошибки содержит (фиг. 4) регистр 41 ошибки адреса, регистр 42 ошибки данных и группы элементов И 43 и 44,

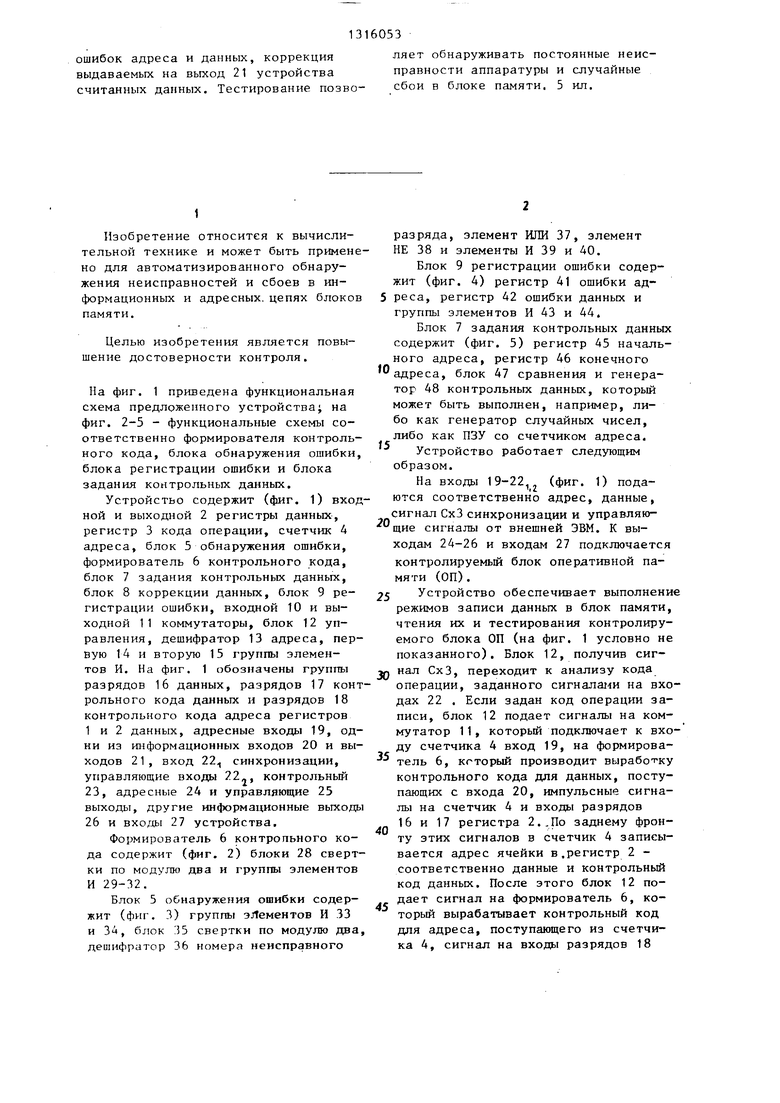

Блок 7 задания контрольных данных содержит (фиг. 5) регистр 45 начального адреса, регистр 46 конечного адреса, блок 47 сравнения и генератор 48 контрольных данных, который может быть выполнен, например, либо как генератор случайных чисел, либо как ПЗУ со счетчиком адреса.

Устройство работает следующим образом.

На входы 19-22, (фиг, 1) подаются соответственно адрес, данные, сигнал СхЗ синхронизации и управляющие сигналы от внешней ЭВМ, К выходам 24-26 и входам 27 подключается контролируемый блок оперативной памяти (СП) ,

Устройство обеспечивает выполнение режимов записи данных в блок памяти, чтения их и тестирования контролируемого блока СП (на фиг, 1 условно не показанного). Блок 12, получив сигнал СхЗ, переходит к анализу кода операции, заданного сигналами на входах 22 , Если задан код операции записи, блок 12 подает сигналы на коммутатор 11, который подключает к входу счетчика 4 вход 19, на формирователь 6, который производит выработку контрольного кода для данных, поступающих с входа 20, импульсные сигналы на счетчик 4 и входы разрядов 16 и 17 регистра 2,.По заднему фронту этих сигналов в счетчик 4 записывается адрес ячейки в.регистр 2 - соответственно данные и контрольньй код данных. После этого блок 12 подает сигнал на формирователь 6, который вырабатывает контрольный код дпя адреса, поступающего из счетчика 4, сигнал на входы разрядов 18

регистра 2, по которому контрольный код адреса записывается из блока 6 в регистр 2 и устанавливает в регистре 3 код операции записи. После этого блок 12 подает потенциальный сигнал на элементы И 14 и 15, в результате в контролируемый блок памяти поступают адрес ячейки, подлежащие записи данные, контрольный код данных и контрольный код адреса через выходы 24 и 26, ас выхода 25 поступает код операции.

После этого блок 12 устанавливает на выходе 23 сигнал СхИ, определяющий, что данные с входов 20 переданы в блок памяти, снимает сигнал управления с входов элементов И 14 и 15 и переходит к ожиданию сброса сигнала СхЗ. После сброса сигнала СхЗблок 12 сбрасывает сигнал СхИ и устанавливает устройство в исходное состояние. В режиме чтения на входах 19 присутствует адрес ячейки памяти блока ОП, на входах 222 - код операции чтения, после чего подается сигнал СхЗ. Блок 12 анализирует код операции, после чего подает сигнал на коммутатор 11, который подключает входы 19 к входам счетчика 4, в который записывается адрес ячейки памяти, а в регистре 3 по сигналу из блока 12 устанавливается код операции чтения. После этого блок 12 подает потенциальный сигнал на элементы И 14, по которому адрес ячейки поступает со счетчика 4 на выход 24, в ответ из контролируемого блока ОП на вход 27 поступает содержимое ячейки памяти.

В следующем такте работы блок 12 подает сигнал на регистр 1, в которы через входы разрядов 16-18 записываются соответственно данные, контрольный код данных и контрольный код адреса, считанные из блока памяти. Затем блок 12 выдает сигнал на блок 5, по которому последний производит соответствия заданного адреса (содержимого счетчика 4) считанному контрольному коду (содержащемуся в регистре 1) и, при наличии несоответствия, вырабатывает код номера неисправного разряда блока памяти.

После этого блок 12 подает сигнал

в блок 5 для анализа результата конт-гг в контролируемом блоке ОП не произроля. Если адрес соответствует контрольному коду, то из блока 5 поступает импульсный сигнал, по которому блок 12 дает команду для выполнения

водится, на выходе 23 устанавливается признак ошибки данных, а в регист ре 42 блока 9 регистрируется номер неисправного разряда блока памяти.

О

контроля данных. Если адрес и контрольный код не соответствуют друг другу, из блока 3 поступает сигнал, по которому блок 12 выдает в блок 9 сигнал записи, по которому блок 9 фиксирует номер разряда адреса, представленный позиционным кодом, где имеет место несоответствие, а блок 12 выставляет на выходе 23 сигнал ошибки адреса.

После этого блок 12 выдает в блок 5 сигнал, по которому производится контроль соответствия полученных данных и контрольного кода

данньгх (содержащихся в разрядах 16 и 17 регистра 1), ив случае ошибки в данньгх вырабатывает номер неисправного разряда блока памяти. После этого блок 12 подает сигнал в блок 5, анализируя результат контроля. Если данные соответствуют контрольному коду, из блока 5 поступает импульсный сигнал на блок 12, который подает на коммутатор 10, тем самым

5 выдавая содержимое разрядов 16 регистра 1 через блок 8 на выход 21. Если данные не соответствуют контрольным разрядам, из блока 3 посту0

0

5

0

5

0

была ли обнаружена ошибка в адресе или нет, блок 12 работает следующим образом.

Если ошибки адреса не было, то по сигналу с блока 5 блок 12 подает сигнал на коммутатор 10, разрешая выдачу скорректированных данных с выхода блока 8 на выход 21, сигнал на блок 6, который вырабатывает конт- рольньм код для скорректироваиньк данных, установленных на выходе блока 8, сигнал для записи данных в разряды 16 и контрольного кода в разряды 17 регистра 2, и сигнал в блок 9 для регистрации номера неисправного разряда блока памяти. Одновременно на выход 23 поступает сигнал о том, что имела место ошибка в данных и произведена их корректировка.

Если ранее бьша обнаружена ошибка адреса, то сигнал с блока 5 пройдет в блок 12 и активизирует на его выходе сигнал разрешения записи признака-ошибки данных в блок 9.

В этом схгучае коррекция данных

водится, на выходе 23 устанавливается признак ошибки данных, а в регистре 42 блока 9 регистрируется номер неисправного разряда блока памяти.

513

После этого блок 12 подает на коммутатор 10 сигнал, по которому скорректированные данные с выхода блока 8 поступают на выход 21, после чего блок 12 устанавливает устройство в исходное состояние и выдает сигнал СхИ окончания операции,,

Режим тест состоит из четырех операций: чтение содержимого регистра 41 ошибки адреса, чтение содержимого регистра 42 ошибки данных, запись в регистр 45 начального.адреса, запись в регистр 46 конечного адреса и проверка аппаратуры.

Если на входах 222 задан код операции тест, блок 12 анализирует адрес на входе 19, для чего подает на вход дешифратора 13 сигнал опроса. Если на входе 19 задан адрес регистра 41 (фиг. 4), то по сигналу с соответствующего выхода дешифратора 13 блок 12 подает потенциальньй сигнал на коммутатор 10 и на элементы И 43 блока 9, по которому к выходу 21 подключается выход регистра 41, а блок 12 устанавливает на выходе 23 сигнал СхИ.

В режиме операции Чтение регистра ошибки данных на входе 19 задан адрес регистра 42. По сигналу с соответствующего выхода дешифратора 13 блок 12 подает сигнал на коммутатор 10 и на элементы И 44 блока 9, по которому к выходу 21 подклйчится выход регистра 42.

В режиме операции записи в регистр начального адреса устройство анализирует код операции аналогично описанному выше. На входе 19 задан адрес регистра 45 (фиг. 5), по сигна лу с соответствующего выхода дешифратора 13 блок 12 подает сигнал записи В блок 7, по которому данные с входа 20 записываются в регистр 45

В режиме операции записи в регистр конечного адреса и проверки аппаратуры устройство работает следующим образом. I

Если на входе 19 задан адрес регистра 46, то в результате анализа кода операции и кода адреса, сигнал с выхода дешифратора 13 на блок 12 вызовет сигнал записи данных с входа 20 в регистр 46, после чего блок 12 подает сигналы на коммутатор 11 и счетчик 4, по которьм производится запись содержимого регистра 45 в счетчик.

60536

В следующем такте блок 12 подает сигнал на блок 6, по которому последний вырабатывает контрольньп код для данных, поступающих из генерато5 ра 48, сигнал на регистр 2, по которому из его разрядов 16 и 17 записываются контрольные данные и контрольный код этих данных, и сигнал в блок 7, по которому генератор 48 формиру 0 ет на своих выходах новые контроль- ные данные (для записи в следующую ячейку памяти при очередном цикле обращения к контролируемому блоку ОП). В следующем такте блок 12 по15 дает сигнал в формирователь 6, по которому последний формирует контрольный код для адреса, и сигналы на регистры 2 и 3, по которым в разряды 18 регистра 2 производится за20 пись контрольного кода адреса, а в регистр 3 записывается код операции записи. I

В следующем такте блок 12 подает

ус сигнал на элементы И 14 и 15, при этом адрес и информация, подлежащая записи, поступают на выходы 24 и 26. После-этого блок 12 анализирует не является ли ячейка памяти контроли-- руемого блока ОП, в которую произведена запись последней, для чего сравнивает адрес этой ячейки с содержимым регистра 46, Если содержимое счетчика 4 не равно содержимому регистра 46, то с выхода блока

12 поступает сигнал в счетчик 4, увеличивая его содержимое на единицу, т.е. формируется адрес очередной ячейки памяти, после чего блок 12 запускает формирование контрольного кода, как описано выше. Если содержимое счетчика 4 равно содержимому регистра 46, блок 12 инициирует операцию чтения из контролируемого блока ОП по адресу, записанному в регистре 45. В следующем такте блок 12 подает импульсный.сигнал на регистр 1, производя запись в него считанной Из блока ОП на вход 27 информации. После этого блок 12 подает сигнал на блок 5, по которому последний производит контроль содержимого разрядов 18 регистра 1 на соответствие его адресу в счетчике 4. В следующем такте блок 12 анализирует результат контроля, аналогично описанному выще. Если ошибки адреса нет, блок 12 перейдет к выполнению контроля данных. Если обнару40

45

50

7

жена ошибка адреса, то из блока 5 сигнал поступит на вход блока 12, который устанавливает на выходе 23 сигнал ошибки адреса и подает сигнал на блок 9, по которому номер неисправного разряда адреса записывается в регистр 41, после чего бло 12 подает сигнал, по которому блок 5 производит контроль данных, т.е. контроль соответствия друг другу содержимого разрядов 16 и 17 регистра 1. Если ошибки данных нет, из блока 5 сигнал поступит на вход блока 12, которьй переходит к сравнению адреса в счетчике с конечным адресом в регистре 46. Если обнаружна ошибка данных, сигнал из блока 5 поступит на вход блока 12, которы выставляет на выходе 23 сигнал ошибки данных и подает сигнал на блок 9 по которому номер неисправного разряда блока ОП записывается в регистр 42. После этого блок 12 анализирует не является ли ячейка памяти, из которой произведено чтение, последней. Если содержимое счетчика 4 равно содержимому регистра 46, то операция тестирования закончена. Если адреса в счетчике 4 и регистре 46 не равны, производится изменение адреса в счетчике 4, после чего блок 12 инициирует чтение по очередному адресу, формируемому счетчиком 4.

В результате выполнения этой операции при наличии ошибок на выходе 23 выставлены сигналы Ошибка адреса или (и) Ошибка данных, а в регистрах 41 и 42 блока 9 зафиксированы номера разрядов блока ОП, в которых обнаружены ошибки адреса и данных. Если имели место ошибки в нескольких разрядах адреса и данных (постоянные в результате неисправности аппаратуры или случайные, появляющиеся в результате сбоев), то в регистрах 41 и 42 указаны позиционным кодом номера всех неисправных разрядов блока ОП, поскольку при записи в регистры 41 и 42 очередного номера неисправного разряда происходит накопление номеров разрядов.

Формул

изобретения

Устройство для контроля блоков памяти, содержащее входной и выходной регистры данных, блок обнаруже

160338

НИЛ ошибки, формирователь контрольного кода, блок управления, входной и выходной коммутаторы, причем выходы данных и выходы контрольного , кода данных входного регистра данных подключены к входам первой группы блока обнаружения ошибки, одни из выходов фopмиpoвafeля контрольного кода соединены с входами данных и

fO входами контрольного кода данных выходного регистра данных, управляющие входы входного и выходного коммутаторов подключены соответственно к первому, второму и третьему, чет15 вертому выходам блока управления, информационные входы входного регистра данных являются одними из информационных входов устройства, о т- личающееся тем, что, с

20 целью повьш1ения достоверности контроля, в устройство введены блок коррекции данных, регистр кода операции, блок задания контрольных данных, блок регистрации ошибки, счетчик ад25 реса, дешифратор адреса и группы

элементов И, причем одни из информационных выходов блока задания контрольных данных подключены к одним из информационных входов входного ком30 мутатора, выходы которого соединены с информационными входами счетчика адреса, выходы которого подключены к первьм входам элементов И первой группы, одним из информационных вхоj дов блока задания контрольных данных, входам первой группы формирователя контрольного кода и входам второй группы блока обнаружения ошибок, входы третьей группы которого соеди40 нены с выходами контрольного кода адреса входного регистра данных, выходы группы блока обнаружения ошибок соединены с одними из входов блока коррекции данных и блока ре45 гистрации ошибки, выходы которого подключены к одним из информационных входов выходного коммутатора, выходы данных, контрольного кода данных и контрольного кода адреса вход50 ного регистра данных соединены с другими входами блока коррекции данных, выходы которого соединены с другими информационными входами выходного коммутатора и входами второй группы

55 формирователя контрольного кода, другие выходы которого подключены к входам контрольного кода адреса выходного регистра данньк, вькоды которого соединены с первыми входа91

ми элементов И второй группы, вторые входы элементов И первой и второй групп, первый и второй входы регистра кода операции подключены соответственно к выходам с пятого по восьмой блока управления, девятый выход которого соединен с входом опроса дешифратора адреса, выходы которого подключены к входам группы блока управления, вход разрешения следующего цикла и выходы с десятого по двенадцатый которого соединены соответственно с управляющим выходом и с входами разрешения записи, входом запуска блока задания контрольных данных, другие информационные выходы которого подключены к входам третьей группы формирователя контрольных кодов, входы запуска которого соединены с выходами с тринадцатого по шестнадцатый блока управления, выходы с семнадцатого по двадцать шестой которого подключены соответственно к входу записи и счетному входу счетчика адреса, к входам разрешения записи входного и выходного регистров данных, к перот от 12 от 7(8) от 8

Фиг.2

310

вому и второму входам записи блока регистрации ошибок, к входам запуска с первого по третий блока обнаруже- , ния ошибок, первый и второй управляющие выходы которого соединены с входами признака результата контроля блока управления. Другие информационные входы блока задания контрольных данных и входы четвертой

группы формирователя контрольного кода объединены и являются другими информационными входами устройства,, входы дешифратора адреса и другие информационные входы входного коммутатора объединены и являются адресным входом устройства, выходы элементов И первой группы и регистра кода операции являются соответственно адресными и управляющими выходами устройства, информационными выходами которого являются выходы элементов И второй группы и выходы выходного коммутатора, выход сигнала ошибки, входы синхронизации и

задания режима блока управления являются соответственно контрольным выходом и управляющими входами устройства.

го

н 12

fft

от 5

от

от 1

к 8.9

U5

100

1

от7О oml71

н10

фиг.

к 12 от 20

Редактор Г.Гербер

Составитель Т.Зайцева Техред А.Кравчук

Заказ 2370/55 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.5

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1290426A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

Изобретение относится к вычислительной техни1{е и может быть применено для автоматизированного обнаружения неисправностей и сбоев в информационных и адресных цепях блоков памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит входной 1 и выходной 2 регистры данных, содержащие данные в разрядах 16, контрольный код данных в разрядах 17 и контрольный код адреса в разрядах 18, регистр 3 кода операции, счетчик 4 адреса, блок 5 обнаружения ошибки, формирователь 6 контрольного кода, блок 7 задания контрольных данных, блок 8 коррекции данных, блок 9 регистрации ошибки, входной 10 и выходной 11 коммутаторы, блок 12 управления, дешифратор 13 адреса, группы элементов И 14 и 15. На вход-,1 19, 20, 22, и поступают от внешней ЭВМ соответственно адрес, данные, подлежащие записи, в контролируемый блок памяти, сигнал синхронизации и код операции. Устройство обеспечивает режимы записи данных в блок памяти, чтения их и тестирование блока памяти. При чтении выполняется контроль считываемых данных и адреса, регистрация.номеров неисправных разрядов при наличии 27 (Л со О) о ел со К, Z, n-t- J2 Фиг.1

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| G 0« F 11/00, 1978. | |||

Авторы

Даты

1987-06-07—Публикация

1985-12-06—Подача