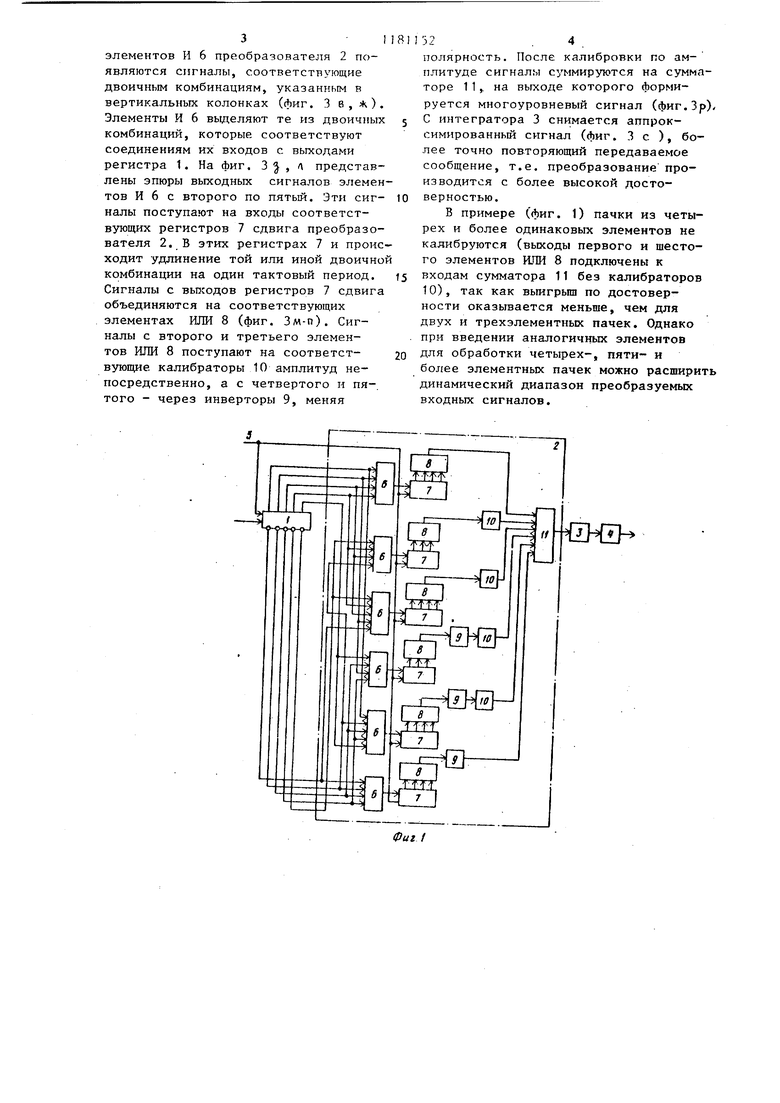

I Изобретение относится к автомат ке и вычислительной технике и може быть использовано при создании лин связи с дельта-модуляцией. Цель изобретения - повышение до товарности преобразования, достигаемое путем более точной аппрокси ции декодированного сигнала к исходному. На фиг. 1 изображена структурнал схема дельта-декодера, на фиг. алгоритм его работы; на фиг. 3 временные диаграммы работы дельтадекодера. Устройство содержит регистр 1 сдвига, преобразователь 2 двоичных комбинаций в многоуровневый сигнал интегратор 3, фильтр 4 н -шних част шину 5 тактирования, а преобразователь 2 комбинаций в многоуровневый сигнал содержит И элементов И П регистров 7 сдвига, И элементов ИХШ 8, п/2 инверторов 9, (ц-2) калибраторов 10 амплитуд и суг-1матор 11, имеющий п входов, выход которо подключен к входу интегратора 3. На фиг. 1 изображена схема для П б. Входы первого элемента И 6 динены с выходами четьфех первых разрядов регистра 1. Входы второго элемента И 6 соединены с прямыми выходами третьего и четвертого и и версным выходом второго и пятого разрядов регистра 1. Входы третье элемента И 6 соединены с прямыми выходами второго, третьего и четвертого и инверсным выходом первог и пятого разрядов регистра 1. Таким образом, первый элемент И 6 выделяет пачку из четырех подряд идущих единиц, второй элемент И.6 - ко бинацию 0110 с пачкой из двух единиц, третий элемент И 6 - комбинацию 01110 с пачкой из трех единиц. Аналогично элементы И 6 четвертого по шестой выделяют соответственно комбинации 1001, 10001 и 0000, т.е пачки из подряд иду1цих нулей. I Выходы всех элементов И 6 подклю чены к информационным входам соответствующих регистров 7 сдвига, тактовые входы которых объединены и подключены к шине 5 тактирования Выходы разрядов всех регистров 7 со динены с входами соответствующих элементов НШ1 8, выходы которых под ключены к входам сумматора 11. 522 Б основе работы дельта-декодера лежнт следующий метод цифровой обработки дельта-модулированного сигнала (фиг. 2). Если наклон od передаваемого сигнала равен величине то его аппроксимация на приемном конце линии связи может быть произведена двумя положительными и одной отрицательной ступеньками & аппроксимации, когда напряжение на интеграторе возрастает на величину + S при интегрировании положительного импульса и падает на величину - 8 при интегрировании отрицательного. Аналогично формируются и остальные наклоны: для наклона ix, обработано (i+2) положительных и один отрицательный импульсы. Однако наклон йд формируется и таким образом В. В -S -|-.-|-., т.е. необходимо проинтегрировать три положительных импульса с амплитудами , где Y - амплитуда исходного положительного импульса. Для аппроксимации наклона У. ц нужно проинтегрировать пачку из четырех единиц с амплитудой и т.д. Для формирования наклона необходимо пачку из i положительных импульсов амплитудой V удлинить на один период тактовой частоты, т.е. сделать ее длину равной ( положительных импульсов и затем откалибровать амплитуду импульсов в этой пачке по закону ll -Ov . Наклон другого знака формируется аналогично: пачка из i отрицательных импульсов (амплитудой - V ) удлиняется до (i+l) и калибруется по амплиту де (iii).Y . 1+Т Дельта-декодер работает следующим образом. Информация, поступающая на вход дельта-декодера с тактовой частотой (ci) в виде дельта-модулированного сигнала (S), записывается в регистр 1 сдвига и последовательно продвигается по нему с помощью тактовых импульсов (В-Ж), При этом на входах

3 I

элементов И 6 преобразователя 2 появляются сигналы, соответствующие двоичным комбинациям, указанньгм в вертикальных колонках (фиг. 3 в, л). Элементы И 6 выделяют те из двоичных комбинаций, которые соответствуют соединениям их входов с выходами регистра 1. На фиг. 3 , л представлены эпюры выходных сигналов элементов И 6 с второго по пятый. Эти сигналы поступают на входы соответствующих регистров 7 сдвига преобразователя 2. В этих регистрах 7 и происходит удлинение той или иной двоичной комбинации на один тактовый период. Сигналы с вькодов регистров 7 сдвига объединяются на соответствующих элементах ИЛИ 8 (фиг. Зм-п). Сигналы с второго и третьего элементов ИЛИ 8 поступают на соответствующие калибраторы 10 амплитуд непосредственно, а с четвертого и пя-. того - через инверторы 9, меняя

52. 4 .

полярность. После калибровки по амплитуде сигналы суммируются на сумматоре 11, на выходе которого формируется многоуровневый сигнал (фиг.Зр С интегратора 3 снимается аппроксимированный сигнал (фиг. 3с), более точно повторяющий передаваемое сообщение, т.е. преобразование производится с более высокой достоверностью.

В примере (фиг. 1) пачки из четырех и более одинаковых элементов не калибруются (выходы первого и шестого элементов ИЛИ 8 подключены к входам сумматора 11 без калибраторов 10), так как выигрыш по достоверности оказывается меньше, чем для двух и трехэлементных пачек. Однако при введении аналогичных элементов для обработки четырех-, пяти- и более элементных пачек можно расшири динамический диапазон преобразуемых входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-декодер | 1986 |

|

SU1381714A1 |

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-декодер | 1990 |

|

SU1728969A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Кодек системы связи | 1983 |

|

SU1150770A1 |

| Устройство для компандированной дельта-модуляции | 1978 |

|

SU1082343A3 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

ДЕЛЬТА-ДЕКОДЕР, содержащий регистр сдвига, информационньА вход которого является входом устройства, а тактовый вход подключен к шине тактирования, преобразователь двоичных комбинаций в многоуровневый сигнал и соединенные последовательно интегратор и фильтр нижних частот, выход которого подключен к выходу .дельта-декодера, отличающийс я тем, что, с целью повьшения ;достоверности преобразования, преобразователь двоичных комбинаций в многоуровневый сигнал вьтолнен I из h элементов И, h элементов ИЛИ, регистров сдвига, п /2 инверторов, (п-2) калибраторов амплитуд и сумматора, выход которого соединен с входом интегратора, прямые и инверсные выходы регистра сдвига подключены к входам соответствующих элементов И преобразователя двоичных комбинаций в многоуровневый сигнал, выходы элементов И соединены с информационными входами соответствующих регистров сдвига, тактовые входы которых объединены и подключены к шине тактирования, выходы разрядов каждого регистра сдвига подключены к входам соответствующего элемента ИЛИ, выход первого эле(О мента ИЛИ соединен с первым входом сумматора, выходы элементов ИЛИ с второго по (п/2)-й через соответствующие калибраторы амплитуд подклюg чены к соответствующим входам сум:матора, выходы элементов ИЛИ с (n+D-ro по (п-1)-й через соединенные последовательно соответствующие инверторы и калибраторы амплитуд подключены к соответствующим входам сумматора, выход h-го элемента ИЛИ через h/2-й инвертор подключен к соответствующему входу сумматора.

| Дельта-модуляция | |||

| Теория и применение.-М.: Связь, 1976, с.164, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , Стил Р | |||

| Принципы дельта-модуля:ЦИи.-М.: Связь, 1979, с | |||

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

Авторы

Даты

1985-09-23—Публикация

1983-07-22—Подача