2. Преобразователь по п. 1, отличающийся тем, что блок преобразования кода в коды косинуса содержит , входной регистр, источник кода смещения фаз, два сумматора по модулю два, запоминакяцее устройство, (k--.2) выходных регистра, последовательно соединенные генератор импульсов, счетчик и дешифратор, выходы которого подключены к управляющим входам соответствующих ( К 2) выходных регистров, входы блока подключены к первым информационным входам входного регистра, первый управляющий вход которого соединен с первым выходом дешифратора, вторые информационные входы соединены с выходом сумматора, а второй управляющий вход соединен с выходом генератора импульсов, выходы входного регистра подключены к одним входам сумматора, другие входы которого подключены к источнику кода смещения фаз, выход предпоследнего старшего разряда входного регистра подключен к одним входам первого сумматора по модулю 2, другие входы которого подключены к выходам остальных младших разрядов входного регистра, а выходы подключены к входам запоминающего устройства, выход последнего старшего разряда вхоного регистра подключен к одним входам второго гумматора по модулю 2 и через инвертор. - к старшим информационным входам выходных регистров, выходы запоминающего устройства подключены к другим входам второго сумматора по модулю 2, выходы которого подключены к младшим информадаонным входам выходных регистров , а выходы выходных регистров подключены к первому , второму и дополнительным выходам блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь балансно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283970A1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1279068A1 |

| Преобразователь балансно-модулированных сигналов переменного тока в код | 1986 |

|

SU1349006A1 |

| Регулятор конденсаторной батареи | 1989 |

|

SU1697067A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1341719A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1283968A1 |

| Цифровой вычислитель синуса и косинуса | 1977 |

|

SU682905A1 |

1. ПРЕОБРАЗОВАТЕЛЬ БАЛАНСНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПЕРЕМЕННОГО ТОКА В КОД, содержащий первый и второй умножители, аналоговые входы которых соединены с первым и вторым выходами источника балансномодулированных сигналов, а выходы подключены к первому и второму входам сумматора, выход сумматора последовательно соединен с усилителем, фаэочувствительным выпрямителем, регулятором частоты и реверсивным счетчиком, выходы разрядов -которого подключены к входам блока преобразователя кода в коды косинуса, первый и второй выходы которого подключены к цифровым входам первого и второго умножителей, отличающийся тем, что, с целью повышения точности преобразователя, в него введены k дополнительных умноямтелей, аналоговые входы которых соединены с соответстg вующими выходами источника балансно-модулированных сигналов, цифровые входы соеданены с дополнительными выходами блока щ)еобразова1шя кода в коды косинуса, а вьтходы подп ключены к входам сумматора.

Изобретение относится к автоматике и вычислительной технике и может быть использся ййо в преобразователь угла nOBOpoW вала в код с многофазными датчиками угЛа.

Известен следящий преобразователь балансно-модулированных сигналов переменного тока формата синусно-косинусного вращающегося трансформатора в цифровой сигнал, содержащий последовательно соединенные усилитель, демодулятор с фильтром, интегратор, преобразователь напряжение-частота, реверсивный счетчик, дешифратор и селектор квадранта, первый и второй входы которого являются входами преобразователя, а первый и второй выходы подключены через первый и второй функциональные умножители соответственно к входам усилителя, выход счетчика, являющийся выходом преобразователя соединен также с цифровыми входами первого и второго функциональных умножителей ГЛ .

Недостатком такого преобразовател является его не высокая точность.

Наиболее близким техническим решением к изобретению является преобразователь балаисно-модулированных сигналов переменного тока в код, содержащий первый и второй умножители, аналоговые которых соединены с первым и вторым выходами источника балансно-модулированных сиг налов, а вЫходы подключены к первому и второму входам сумматора, выход сумматора последовательно соединен с усилителем, фазочувствительным вьтрямителем, регулятором частоты и реверсивным счетчиком, выходы разрядов которого подключены к входам блока преобразования кода в коды косинуса, первый и второй выходы которого подключены к цифровым входам первого и второго умножителей 2.

Недостатком известного преобразователя является его невысокая точность.

Цель изобретения - повьш1ение точности преобразователя.

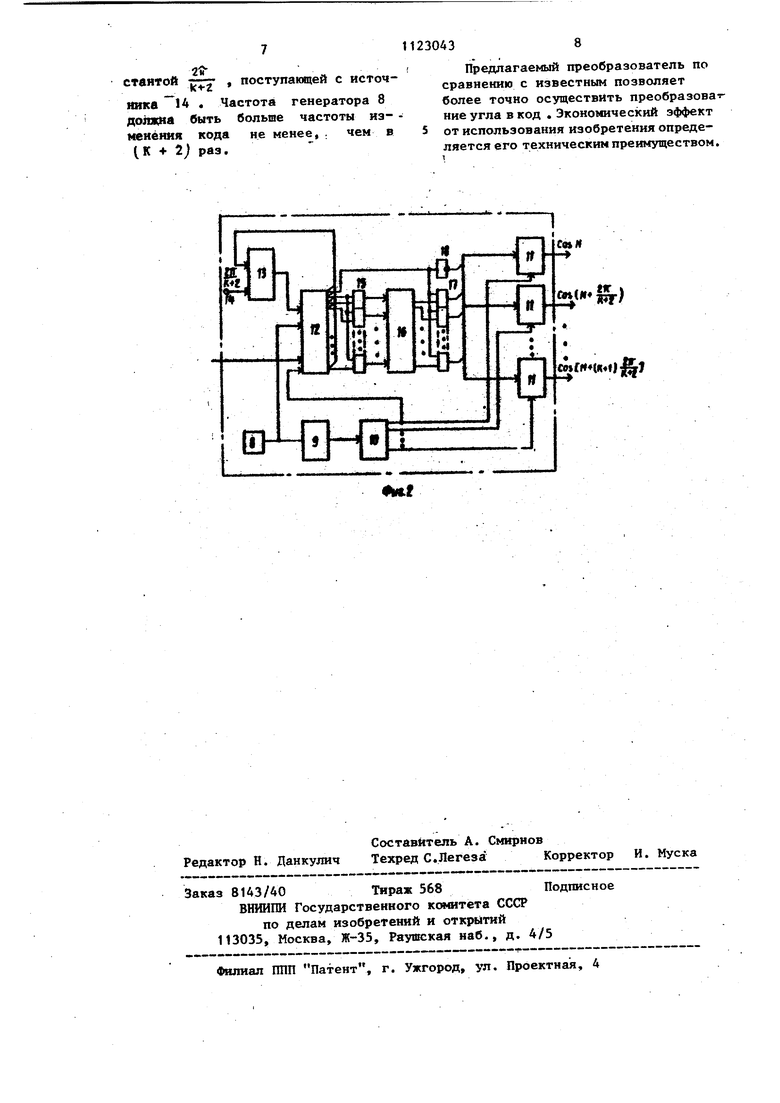

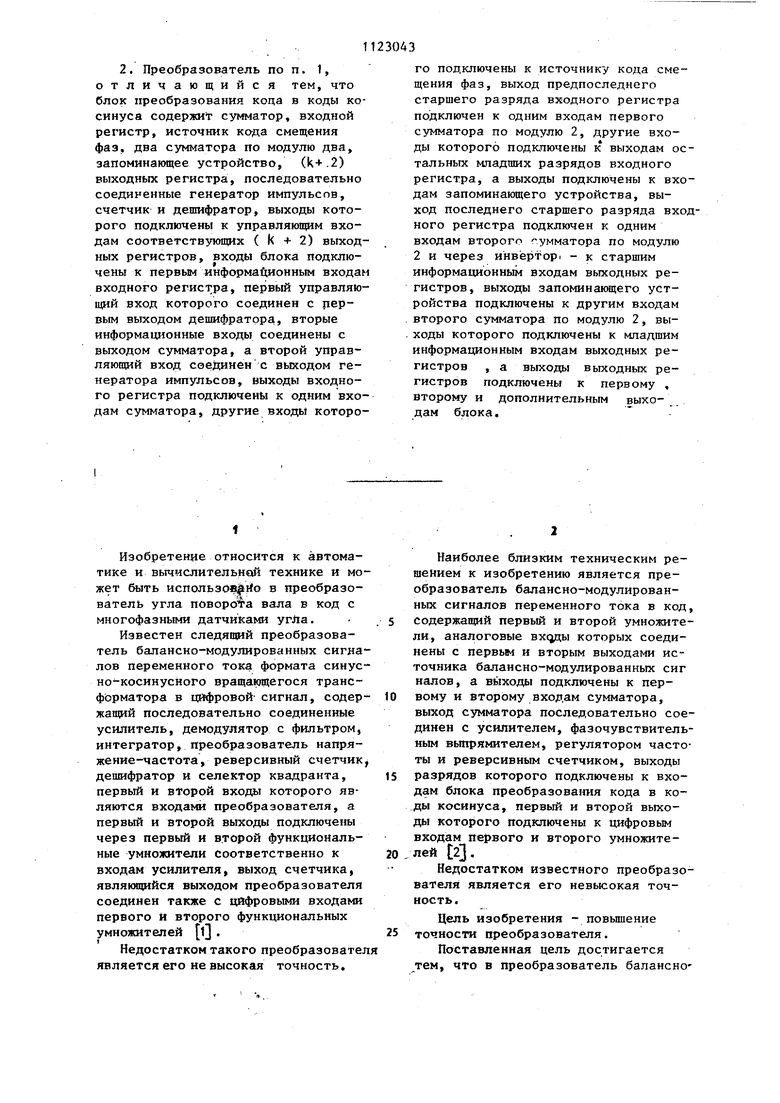

Поставленная цель достигается тем, что в преобразователь балансно модулированных сигналов переменного тока в код, содержащий первый и вто рой умножители, аналоговые входы которых соединены с первым и вторым выходами источника балансно-модулированных сигналов, а выходы подключены к первому и второму входам сумматора, выход сумматора последовательно соединен с усилителем, фазочувствительным выпрямителем, регулятором частоты и реверсивным сче чиком, выходы разрядов которого подключены к входам блока преобразо вания кода в коды косинуса, первый и второй выходы которого подключены к цифровым входам первого и второго умножителей,. введены |{ дополнительных умножителей, аналоговые вхо ды которых соединены с соответствую щими выходами источника балансномодулированных сигналов, цифровые входы соединены с дополнительными выходами блока преобразования кода в коды косинуса, а выводы подключен к входам сумматора. Блок преобразования кода в коды косинуса содержит сумматор, входной регистр, источник кода смещения фаз два сумматора по модулю два, запоминаю.щее устройство, (k + 2) выходных регистра, последовательно соеди ненные генератор импульсов, счетчик и дешифратор, выходы которого подключены к управляющим входам соответствукящх (К + 2) выходных регист ров входы блока подключены к первым информационным входам входного регистра, первый управляющий вход которого соединен с первым выходом дешифратора, вторые информационные входы соединены с выходом сумматора, а второй управляющий вход соеди нен с выходом генератора импульсов, выходы входного регистра подключены к одним входам сумматора, другие входы которого подключены к источнику кода смещения фаз, выход предпоследнего старшего разряда входного регистра подключен к одним входам первого сумматора по модулю 2, другие входы которого подключены к выходам остальных младших разрядов входного регистра, а выходы подключены к входам запоминающего устройства, выход последнего старшего раз ряда входного регистра подключен к одним входам второго сумматора по модулю 2 и через инвертор - к старимм информационньм входам выходных регистров, выходы запоминающего устройства подключены к другим входам второго сумматора по модулю 2, выходы которого подключены к младшим информационным входам выходных регистров, а выходы выходных регистров подключены к первому, второму и дополнительньм выходам блока. На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - блок преобразования кода в коды косинуса. Преобразователь содержит k умножителей t, аналоговые входы которых являются входами преобразователя, последовательно соединенные сумматор 2, усилитель 3, фазочувствительный выпрямитель 4, регулятор 5 частоты и реверсивный счетчик 6, выходы разрядов которого, являющиеся выходами преобразователя, соединены с входами блока 7 преобразования кода в коды косинуса, выходы блока 7 соединены с цифровыми входами соответствующих умножителей 1, выходы которых подключены к входам сумматора 2. Умножитель 1 предназначен для умножения входного аналогового напряжения на код, поступающий с выходов блока 7, результат умножения представлен на выходе умножителей 1аналоговым напряжением. Сумматор 2 предназначен для нахождения суммы аналоговых сигналов с выходов умножителей 1. Сумматор 2и усилитель 3 могут быть реализованы совместно на операционном усилителе . Фазочувствительный вьшрямитель 4предназначен для выделения напряжения пропорционального синусу рассогласования угла 0 и кода N. Регулятор 5 частоты предназначен для формирования последовательности импульсов с соответствующей частотой следования и их знака (импульсы поаются на суммируюа91й или вычитаюпщй входы счетчика 6). В регуляторе 5может быть использована опорная высокая частота (например, с применением кварца) или генератор частоты, управляе1 в11й напряжением рассогласования. Возможна реализация различных законов регулирования (в том числе и пропорционально ин-т теграпьно-дифференциального).

Блок 7 преобразования кода в коды косинуса предназначен для фор, вlpoвaния кодов cos N,

COS («f N + ( + 1)Щ a соответствии с кодом N на выходе реверсивного счетчика 6. Блок 7 преобразования кода в коды косинуса содержит последовательно соединенны генератор 8 импульсов, счетчик 9 и дешифратор 10, выходы которого подключены к управляющим входам соответствующих (К +2) выходных регистров 11, входы блока 7 подключены к первым информационным входам входного регистра 12, первый управляющий вход которого соединен с первым выходом дешифрйтора 10, вторые информационные входы соединены с выходом сумматора 13 а второй управляющий вход соединен с выходом генератора 8 импульсов, выходы входного регистра 12 подключены к одним входам сумматора 13, другие входы которого подключены к источнику 14 кода смещения фаз, предпоследнего старшего разряда входного регистра 12 подключен к одним входам первого сумматора 15 по модулю 2, другие входы которого подключены к выходам остальных младших разрядов входного регистра 12, а выходы подключены к входам запоминающего устройства 16, выход последнего старшего разряда входного регистра 12 подключен к входам второго сумматора 17 по модулю 2 и через инвертор 18 к старшим информационным входам выходных регистров 11, выходы 3anof«fнакядего устройства 16 подключены в другим входам второго cy в aтopa 17 по модулю 2, выходы которого подключены к младшим информащсонным входам регистров 11, выходы регистров 11 подключены к выходам блока 7.

Преобразователь работает следующим образом.

На аналоговые входа умножителей поступает система напряжений

; Uj и„ sin(e6 +

и, Л

ag kti

);

/

Al

- ( k -ь 1)

и

K4ZJ

а на их цифровые входы соответственно поступают коды cos N,

cos (N ), ..., +

-ь ( К + 1) . Умножители 1

формируют систему напряжений U U. + 1(-|тг} °

-firj

Сумматор 2 формирует сигнал, пропорциональный синусу разности угла Об и кода N.

Этот сигнал усиливается усилителем 3. Фазочувствительный выпрямитель 4 выделяет напряжение, пропорциональное sin (сб. - N). Регулятор 5 частоты в зависимости от знака sin ( в6 - N) подает импульсы на су1Фдарующий или вычитающий входы реверсивного счетчика 6, по кеду N которого на выходе блока 7 формируются коды cos N + i r J. Преобразователь будет сбалансирован, если N об . Направление рассогласования определяется рассогласованием угла об н кода N, так как фаза выходного сигнала изменяется на I при изменении знака разности углов.

Блок 7 работает следующим образом. На счетчик 9 поступает тактовая частота с генератора 8, код с вьпсода счетчика 9 поступает на дешифратор 10 При наличии уровня логической 1 на первом выходе дешифратора 10 происходит запись в регис 12 кода N с выходов реверсивного счетчика 6, этот код через сумматор

15по модулю 2 поступает на вход постоянного запоминакнцего устройства 16, в котором записаны коды

cos N для углов 0-90 . Старший разряд кода N используется для инвертирования кода COS N на выходе постоянного запоминакяцего устройства

16при отрицательных значениях функции cos N с помснцью сумматора 17. Ecjm код N соответствует убьтающему участку функции cos N, то предпоследний старший разряд кода N используется для инвертирования кода, поступакицего на вход постоянного запоминающего устройства 16. Код с выхода сумматора 17, а также инвертированный разряд кода N с инвертора 18 поступает на регистры 11, и соответствии с позиционньм кодом навыходе дешифратора 10 осуществляется запись в Соответствующий регистр 11. При каждом импульсе тактовой частоты осуществляется также запись в регистр 12 с выхода сумматора 13 кода, образованного суммирова нием содержимого регистра 12 с кон2-jJ-. .

стантой Г -г- , поступающей с источника 14 , Частота генератора 8 должна быть больше частоты из- меиёния кода не менее, . чем в (К + 2J раз.

Предлагаемый преобразователь по сравнению с известным позволяет более точно осуществить преобразовав ние угла в код . Экономический эффект от использования изобретения определяется его техническим преимуществом.

йпСМ)

(i««OJ 7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вульвет Дж | |||

| Датчики в цифровых системах | |||

| М., Энергоиздат, 1981, с | |||

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Зверев А.Е | |||

| и др | |||

| Преобразователи угловых перемещений в цифровой код | |||

| Л., Энергия, 1974, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1984-11-07—Публикация

1983-07-13—Подача