ИэоЛретение относится к вычислительной технике и может,быть использовано для параллельного вывода определенной части информации с узлов сеточной области (аналоговой ил гибридной) в виде группы узловых напряжений (для аналоговой сеточной области), либо группы двоичных слов (для цифровой сеточной области) и предназначенных для дальйейшей обработки аналоговыми либо цифровыми способами.

Известно устройство для полуавтоматической коммзггации задач на аналоговых вычислительных машинах, содержащее блок входных элементов И, который соединен с дйумя входными регистрами и блоком управления ., Входные регистры пoдкJдачeны к блоку управления и координатным дешифраторам. Выходы одного дешифратора соединены с гнездами сеточной области,а другого - с одним из входов соответствующей схемы совпадения. На вторые входы схемы совпадения поступают сигналы от выходов информационных гнезд сеточной области, выходы координатных дешифраторов связаны также со схемо индикации. Связь между блоксм управ ления и выходами схем совпадения осуществляется через схемы ИЛИ JJ

Наиболее близким к данному изобретению является устройство для коммутагри задач на аналоговых вычислительных машинах, содержащее блок входных элементов И, выходы которых соединены с входами первого и второго входных регистров, выходы которых соединены соответственно с входами первого и второго координатных дешифраторов, выходы первого дешифратора соединены с первыми входами вентилей первой группы, а входы второго координатного дешифратора. соединены с первыми входами вентилей второй группы, выходы каждого вентиля первой и второй групп соединены : управляющими входами соответствуюпрге ключей, информацион ные входы ключей объединены междУ собой и подключены к соответствующим входам управляющего блока цифрового коэффициента, а информационные выходы подключены к соответствующим гнездам сеточной области. Вторые входы вентилей первой и второй групп, входные регистры и

входные элементы И подключены к входам схемы синхронизации 2 .

Недостатком известных устройств является низкое быстродействие изза последовательного опроса узлов сеточной области.

Цель изобретения - повьш1ение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее первый и второй регистры, дешифратор, матрицу, ключей,-информационные входы которых являются входами первой группы устройства, входы первой и второй групп дешифратора соединены соответственно с выходами первого и второго регистров, входы группы которых являются соответственно входами второй и третьей групп устройства, входы первого и второго регистров являются входом устройства, дополнительно введены арифметические блоки, группа дешифраторов, блок памяти, коммутатор и матрица элементов ИЛИ, входы которой соединены с выходами дешифратор и группы дешифраторов, информационн входы дшпифраторов группы соединены с выходами соответствующих арифметических блоков, входы первой и второй групп которых соединены соответственно с выходами первого и второго регистров и входами первой и второй групп блока памяти, входы третьей группы которых соединены со стробирующям входом соответствующег дешифратора группы и являются входами четвертой группы устройства, . выходы блока памяти соединены с входами первой группы коммутатора, выхды которого являются выходами устройства, входы второй группы коммутатора соединены с выходами ключей матрицы, входы второй группы которых соединены с выходами элеменtoB ИЛИ матрицы. .

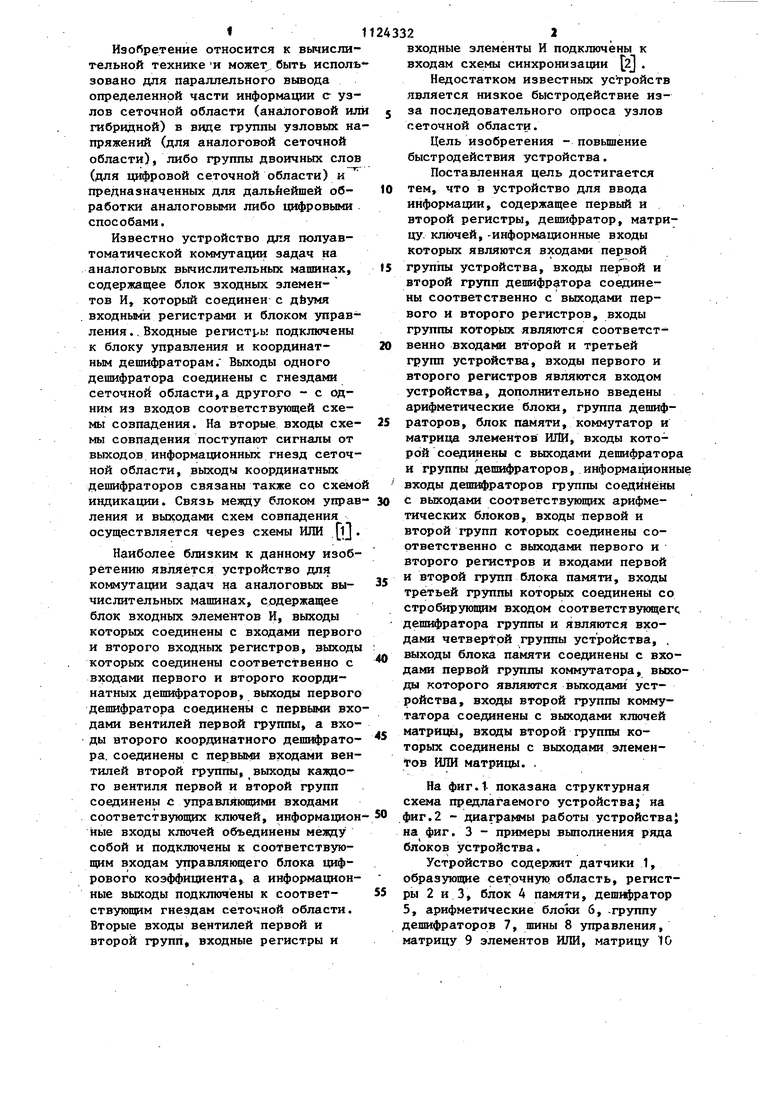

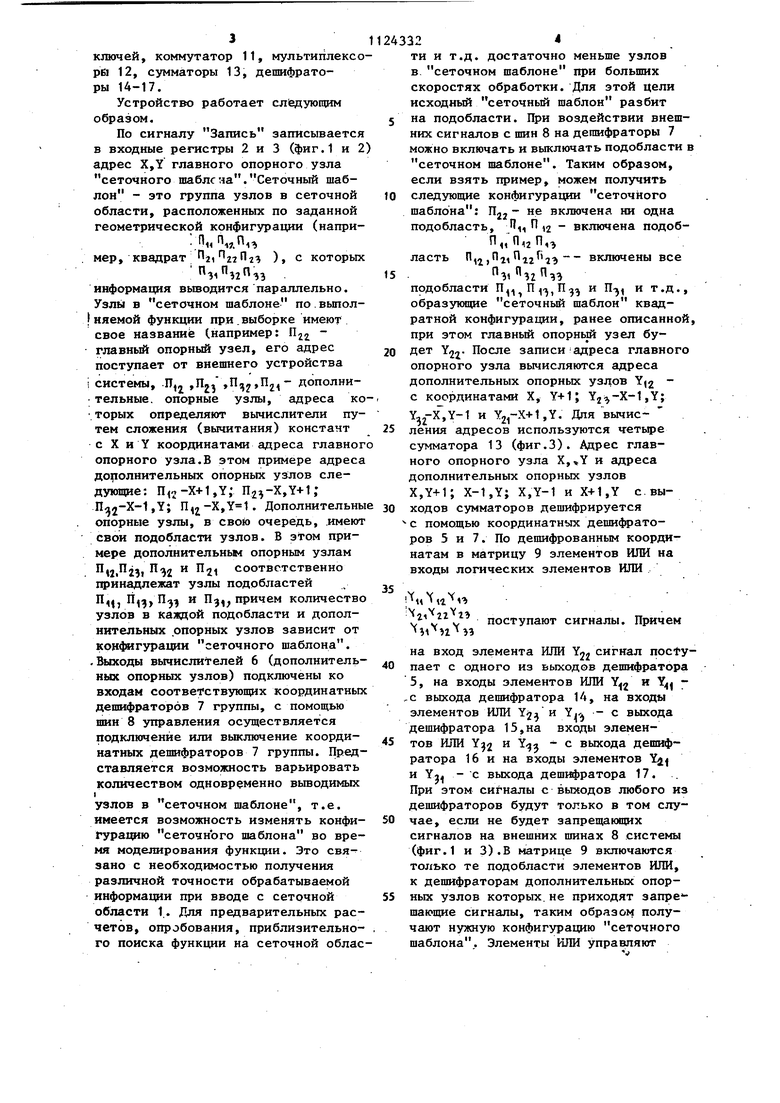

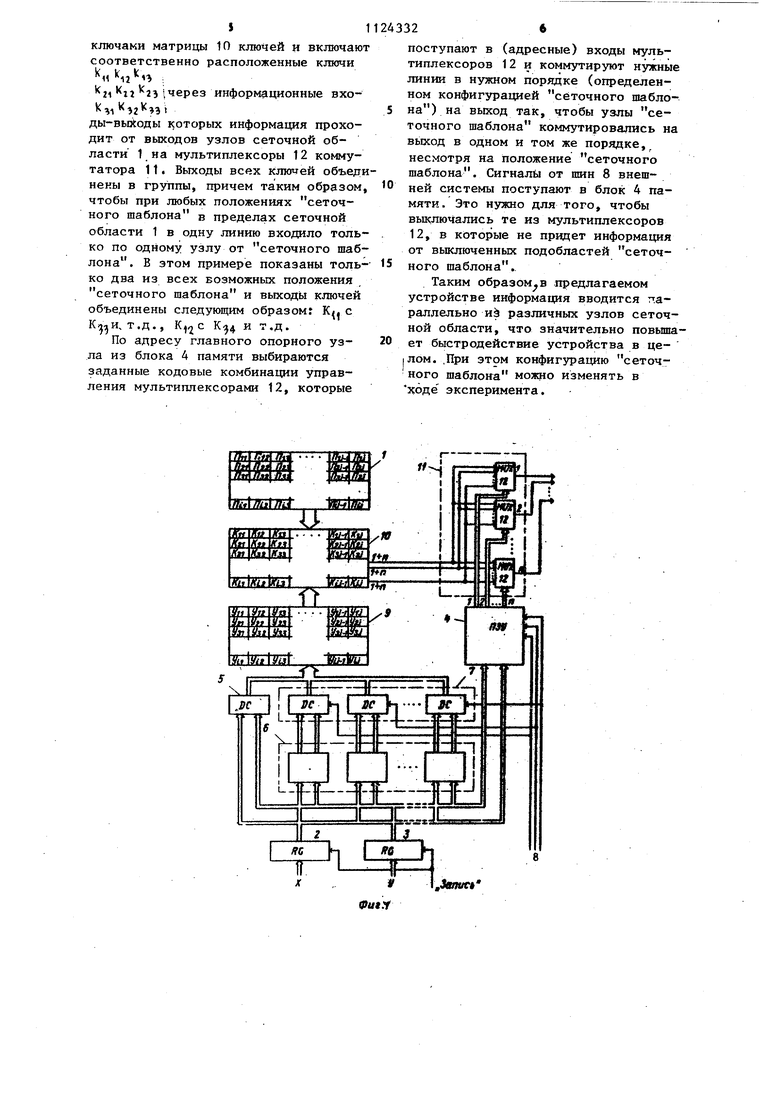

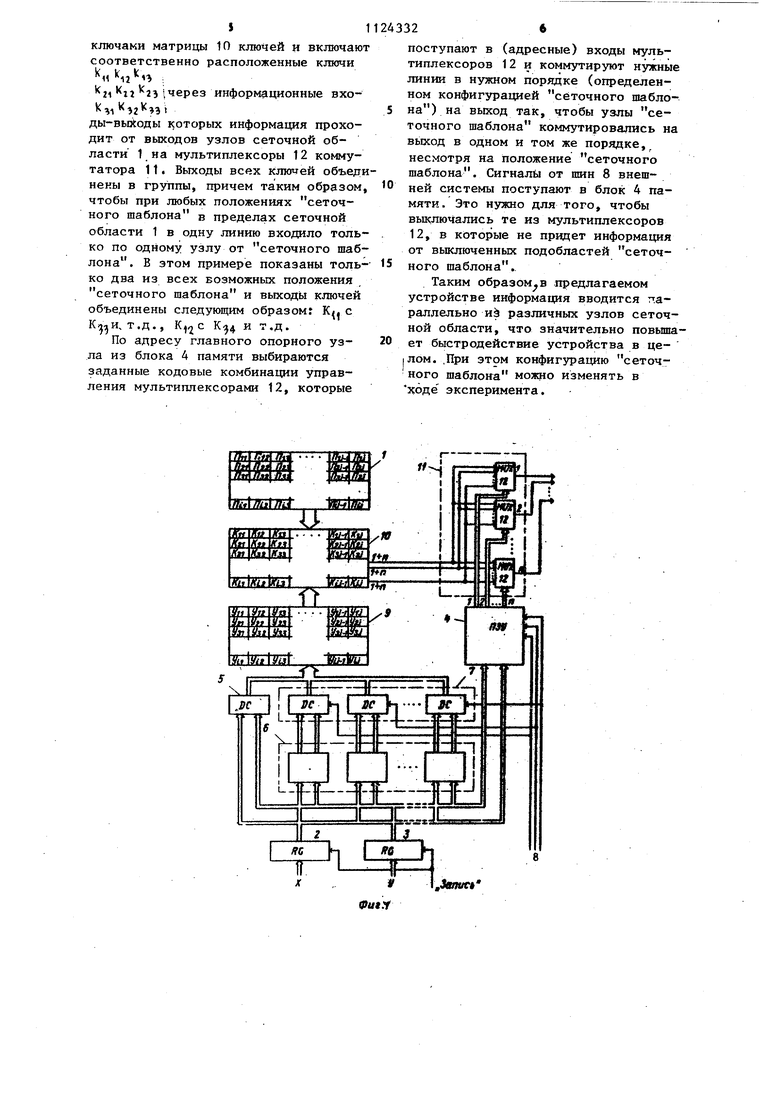

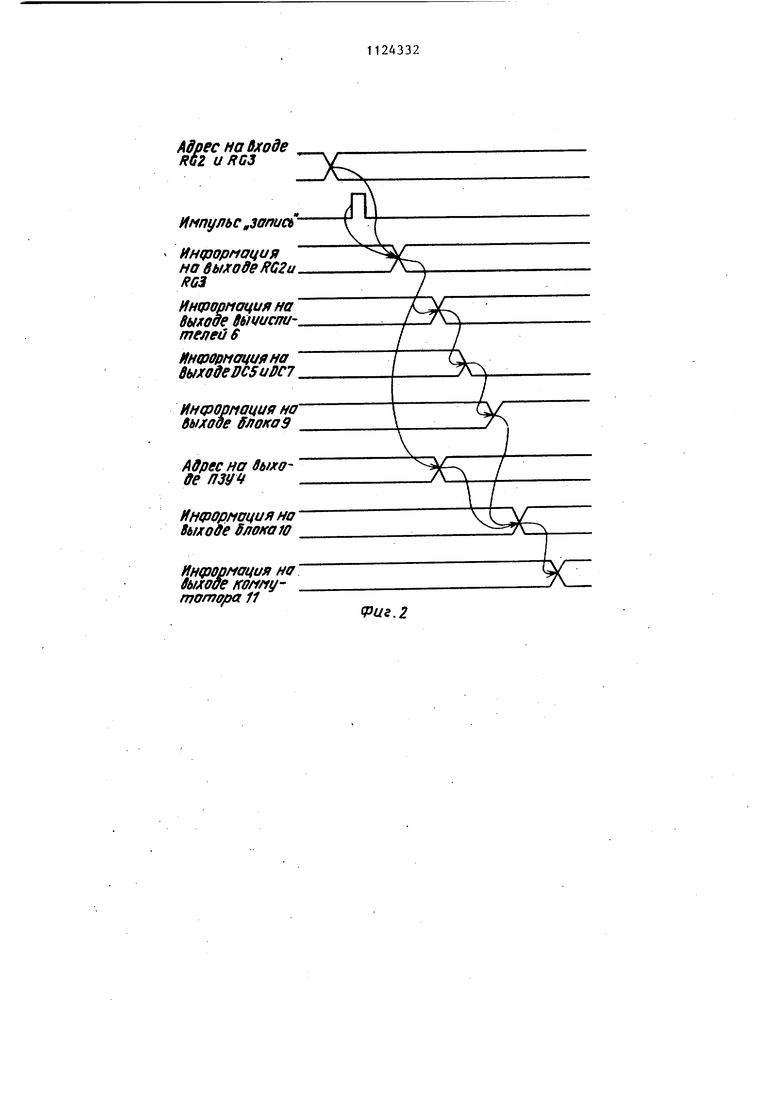

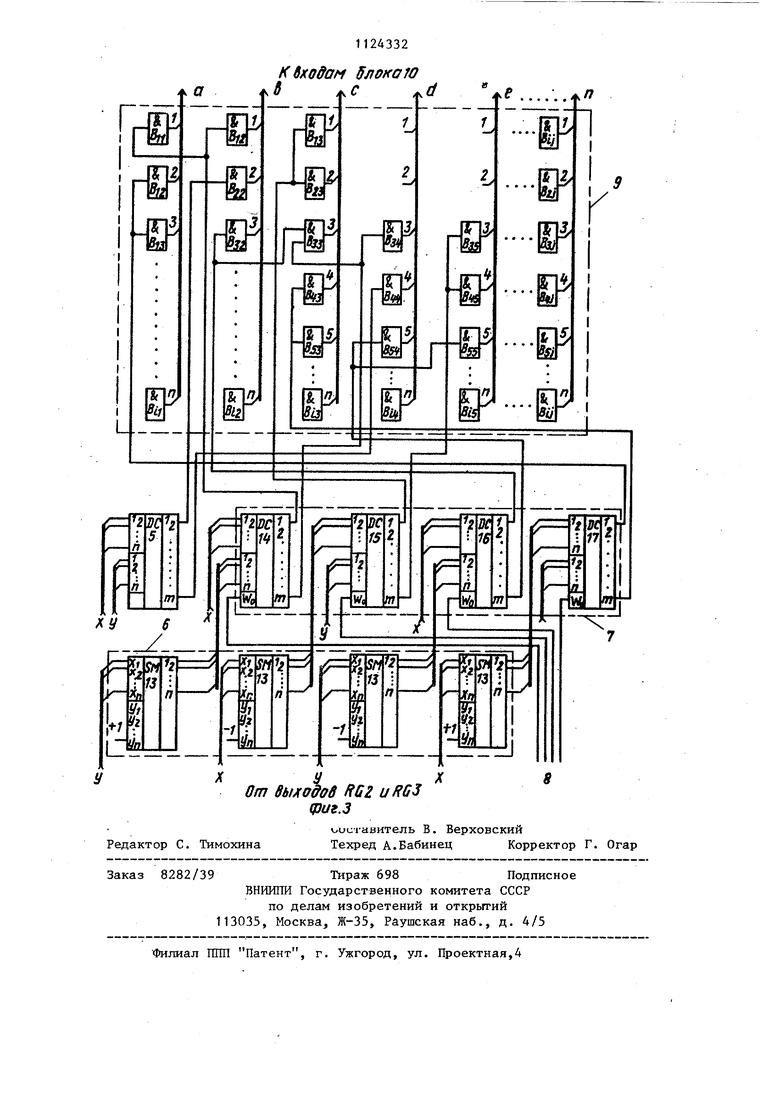

На фиг.1- показана структурная схема предлагаемого устройства; на фиг.2 - диаграммы работы устройства на фиг. 3 - примеры выполнения ряда блоков устройства.

Устройство содержит датчики 1, образующие сетрчнзпо область, регистры 2 и 3, блок 4 памяти, дешифратор 5, арифметические блоки б, -группу дешифраторов 7, шины 8 управления, матрицу 9 элементов ИЛИ, матрицу 10

3

ключей, коммутатор 11, мультиплексорВ1 12, сумматоры 13, дешифраторы 14-17.

Устройство работает следующим образом.

По сигналу Запись записывается в входные регистры 2 и 3 (фиг.1 и 2 адрес X,Y главного опорного узла сеточного шаблс на.Сеточный шаблон - зто группа узлов в сеточной области, расположенных по заданной геометрической конфигурации (напри:П1,п„,п,,

мер, квадрат 2,12(123 ) с которых

Э1 52ПЗЗ информация выводится параллельно.

Узлы в сеточном шаблоне по.вьшолIняемой функции при.выборке имеют свое название (.например: П главный опорный узел, его адрес поступает от внешнего устройства I системы, .n,j, ,П2з ,П:5,П24- дополнительные, опорные узлы, адреса ко торых определяют вычислители путем сложения (вычитания) констант с X и Y координатами адреса главног опорного узла.В этом примере адреса дополнительных опорных узлов следующие: n j-X+1,Y, П2з-Х,У+1, ,У; n,j,-X,. Дополнительны опорные узлы, в свою очередь, .имеют свои подобласти узлов. В зтом примере дополнительньм опорным узлам

W.23i Ъг 21 соответственно принадлежат узлы подобластей n,jj li, П и Пз причем количество узлов в кавдой подобласти и дополнительных .опорных узлов зависит от конфигурации сеточного шаблона. .Выходы вычислителей 6 (дополнительных опорных узлов) подключены ко входам соответствующих координатных дешифраторов 7 группы, с помощью шин 8 управления осуществляется подключение или выключение координатных дешифраторов 7 группы. Представляется возможность варьировать

количеством одновременно выводимых I

узлов в сеточном шаблоне, т.е. имеется возможность изменять конфиГурагщю сеточного шаблона во время моделирования функции. Это связано с необходимостью получения различной точности обрабатываемой информации при вводе с сеточной области 1. Для предварительньпс расчетов, опробования, приблизительного поиска функции на сеточной облас24332

ти и т.д. достаточно меньше узлов в сеточном шаблоне при больших скоростях обработки. Для этой цели исходный сеточный шаблон разбит 5 на подобласти. При воздействии внешних сигналов с шин 8 на дешифраторы 7 можно включать и выключать подобласти в сеточном шаблоне. Таким образом, если взять пример, можем получить 10 следующие конфигурации сеточного шаблона : nj не включена ни одна подобласть, 11,2 - включена подобП„П,2П„ ласть n,,nj, включены все

15 .

подобласти П,. и П, и т.д., образующие сеточный шаблон квадратной конфигурации, ранее описанной, при этом главный опорньй узел бу0 дет После записи адреса главного опорного узла вычисляются адреса дополнительных опорных узлов У(2 с координатами X, У+1; ,У;

,У-1 и У2,-Х+1,У. Для вычис5 ления адресов используются четыре сумматора 13 (фиг.З). Адрес главного опорного узла X,У и адреса дополнительных опорных узлов Х,У+1; Х-1,У; Х,У-1 и Х-|-1,У с.вы0 ходов сумматоров дешифрируется с помощью координатных дешифраторов 5 и 7. По дешифрованным координатам в матрицу 9 элементов ИЛИ на входы логических элементов ИЛИ

,,,lYi,тт

., f поступают сигналы. Причем

на вход элемента ШШ сигнал nocty0 пает с одного из выходов дешифратора 5, на входы элементов ИЛИ У ,с выхода дешифратора 14, на входы элементов ИЛИ УЗ и У - с выхода дешифратора 15,на входы элемен5 тов ИЛИ и - с выхода дешифратора 16 и на входы элементов У и У - с выхода дешифратора 17. . При этом сигналы с выходов любого из дешифраторов будут только в том слу0 чае, если не будет запрещающих

сигналов на внешних шинах 8 системы (фиг.1 и 3)«В матрице 9 включаются только те подобласти элементов ИЛИ, к дешифраторам дополнительных опор5 ных узлов которых.не приходят запре шающие сигналы, таким образом получают нузкную конфигурацию сеточного шаблона. Элементы ИЛИ управляют

V S ключами матрицы 10 ключей и включаю соответственно расположенные ключи м Ili n , 21 Ъ |через информационные вхоК,1 i ды-вьЛоды которых информация проходит от выходов узлов сеточной области 1 на мультиплексоры 12 коммутатора 11. Выходы всех Ключей объед нены в группы, причем таким образом чтобы при любых положениях сеточного шаблона в пределах сеточной области 1 в одну линию входило толь ко по одному узлу от сеточного шаб лона . В этом примере показаны толь ко два из всех возможных положения сеточного шаблона и выходы ключей объединены следующим образом: К с , т.д., и т.д. По адресу главного опорного узла из блока 4 памяти выбираются заданные кодовые комбинации управления мультиплексорами 12, которые 26 поступают в (адресные) входы мультиплексоров 12 и коммутируют нужные линии в нужном порядке (определенном конфигурацией сеточного шаблона) на выход так, чтобы узлы сеточного шаблона коммутировались на выход в одном и том же порядке,, несмотря на положение сеточного шаблона. Сигналы от шин 8 внешней системы поступают в блок 4 памяти. Это нужно для того, чтобы выключались те из мультиплексоров 12, в которые не првдет информация от выключенных подобластей сеточного шаблона. Таким образом в предлагаемом устройстве информация вводится параллельно и различных узлов сеточной области, что значительно повьшиет быстродействие устройства в цеЛом. ,При этом конфигурацию сеточкого шаблона можно изменять в ходе эксперимента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для съема информации с сеточной электромодели | 1980 |

|

SU962985A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЩШ, содержащее первьп : и второй регистры, дешифратор, матрицу ключей, информационные входы которых являются входами первой группы устройства, входы первой и второй групп дешифратора соединены соответственно с выходами первого и второго регистров, входы группы которых являются соответственно входами второй и третьей групп устройства, входы первого и второго регистров являются входом устройства, отлича-ющееся тем, что, с целью повьшения быстродействия устройства, в него введены арифметические блоки, группа депифраторов, блок памяти, коммутатор и матрица элементов ИЛИ, .входы которой соединены с выходами дешифратора и группы дешифраторов, информационные входы дешифраторов группы соединены с выходами соответствующих арифметических блоков, входы первой и второй групп которых соединены соответственно с выходами первого и второго регистров и входами первой и второй групп блока памяти, входы третьей § группы которого соединены со стробирующим входом соответствующего дешифратора группы и являются входами четвертой группы устройства, выходы блока памяти соединены с входами первой группы коммутатора, выходы которого являются выходами устройства, входы второй группы коммутатора соединены с выходами ключей матрицы, входы второй группы которых соединены с выходами элементов ИЛИ матрицы. Ю 9 :о N5

-ТУ.Г/Ч .Г/Л

Адрес на бходе

и ясз

Импульс „запись

Информация на выходе КС2и RG3

Нн(рорпация на бшоие etivt/cm-. т ел ей $

Мнфоцнацийна выходе ffcs иffC7

Инфорпация на быхоое ВлокаЭ

Адрес на выходе nsyff

Информация на Выходе блока 10

Информация на выходе коммутатора 11

(Pus. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для полуавтоматической коммутации задач на аналоговых вычислительных машинах | 1973 |

|

SU446068A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-07—Подача