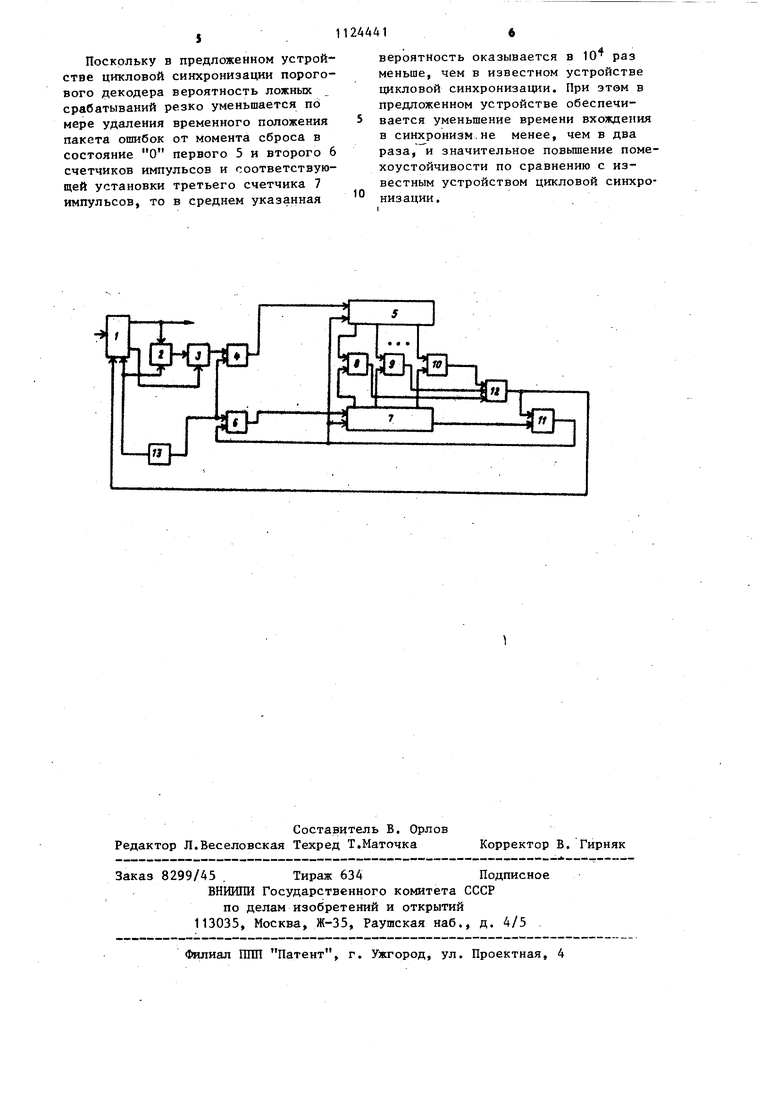

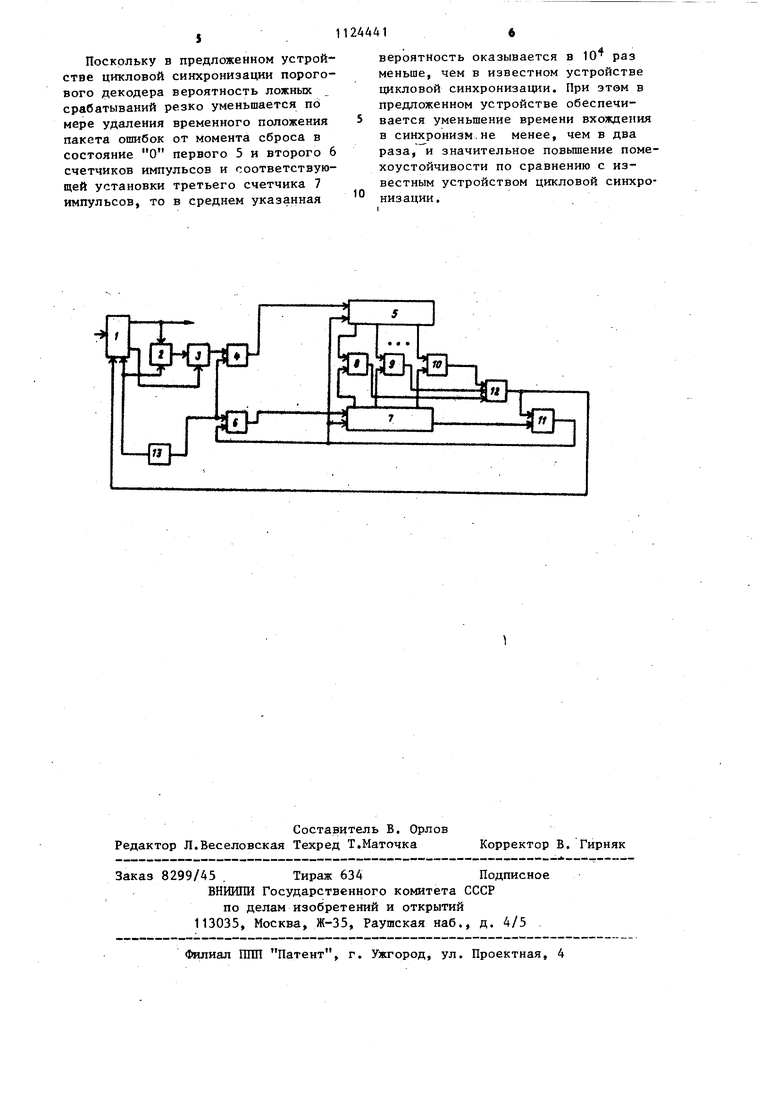

Изобретение относится к электросвязи и может быть использовано гля цикловой синхронизации в системах передачи данных и в цифровом радио и телевизионном вещании при использевании сверхточного кодирования и порогового декодирования информационных сигналов. Известно устройство цикловой син хронизации, содержащее последовательно соединенные запрещающий блок коммутатор, ключи, блок для обнаружения ошибок и блок для исправления ошибок, последовательно соединенные формирователь тактовых импульсов, счетчик объема выборки, формирователь импульсов установки нуля, элемент ИЛИ, пороговый 4:четчик., тригге и формирователь запрещающих импульсов, выход которого подсоединен к входу запрещающего блока, другой вход которого подключен к выходу формирователя тактовых импульсов, другой вход порогового счетчика под ключен к второму выходу блока для обнаружения ошибок, а второй вход триггера подсоединен к выходу элемента ИЛИ Л . Недостатком такого устройства ци ловой синхронизации является большо время вхождения в синхронизм. Наиболее близким к предложенному по техническому решению является ус ройство цикловой синхронизации, содержащее последовательно соединенны формирователь тактовых импульсов, коммутатор, формирователь проверочной последовательности, формирователь синдромной последовательности, элемент совпадения и первый счетчик импульсов, а также второй счетчик импульсов, причем второй выход коммутатора .подсоединен к другому вход формирователя синдромной последовательности, а второй вход и первый выход коммутатора явЬяются соответс венно входом и выходом устройства, выход первого счетчика импульсов через формирователь запрещающих сиг налов подсоединен к третьему входу доммутатора, выход второго счетчика импульсов подсоединен к установочному входу счетного триггера и к объединенным вторым входам первого счетчика импульсов и формирователя запрещакмцих сигналов, прямой выход счетного триггера через дополнитель ный элемент совпадения и формирователь иремспного интбовала перезаписи подсоединен к счетному входу счетного триггера, инверсный вьгход которого подсоединен к другому входу элемента совпадения, а второй вход дополнительного элемента совпадения подключен к выходу формирователя тактовых импульсов 2j . Недостатком известного устройства цикловой синхронизации является большое время вхождения в синхронизм. Цель изобретения - уменьшение времени вхождения в синхронизм и повьштение помехоустойчивости. Поставленная цель достигается тем, что в устройство цикловой синхронизации порогового декодера, содержащее последовательно соединенные формирователь тактовых импульсов, коммутатор, формирователь проверочной последовательности, формирователь синдромной последовательности, элемент совпадения и первый счетчик импульсов, а также второй счетчик импульсов,причем второй выход коммутатора подсоединен к другому входу формирователя синдромной последовательности, а второй вход и первый выход коммутатора являются соответственно входом и выходом устройства, введены последовательно соединенные третий счетчик импульсов и первый элемент Ш1И-НЕ, а также второй элемент ИЛИ-НЕ и сумматоры по модулю два, при этом выход второго злемен- та ИЛИ-НЕ подсоединен к второму входу первого элемента ИЛИ-НЕ и третьему входу коммутатора, первые входы сумматоров по модулю два подключены к соответствующим выходам первого счетчика импульсов, вторые входы сумматоров по модулю два подключены к соответствующим выходам третьего счетчика импульсов, а выходы сумматоров по модулю два подсоединены к входам второго элемента ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ подсоединен к второму входу первого счетчика импульсов и к объединенным входам второго счетчика импульсов и третьего счетчика импульсов, второй вход которого подключен к выходу второго счетчика импульсов, дополнительный вькод формирователя тактовых импульсов подсоединен к объединенным вторым входам элемента совпадения и второго счетчика импульсов, а другой вход формирователя проверочной последовательности подключен к выходу формирователя тактовых импульсов . Ча чертеже представлена структур ная электрическая схема устройства цикловой синхронизации порогового декодера. Устройство цикловой синхронизаци порогового декодера содержит коммутатор 1, формирователь 2 проверочной последовательности, формирователь 3 синдромной последовательности, элемент А совпадения, первый 5, второй 6, третий 7 счетчики импульсов, сумматоры 8-10 по модулю два, первый 11 и второй 12 элемент ШТИ-Н и .формирователь 13 тактовых импульсов. Устройство цикловой синхронизаци порогового декодера работает следую щим образом. Входная кодовая последовательность в коммутаторе 1 разделяется на информационную и проверочную последовательности. Символы информа ционной последовательности одновременно поступают на вход формирователя 2 проверочной -последовательнос ти, где из принятых информационных символов формируется проверочная последовательность, которая поступа ет на вход формирователя 3 синдромной последовательности, на другой вход которого с коммутатора 1 посту пает входная проверочная последовательность. На выходе формирователя синдромной последовательности произ водится формирование синдромной последовательности (СП). При наличи цикловой синхронизации ветвей коммутатора 1 и при отсутствии ошибок в информационной и проверочной последовательностях формируется нулевая .СП, а при наличии ошибок или от сутствии цикловой синхронизации фор мируется ненулевая СП. Однако струк тура ненулевых символов в том и в другом случаях имеет разньй характе при наличии только ошибок структура ненулевых символов соответствует структуре используемых порождающих полиномов, а при отсутствии циклово синхронизации структура ненулевых с вопов СП носит случайный характер, а количество их больше, чем при наличии ошибок. Сформированная СП через элемент 4 совпадения поступает на вход первого счетчика 5 импульсов. При большом числе ненулевых символов СП приводит к быстрому за- , полнению первого счетчика 5 импульсов, потому что скорость нарастания двоичного кода в первом счетчике5 импульсов оказывается значительно больше скорости нарастания двоичного кода порога в третьем счетчике 7 импульсов. В результате этого в какой-то момент времени происходит Сравнение этих двоичных кодов, и на всех выходах сумматоров 8-10 по модулю два появляются логические нули (низкий потенциал), обеспечивающий формирование на выходе первого элемента ИЛИ-НЕ 11 сигнала 1, по которому происходит сдвиг ветвей коммутатора 1 на один разряд и через второй элемент ИЛИ-НЕ 12 сброс первого счетчика 5 импульсов и второго счетчика 6 импульсов в состояние О, а также установка третьего счетчика 7 импульсов в состояние, соответствующее начальному значению величины порога. Указанные операции повторяются до тех пор, пока не осуществится правильное распределение ветвей коммутатора 1. В этом случае число ненулевых символов СП резко уменьшается (до величины ненулевых символов исправляемых ошибок), и заполне- , ние первого счетчика импульсов 5 осуществляется со скоростью, значительно меньшей, чем скорость заполнения третьего счетчика 7 импульсов, в результате чего не достигается {равенство двоичных кодов и не осуществляется сдвиг ветвей коммутатора 1. Если при наличии синхронного состояния коммутатора 1 происходит срыв синхронизма из-за воздействия помех, то двоичный код, формируемый первым счетчиком 5 импульсов, быстро достигает порогового уровня, формируемого третьим счетчиком 7 импульсов и начинается вновь процесс установления цикловой синхронизации. Так как при возникновении больших пакетов ошибок в СП формируется большое количество ненулевых символов, что приводит к быстрому росту числа ненулевых символов СП, записанных в третий счетчик 7, то в зависимости от величины пакета ошибок и его временного положения возможны ложные срабатьшания, приводящие к циклу поиска.

Поскольку в предложенном устройстве цикловой синхронизации порогового декодера вероятность ложных срабатываний резко уменьшается по мере удаления временного положения пакета ошибок от момента сброса в состояние О первого 5 и второго 6 счетчиков импульсов и соответствующей установки третьего счетчика 7 импульсов, то в среднем указанная

вероятность оказывается в Ю раз меньше, чем в известном устройстве цикловой синхронизации. При этом в предложенном устройстве обеспечивается уменьшение времени вхождения в синхронизм.не менее, чем в два раза/ и значительное повьш1ение помехоустойчивости по сравнению с известным устройством цикловой синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство цикловой синхронизации порогового декодера | 1987 |

|

SU1483661A2 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1981 |

|

SU1008921A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ ПОРОГОВОГО ДЕКОДЕРА, содержащее последовательно соединенные формирователь тактовых импульсов, коммутатор, формирователь проверочной последовательности, формирователь синдромной последовательности, элемент совпадения -и первый счетчик импульсо, а также второй счетчик импульсов, причем второй выход коммутатора подсоединен к другому входу формирователя синдромной последовательности, а второй вход и первый выход коммутатора являются соответственно входом и выходом устройства, отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм и повьипения помехоустойчивости, в устройство введены последовательно соединенные третий счетчик импульсов и первый элемент ИЛИ-НЕ, а также второй элемент ИЛИ-НЕ и сумматоры по модулю два, при этом выход второго элемента ИЛИ-НЕ подсоединен к второму входу первого элемента ИЛИ-НЕ и третьему входу коммутатора, первые входы сумматора по модулю два подключены к соответствукяцим выходам первого счетчика импульсов, вторые входы сумматоров по модули два подключены к соответствующим выходам третьего счетчика импульсов, а выходы сумматоров по модулю два подсое§ динены к входам второго элемента ИЛИ-НЕ, выход первого элемента ШШ-НЕ подсоединен к второму входу первого счетчика импульсов и к объединенным входам второго счетчика импульсов и третьего счетчика импульсов, второй вход которого подключен к выходу второго счетчика импульсов, дополнительный выход формирователя тактовых импульсов подсоединен к объединенным вторым входам элемента совпадения и BTOiporo счетчика импуль- сов, а другой вход формирователя проверочной последовательности подключен к выходу формирователя тактовых импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1974 |

|

SU496690A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1981 |

|

SU1008921A1 |

Авторы

Даты

1984-11-15—Публикация

1983-05-26—Подача