Изобретение относится к электросвязи и может быть использованр для цикловой синхронизации в аппаратуре повышения достоверности передачи данных при двоичном сверточном кодировании

Известно устройство для цикловой синхронизашш при двоичном сверточном кодировании, содержащее последовательно соединенные запрещающий блок, коммутатор, ключи, блок для. обнаружения ошибок, блок, для исправления ошибок, а также последовательно соединенные бдок формирования тактовых импульсов, выход которого соединен с первым входом запрещающего блока, счетчик объема выборки, формирователь импульсов, установки нуля, элемент ИЛИ, пороговый счетчик, триггер и формирователь запрещающих импульсов, выход которого соединен с вторым входом запрещающего блока Lll .

Однако известное устройство имеет сравнительно большое время вхождения в сйлкронизм..

Цель изобрете1шя - сокращение вр Meiffl вхождени. в синхронизм.

Поставленная цель достигается тем, что в устройство введены блоки совпадения, счетный триггер и формирователь временного интервала перезаписи информации, при этом вы.ход формирователя синдромной последовательнооти соединен с первым в.ходом первого блока совпадения, выход которого через пороговый счетчик соединен с первым входом формирователя запрещак ШИ.Х сигналов, второй в.ход которого объединен с другим входом порогового счетчика и установочным входом счетного триггера « подключен выходу счетчика объема выборки, выход формирователя запрещающих сигналов соединен с управляющим входом коммутатора, а прямой выход счетного триггера соединен с первым входом второго блока совпадения, второй вход которого подключен к выходу формирователя тактовых импульсов, выход

-второго блока совпадения через формирователь временного интервала перезаписи информации соединен со счетным входом счетного триггера, инвероный выход которого соединен с вторым входом первого блока совпадения.

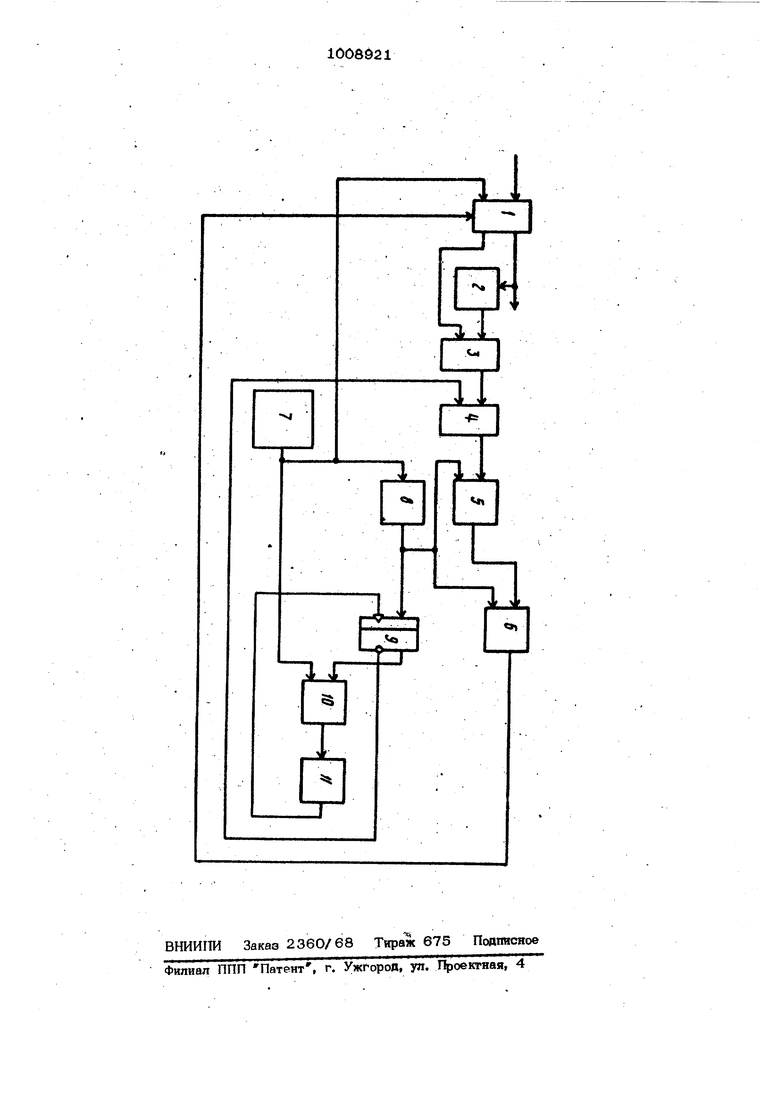

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит коммутатор 1, формирователь 2 проверочной последовательн,ости, формирователь 3 синдромиой последовательности, первый биок-4 совпадения пороговый счетчик 5 рователь 6 запрещающих сигналов, фо1 мирователь 7 тактовых импульсов, счеа . чик 8 фбъема выборки, счетный триггер 9, второй блок 10 совпадения, и формирователь 11 временного интервала .перезаписи,

Устройство работает следующим о&разом.

Входная кодовая последовательность разделяется в коммутаторе. 1 на инфор-. мационную. и проверочную последовательности. Символы информационной последовательности следуют на вход формирователя, .который вьфабатывает из ЭТИХ,сигналов проверочную последоватвльност.ь. Последняя совместно

Q с проверочной последовательностью,

снимаемой с соответствующего выхоjfla коммутатора 1, поступает на два входа формирователя 3, формирующего синдромную последовательность путем

J сравнения указанных последовательностей символов по модулю 2, Вид синдромной последовательности зависит как от установления цикловой синхронизации,так и от наличия ошибок в информашюнной п)следовательт

JJ ности. При установлении цикловой синхронизаши и отсутствии ощибок формируется нулевая синдромная последовательность. Во всех других случаях формируется ненулевая синдромная пооледовательность, причем в случаях отсутствий цикловой синхронизашш (,при наличии или отсутствии ошибок в информационной последовательности) количество ненулевых символов в синдромной после- довательности значительно превышает их количество по сравнению со случаем, когда цикловая синхронизация установлена и присутствуют . ощибки в инфорцмационной последовательности,

Синдромная последовательность ч& рез первый блок 4 совпадения поступает на вход порогового счетчика 5, на другой вход которого следуют импульсы с выхода счетчика 8 объема выборки. Если по окончании времени

анализа синдромной последовательности, определяемого периодом следования импульсов с выхода счетчика 8, на выходе порогового счетчика 5 отсутствует импульсный сигнал,

5 то формирователь 6 не вырабатывает СИГН4/1, запрещающий прохох денне тактовых импульсов, поступающих с выхода формирователя 7 тактовых импульсов на вход коммутатора 1, Этот случай соответствует наличию оякповой синхронизации. Есш1 по окончании времени анализа число ненулевых символ ж сищфомной последовательно сти превысит выбранную пороговую величину, то на выходе счет чнка 5 появится импульснь1й сигнал. Под действием последнего.в формирог вателе 6 вырабатывается зап ещаюпшй сигнал (совпадаюишй по-фазе с выходным импульсным с-лгналом счетчика 8 объема выборки), который препятствует: прохождению одного импульса указанной последсеатедьности тактовых импульсов на вход коммутатора 1. Запрет тактовых импульсов щшводит к сдвигу по фазе принимаемой информации в кетлмутаторе 1, в результате чего обеспечивается цикловая синхронизаиия декодера. Импульсы с выхода Счетчика 8 объе ма выборки поступают также на устано.вочный вход счетного триггера 9, уста навливая его в состояние 1. При . этом сигналом с лнверсного выхода счетного триггера 9 запирается блок 4 совпадения, прекращая тем самым поступ ление синдромной последовательности , на вхйд Порогового счётчика 5, а сигна лом с прямого выхода счетного триггера 9 отпирается блок 1О совпадиния ,и тактовые импульсы с выхода зрмироват&ия 7 тактовых импульсов следуют на вход формирователя 11 1 214 временного интервала перезаписи инфо| машга. На выходе последнего вьфабатываеФ ся импульсный сигнал, задержанный по отношению к входному сигналу наинтервал времени, требуемый для перезаписи информашш в регистре формирователя 2-проверочной комбинации после очередного запрета тактового импул: са в кокшутаторе 1. Импульс с выхода формирователя 11 переводит счетнь1й триггер 9 в исходное состояние . При этом запирается блок 10,. совпадения прекращая тем самым посту- ппение тактовых импульсов на вход формирователя 11 временного интервала перезаписи информашш, а также отпирается блок 4 совпаления пропуская на вход Порогового счетчика 5 синдромную носледовательность. В предлагаемом устройстве за счет преткращения поступления синдромной последовательности на вход порогового счетчика 5 в течение времени перезаписи ин- фсфмашш в регистре формирователя 2 проверочной последовательности, обеспечивается уменьщение числа ненулевых символов синдромной последовательное-. ти, образованных за счет памяти формирователя 2. При этом уменьшается вероятность пропуска момента сфази- рования цикловой синхронизации декодера, благодаря чему сокращается вр&мя вхождения в синхронизм.

т1

CzJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| Устройство для цикловой синхронизации порогового декодера | 1983 |

|

SU1124441A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство цикловой синхронизации порогового декодера | 1987 |

|

SU1483661A2 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

УСТРОЙСТВО .ДЛЯ ЦИКЛОи ВОЙ СИНХРОНИЗАЦИИ ПРИ ДВОИЧНОМ СВЕРТОЧКОМ КОДИРОВАНИИ, содержащее последовательно соединенные коммутатору формирователь проверочной последовательности, формирователь синдромной последовательности, к друг« му входу которого подключен другой выход коммутатора, а также пороговый счетчик, формирователь запрещающих сигналов и счетчик объема выборки, вход которого объединен с соответст вующим входом коммутатора и подклю- чей к выходу формирователя тактовых импульсов, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, в него введены блоки совпадения,счетный триг гер и формирователь временного внтер вала перезаписи информации, при этом выход формирователя сшшрся ной пооледовательности соединен с первым БХ.ОПЯМ первого блока совпадения, выход которого через пороговый счетчик соединен с первым входом формирователя запрещающих сигналов, второй вход котсфого объединен с другим входом порогового счетчика я установочным входом счетного триггера и nof ключен к выходу счетчика объема выборки, выход формирователя защ е1цак щих сигналов соедини с управляющим входом коммутатора, а прямой выход S счетного тригг а соединен с первым входетл второго блока совпадения, вто-, рой вход которого подключен к выходу формирователя.- тактовых импульсов , выход второго блока совпадения через формирователь временного интер- . вала перезаписи информации соединен со счетным вход ом счетного триггера, .инверсный выход которого соединен с X) вторым входом первого блока совпа;о -дения. Nd

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1974 |

|

SU496690A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-03-30—Публикация

1981-04-17—Подача