Изобретение относится к автоматике .и вычислительной технике н может быть использовано как входное устройство в цифровых вычислительных машинах,

Известно устройство многоканального приема и накопле юя дискретной информации, содержащее блок накопления, блок.- сопряжения с датчиками, выход которого соединен с первым вхо дом блока местного управления, причем два входа блока сопряжения с датчиками соединеш с входаьш устрой ства, второй вход и второй выкод бло ка местного управления соединаны соответственно с третьим входом и управляющим выходом устройства Ll.

Недостаток устройства - большие аппаратурные затраты, значительно возрастающие с увеличением числа подключаемых датчиков,

Наиболее близким к предлагаемому является устройство для ввода информации, содержащее приемньш регистр, входной коммутатор, выходной коммутатор, .тор и регистры по- числу подключаемых датчиков, причем информационный выход приемного регистра соединен с информационным входом входного коммутатора, информационные входы сумматора соединены соответственно с выходами входного коммутатора и выходного коммутатора, информационные входы которого соединены с выходами регистров, информационные входы которых соединены с выходом сумматора и информационным выходом устройства, первый вход приемного регистра соединен с выходом блока сопряжения с датчиками, управляющие входы приемного :регистра, входного и выходного коммутаторов, сумматора и регистров соединены с первым выходом блока местного упрарлен-ия, второй выход которого является управляющим выходом устройства, а вход соединен с выходом блока сопрялсения с датчиками 23«

Недостаток устройства - низкое, быстродействие, что не позволяет применять его для ввода сигналов высокой частоты либо для ввода низкочастотных сигналов, но с большого числа Датчиков,

Цель изобретения повьппение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее регистр, ком269А5I

мутатор и блок управления, выходы первой группы которого соединены с входами первой группы коммутатора, введены счетчик, мультиплексор, групJ. па счетчиков и блок памяти; входы счетчиков группы-являются входами устройства, первые выходы счетчиков группы соединены с входами первой группы регистра, входы второй груп JQ пы которого соединены с выходами группы коммутатора, входы второй группы которого соединены с выходами регистра, выходы первой группы блока управления соединены с входами первой группы мультиплексора, вхо- . Ды второй группы которого соединены с вторыми выходами счетчиков группы, вход коммутатора соединен с третьим выходом блока управления, первый выход которого соединен с зходо-м мультиплексора и является управляющим выходом устройства, выход коммутатора соединен с входом счетчика, выходы группы которого соединены с входами второй группы блока памяти и являются информационными выходами группы устройства, выходы второй группы блока управления соединены с входами первой группы блока- памяти и являются адресными выходами устройства, первый вход блока памяти соединен с четвертым выходом блока управления, второй выход которого соединен с вторым входом блока памяти, выходы группы которо5. го соединены с входами группы счетчика, выход мультиплексора является информационным выходом устройства, при этом блок управления содержит счетчик адресов, дешифратор, первый,

0 второй, третий и четвертый элементы задержки, генератор импульсов, выход которого соединен с входом счетчика адресов и входом первого элемента задержки, выход которого

5 соединен с входом второго элемента

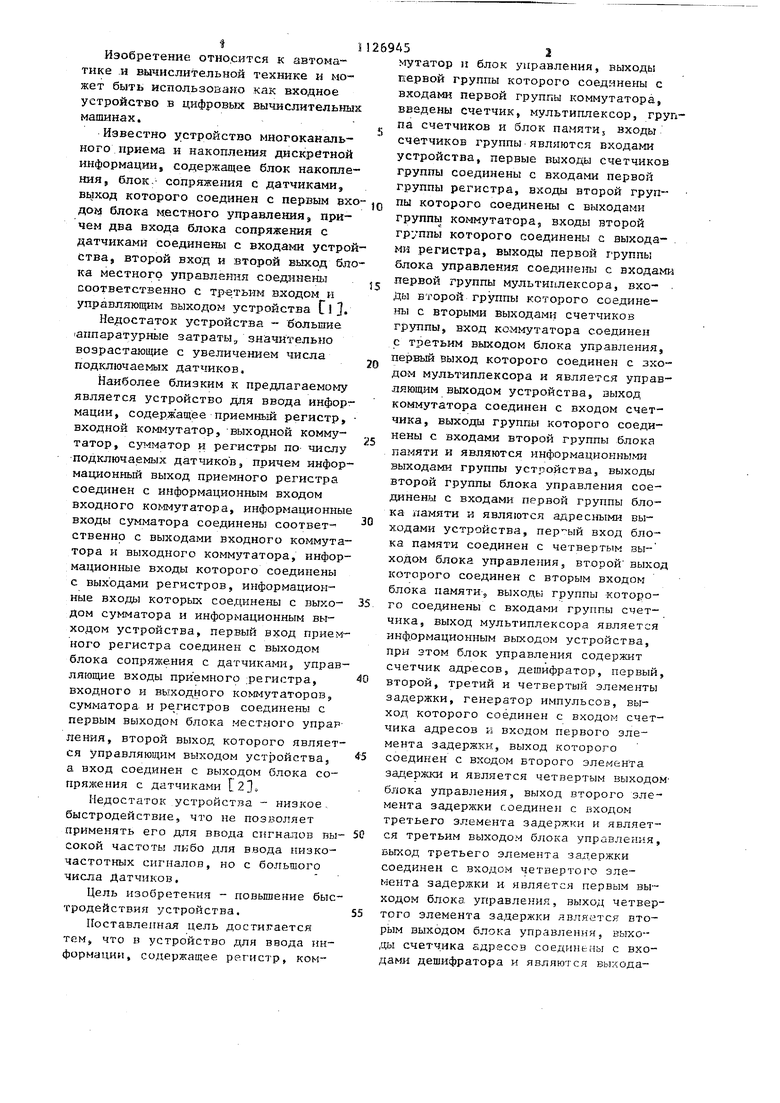

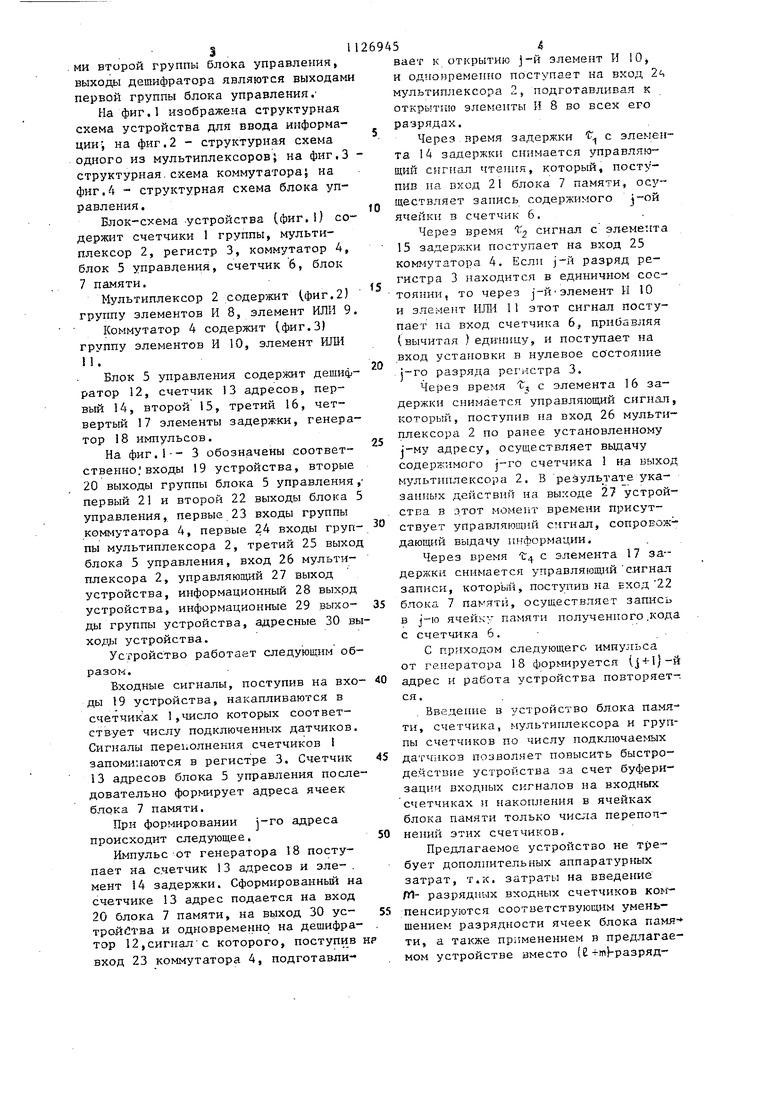

задержки и является четвертым выходоМ блока управления, выход второго злемента задержки соединен с входом третьего элемента задержки и являет0 ся третьим выходом блока -управления, выход третьего злемента задержки соединен с входом четвертого элемента задержки и является первым выходом блока управления, выход четвер5 того элемента задержки является вторым выходом блока управления, выхода счетчика ацресов соединены с входами дешифратора и являются выходами второй группы блока управления, выходы дешифратора являются выходам первой группы блока управления . На фиг,1 изображена структурная схема устройства для ввода информации, на фиг,2 - структурная схема одного из мультиплексоров; на фиг,3 структурная.схема коммутатора; на фиг,4 - структурная схема блока управления . Блок-схема устройства (фиг.I) со держит счетчики 1 группы, мультиплексор 2, регистр 3, коммутатор 4, блок 5 управления, счетчик 6, блок 7 памяти. Мультиплексор 2 содержит (фиг,2) группу элементов И 8, элемент ИЛИ 9 Коммутатор 4 содержит (фиг,3) группу элементов И 10, элемент ИЛИ П, Блок 5 управления содержит дешиф ратор 12, счетчик 13 адресов, первый 14, второй 15, третий 16, четвертый 17 элементы задержки, генера тор 18 импульсов, На фиг, 1 - - 3 обозна.чены соответственно.входы 19 устройства, вторые 20 выходы группы блока 5 управления первый 21 и второй 22 выходы блока управления, первые 23 входы группы коммутатора 4, первые 24 входы груп пы мультиплексора 2, третий 25 выхо блока 5 управления, вход 26 мультиплексора 2, управляюЕЦИЙ 27 выход устройства, информационный 28 выход устройства, информационные 29 выходы группы устройства, адресные 30 в ход)1 устройства. Устройство работает следуюш.1ш об разом. Входные сигналы, поступив на вхо ды 19 устройства, накапливаются в счетчиках 1,число которых соответствует числу подключенных датчиков. Сигналы пере1;олнения счетчиков 1 запоминаются в регистре 3, Счетчик 13 адресов блока 5 управления после довательно формирует адреса ячеек блока 7 памяти. При формировании j-ro адреса происходит следующее. Импульс от генератора 18 поступает на счетчик 13 адресов и эле- . мент 14 задержки. Сформированный на счетчике 13 адрес подается на вход 20 блока 7 памяти, на выход 30 устроййтва и одновременно на дешифратор 12,сигнал с которого, поступив вход 23 коммутатора 4, подготавли54вает к открытию j-й элемент И 10 и одновременно поступает на вход мультиплексорг 2 подготавливая к открытию элементы И 8 во всех его разрядах. Через - время задержки t с элемента 14 задержки снимается управляющий cHTFtan чтения, который, поступив на вход 21 блока 7 памяти, осуществляет запись содержимого j-ой ячейки в счетчик 6. Через время 1, сигнал с элемента 15 задержки поступает на вход 25 коммутатора 4, Если j-й разряд регистра 3 находится в единичном состоянии, то через j-йЭлемент И 10 и элемент ИЛИ 11 этот сигнал поступает на вход счетчика 6, прибавляя (вычитая ) едшшцу, и поступает на вход установки в нулевое состояние j-ro разряда регистра 3, время t, с элемента 16 задержки снимается управляющий сигнал, который, поступив на вход 26 мультиплексора 2 по ранее установленному j-му адресу, осуществляет вьздачу содержимого j-ro счетчика 1 н.а выход мультиплексора 2, В результате указанных действий на выходе 27 устройства в этот момент времени присутствует управляюио1и сигнал, сопровождаювдш выдачу информации. Через время t, с элемента 17 задержки снимается управляющий сигнал записи, который, поступив на ЕХОД 22 блока 7 паьятй, осуществляет запись в j-ю ячейку памяти полученного .кода с счетчика 6, С приходом следующего импульса от генератора 18 формируется (+1)-й адрес и работа устройства новторяет-. ся, Введение в устройство блока памяти, счетчика, мультиплексора и группы счетчиков по числу подключаемых датчиков позволяет повысить быстродействие устройства за счет буферизации входных о гналов на входных счетчиках и накопления в ячейках блока памяти только числа перепопнений этих счетчиков. Предлагаемое устройство не требует дополнительных аппаратурных затрат, т.к, затраты на введение 1- разрядных входных счетчиков компенсируются соответствующим уменьшением разрядности ячеек блока памя- ти, а также применением в предлагаемом устройстве вместо (-ьтЬразрядных сумматора и выходного коммутатора только Р-разряд:1сго счетчика V hi-разрядного мультиплексора.

Выходная информация представляется двумя компонентами; гп-младших разрядов снимаются через мультиплексор 2 с j-ro счетчика I (текущее состояние счетчика )i Р-старших разрлЛОР снимаются с счетчика 6, в котором в данный момент времени находится содержимое j-ой ячейки блока 7 памяти {накопленное число переполнений j-ro входного счетчика К В этом случае либо граничная частота входных сигналовJ либо число подключенных датчиков может быть увеличено в .35 где т- число разрядов счетчика 1 о

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Программное устройство управления | 1986 |

|

SU1339558A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Многоканальный временной коммутатор | 1988 |

|

SU1647922A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

1. УСТРОЙСТВО ДПЯ ВВОДА ИНФОРМАЦИИ, содержащее регистр, коммутатор и блок управления, выходы первой группы которого соединены с входами первой группы коммутатора, отличающееся тем, что, с целью повышения быстродействия, в него введенгы счетчик, мультиплексор, группа счетчиков и блок памяти, входы счетчиков группы являются входами устройства, первые выходы счетчиков группы соедине.ны с входами первой группы регистра, входы второй группы которого соединены с выходами группы коммутатора, входы второй группы которого соединены с выходами регистра, выходы первой группы блока управления соединены с входами первой группы мультиплексора, входы второй группы которого соединены с вторыми выходами счетчиков группы, вход коммутатора соединен с третьим выходом блока управления, первый выход которого соединен с входом мультиплексора и является управляющим выходом устройства, выход коммутатора соединен с входом счетчика, выходы группы которого соединены с входами второй группы блока памяти и являются информационными выходами группы устройства, выходы второй группы блока управления соединены с входами первой группы блока памяти и являются адрескь ъш выходами устройства, первый вход блока памяти соединен с четвертым выходом блока управления, второй выход которого соединен с вторым вхо дом. блока памяти, выходы группы которого соедрпшны с входами группы счетчика, выход мультиплексора является информационным выходом устройства. 2. Устройство по п.1, о т л и чающееся тем, что блок управления содерж1-5т счетчик адресов, дешифратор, первый, второй, третий и четверть элементы задержки, генератор импульсов, выход которого соединен с входом счетчика адресов и входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и являетю о ся четвертым -выходом блока управления, выход второго элемента задержсо 4; ки соединен с входом третьего элемента задержки и является третьим ел выходом блока управления, выход третьего элемента задержки соединен с входом четвертого элемента задержки и является первым выходом блока управления, выход четвертого элемента задержки является вторым выходом блока управления, выходы счетчика адресов соединены с входами дешифратора и являются выходами второй группы блока управления, выходы дешифратора являются выходами первой группы блока управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ВВОДА ИНФОРМАЦИИ | 0 |

|

SU352270A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ввода информации от датчиков | 1975 |

|

SU561954A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-30—Публикация

1983-07-19—Подача