Фиг.

Изобретение относится к многоканальной связи и может быть использовано в автоматизированных комплексах обработки данных для подключения входных информационных каналов к аппаратура обработки,

Цель изобретения - повышение емкости коммутатора при сохранении быстро- деиствия.

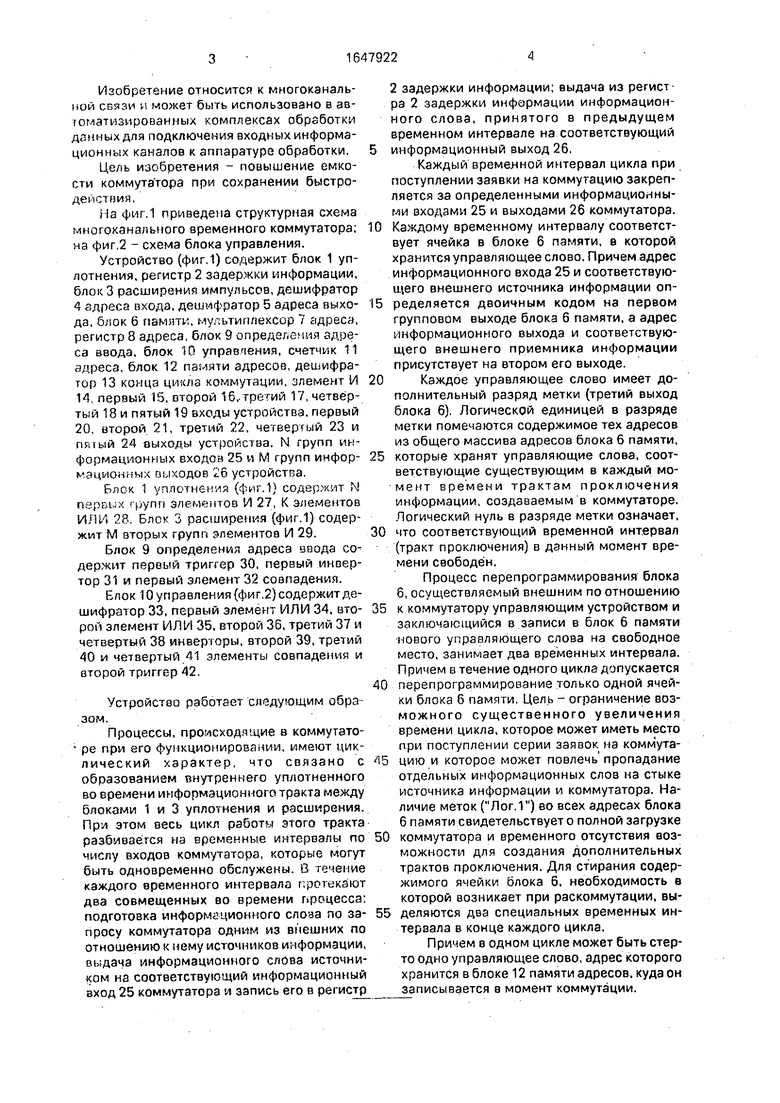

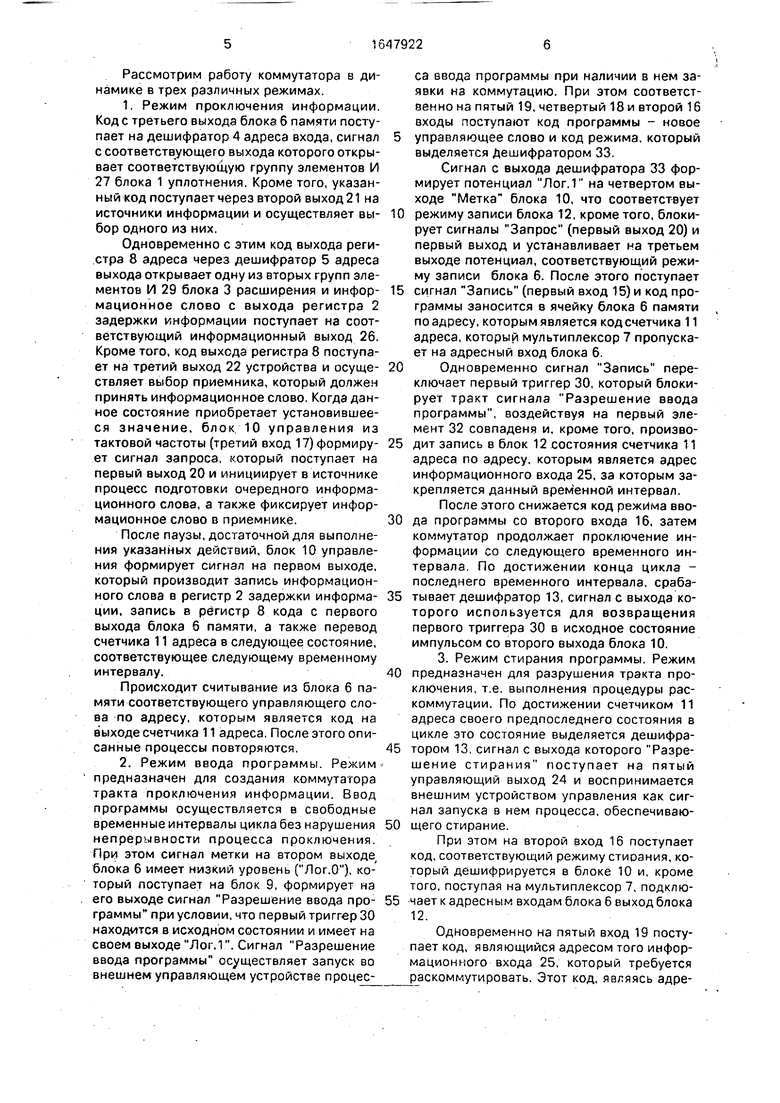

На фиг.1 приведена структурная схема многоканального временного коммутатора; на фиг.2 - схема блока управления.

Устройство (фиг,1) содержит блок 1 уплотнения, регистр 2 задержки информации, блок 3 расширений импульсов, дешифратор 4 адреса входа, дешифратор 5 адреса выхода, блок 6 памяти, мультиплексор 7 адреса, регистр 8 адреса, блок 9 определения адреса ввода, блок 10 управпения, счетчик 11 адреса, блок 12 памяти адресов, дешифратор 13 конца цикла коммутации, олемент И 14, первый 15, второй 16, грегий 17, четвертый 18 и пятый 19 входы устройства, первый 20, второй 21, третий 22, четвертый 23 и питый 24 выходы устройства. N групп информационных входов 25 и М групп информационных выходов 26 устройства.

Блок 1 уплотнения (фиг.1 содержит N гкервьх рулп элементов И 27, К элементов ИЛИ В. Блок 3 расширения (фиг.1) содержит М вторых групп элементов И 29.

Блок 9 определения адреса ввода содержит первый триггер 30, первый инвертор 31 и первый элемент 32 совпадения.

Блок 10 управления (фиг,2) содержит дешифратор 33, первый элемент ИЛИ 34, второй элемент ИЛИ 35, второй 36, третий 37 и четвертый 38 инверторы, второй 39, третий 40 и четвертый 41 элементы совпадения и второй триггер 42.

Устройство работает следующим обра зом.

Процессы, происходящие а коммутато- ре при его Функционировании, имеют циклический характер, что связано с образованием внутреннего уплотненного во времени информационного тракта между блоками 1 и 3 уплотнения и расширения. При этом весь цикл работы этого тракта разбивается на временные интервалы по числу входов коммутатора, которые могут быть одновременно обслужены. В течение каждого временного интервала протекают два совмещенных во времени процесса: подготовка информационного слоза по запросу коммутатора одним из внешних по отношению к нему источников информации, выдача информационного слова источникам на соответствующий информационный вход 25 коммутатора и запись его в регистр

2 задержки информации; выдача из регистра 2 задержки информации информационного слова, принятого в предыдущем временном интервале на соответствующий

информационный выход 26.

Каждый времеяной интервал цикла при поступлении заявки на коммутацию закрепляется за определенными информационными входами 25 и выходами 26 коммутатора.

0 Каждому временному интервалу соответствует ячейка в блоке 6 памяти, в которой хранится управляющее слово. Причем адрес информационного входа 25 и соответствую- щего внешнего источника информации оп5 ределяется двоичным кодом на первом групповом выходе блока 6 памяти, а адрес информационного выхода и соответствующего внешнего приемника информации присутствует на втором его выходе.

0 Каждое управляющее слово имеет дополнительный разряд метки (третий выход блока 6). Логической единицей в разряде метки помечаются содержимое тех адресов из общего массива адресов блока 6 памяти,

5 которые хранят управляющие слова, соответствующие существующим в каждый момент времени трактам проключения информации, создаваемым в коммутаторе. Логический нуль в разряде метки означает,

0 что соответствующий временной интервал (тракт проключения) в данный момент времени свободен.

Процесс перепрограммирования блока 6, осуществляемый внешним по отношению

5 к коммутатору управляющим устройством и заключающийся в записи в блок 6 памяти нового управляющего слова на свободное место, занимает два временных интервала. Причем в течение одного цикла допускается

0 перепрограммирование только одной ячейки блока 6 памяти, Цель - ограничение возможного существенного увеличения времени цикла, которое может иметь место при поступлении серии заявок, на коммута5 цию и которое может повлечь пропадание отдельных информационных слов на стыке источника информации и коммутатора. Наличие меток (Лог.1) во всех адресах блока 6 памяти свидетельствует о полной загрузке

0 коммутатора и временного отсутствия возможности для создания дополнительных трактов проключения. Для стирания содержимого ячейки блока 6, необходимость в которой возникает при раскоммутации, вы5 деляются два специальных временных интервала в конце каждого цикла.

Причем в одном цикле может быть стерто одно управляющее слово, адрес которого хранится в блоке 12 памяти адресов, куда он записывается в момент коммутации.

Рассмотрим работу коммутатора в динамике в трех различных режимах.

1.Режим проключения информации. Код с третьего выхода блока б памяти поступает на дешифратор 4 адреса входа, сигнал с соответствующего выхода которого открывает соответствующую группу элементов И 27 блока 1 уплотнения. Кроме того, указанный код поступает через второй выход 21 на источники информации и осуществляет выбор одного из них.

Одновременно с этим код выхода регистра 8 адреса через дешифратор 5 адреса выхода открывает одну из вторых групп элементов И 29 блока 3 расширения и информационное слово с выхода регистра 2 задержки информации поступает на соответствующий информационный выход 26. Кроме того, код выхода регистра 8 поступает на третий выход 22 устройства и осуществляет выбор приемника, который должен принять информационное слово. Когда данное состояние приобретает установившееся значение, блок 10 управления из тактовой частоты (третий вход 17) формирует сигнал запроса, который поступает на первый выход 20 и инициирует в источнике процесс подготовки очередного информационного слова, а также фиксирует информационное слово в приемнике.

После паузы, достаточной для выполнения указанных действий, блок 10 управления формирует сигнал на первом выходе, который производит запись информационного слова в регистр 2 задержки информации, запись в регистр 8 кода с первого выхода блока б памяти, а также перевод счетчика 11 адреса в следующее состояние, соответствующее следующему временному интервалу.

Происходит считывание из блока 6 памяти соответствующего управляющего слова по адресу, которым является код на выходе счетчика 11 адреса, После этого описанные процессы повторяются.

2.Режим ввода программы. Режим предназначен для создания коммутатора тракта проключения информации. Ввод программы осуществляется в свободные временные интервалы цикла без нарушения непрерывности процесса проключения. При этом сигнал метки на втором выходе блока 6 имеет низкий уровень (Лог.О), который поступает на блок 9, формирует на его выходе сигнал Разрешение ввода программы при условии, что первый триггер 30 находится в исходном состоянии и имеет на своем выходе Лог. 1. Сигнал Разрешение ввода программы осуществляет запуск во внешнем управляющем устройстве процесса ввода программы при наличии в нем заявки на коммутацию. При этом соответственно на пятый 19, четвертый 18 и второй 16 входы поступают код программы - новое управляющее слово и код режима, который выделяется дешифратором 33.

Сигнал с выхода дешифратора 33 формирует потенциал Лог.1 на четвертом выходе Метка блока 10, что соответствует

0 режиму записи блока 12, кроме того, блокирует сигналы Запрос (первый выход 20) и первый выход и устанавливает на третьем выходе потенциал, соответствующий режиму записи блока 6. После этого поступает

5 сигнал Запись (первый вход 15) и код программы заносится в ячейку блока 6 памяти по адресу, которым является код счетчика 11 адреса, который мультиплексор 7 пропускает на адресный вход блока 6.

0 Одновременно сигнал Запись переключает первый триггер 30, который блокирует тракт сигнала Разрешение ввода программы, воздействуя на первый элемент 32 совпаденя и, кроме того, произво5 дит запись в блок 12 состояния счетчика 11 адреса по адресу, которым является адрес информационного входа 25, за которым закрепляется данный временной интервал. После этого снижается код режима вво0 да программы со второго входа 16, затем коммутатор продолжает проключение информации со следующего временного интервала. По достижении конца цикла - последнего временного интервала, сраба5 тывает дешифратор 13, сигнал с выхода которого используется для возвращения первого триггера 30 в исходное состояние импульсом со второго выхода блока 10. 3. Режим стирания программы. Режим

0 предназначен для разрушения тракта проключения, т.е. выполнения процедуры рас- коммутаций. По достижении счетчиком 11 адреса своего предпоследнего состояния в цикле это состояние выделяется дешифра5 тором 13, сигнал с выхода которого Разрешение стирания поступает на пятый управляющий выход 24 и воспринимается внешним устройством управления как сигнал запуска в нем процесса, обеспечиваю0 щего стирание.

При этом на второй вход 16 поступает код, соответствующий режиму стиоания, который дешифрируется в блоке 10 и, кроме того, поступая на мультиплексор 7. подклю5 чает к адресным входам блока 6 выход блока 12.

Одновременно на пятый вход 19 поступает код, являющийся адресом того информационного входа 25, который требуется раскоммутировать. Этот код, являясь адресом блока 12, вызывает считывание адреса ячейки в блоке 6, которая отведена для хранения управляющего слова, относящегося к тому тракту проключения. который требуется раскоммутировать.

Сигнал с выхода дешифратора 33 блокирует сигнал запроса на пятом выходе блока 10 и соответственно на первом выходе 20, кроме того он переводит блок 6 в режим записи сигналом Лог. 1й на третьем выходе блока 10. Сигналом Запись, поступающим на первый вход 15, производится запись в ячейку блока 6 кода, который в разряде Метка имеет Лог.О, что означает, что данный адрес блока б, а значит и соответствующий временной интервал свободны.

После этого режим стирания снимается, счетчик 11 адреса, завершив цикл, приходит в исходное состояние, являющееся началом следующего цикла.

Формула изобретения

Многоканальный временной коммутатор, содержащий последовательно соединенные дешифратор адреса входа и блок уплотнения, информационные входы которого являются информационными входами устройства, последовательно соединенные дешифратор адреса выхода и блок расширения импульсов, выходы которого являются информационными выходами устройства, последовательно соединенные блок памяти и регистр адреса, последовательно соединенные блок управления и счетчик адреса, отличающийся тем, что, с целью повышения емкости коммутатора при сохранении быстродействия, введены последовательно соединенные дешифратор конца цикла коммутации и элемент И, регистр задержки информации, входы которого соединены с выходами блока уплотнения, последовательно соединенные блок памяти

адресов и мультиплексор адреса, блок определения адреса ввода, первый и второй входы которого подключены соответственно к второму выходу дешифратора конца цикла

коммутации и второму выходу блока памяти, второй и третий выходы которого соединены соответственно с первыми входами блока управления и дешифратора адреса входа, а второй выход блока управления подключен к второму входу элемента И и третьему входу блока определения адреса ввода, четвертый вход которого объединен с тактовыми входами блока памяти адресов и блока памяти и является первым управляющим

входом устройства, вторым входом которого являются вторые входы блока управления и мультиплексора адреса, выход которого подключен к первому входу блока памяти, второй вход которого подключен к третьему

входу блока управления, первый выход которого подключен к управляющим входам регистра адреса и регистра задержки информации, выходы которых подключены соответственно к входам дешифратора адреса

выхода и блока расширения импульсов, причем выход счетчика адреса соединен с входом дешифратора конца цикла, третьим входом мультиплексора адреса и вторым входом блока памяти адресов, третий вход

которого соединен с третьим входом блока памяти и четвертым выходом блока управления, третий вход которого является третьим управляющим входом устройства, четвер- тым-и пятым управляющими входами которого являются соответственно четвертый вход блока памяти и объединенные четвертые входы блока памяти и блока памяти адресов, а пятый выход блока управления, третий выход блока памяти, выходы регистра адреса блока определения адреса ввода и элемента И являются соответственно первым, вторым, третьим, четвертым и пятым управляющими выходами устройства.

К блокам

К блокам 9,14

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Коммутационное устройство | 1987 |

|

SU1478371A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

Изобретение относится к связи и может быть, использовано в автоматизированных комплексах обработки данных для подключения входных информационных каналов к аппаратуре обработки. Целью изобретения является повышение емкости коммутатора при сохранении быстродействия. Устройство содержит блок 1 уплотнения, регистр 2 задержки информации, блок 3 расширения, дешифратор 4 адреса входа, дешифратор 5 адреса выхода, блок 6 памяти, мультиплексор 7 адреса, регистр 8 адреса, блок 9 определения адреса ввода, блок 10 управления, счетчик 11 адреса, блок 12 памяти адресов, дешифратор 13 конца цикла, элемент И 14, первый 15, второй 16, третий 17, четвертый 18 и пятый 19 входы устройства, первый 20, второй 21. третий 22, четвертый 23 и пятый 24 выходы устройства, N групп информационных входов 25, М групп информационных выходов 26. При взаимодействии абонентов с коммутатором по асинхронному принципу увеличивается возможная емкость коммутатора, обусловленная временем переключения коммутационных элементов, 2 ил.

Фиг. 2

| Синхронное адресно-временное устройство коммутации | 1982 |

|

SU1058079A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-05—Подача