1

Изобретение относится к вычисли тельной технике и предназначено для ло1 арифмирования двоичных чисел в арифметических устройствах ЭВМ и спецпроцессоров.

Цель изобретения повышение быстродействия устройства и сокращение аппаратурных затрат.

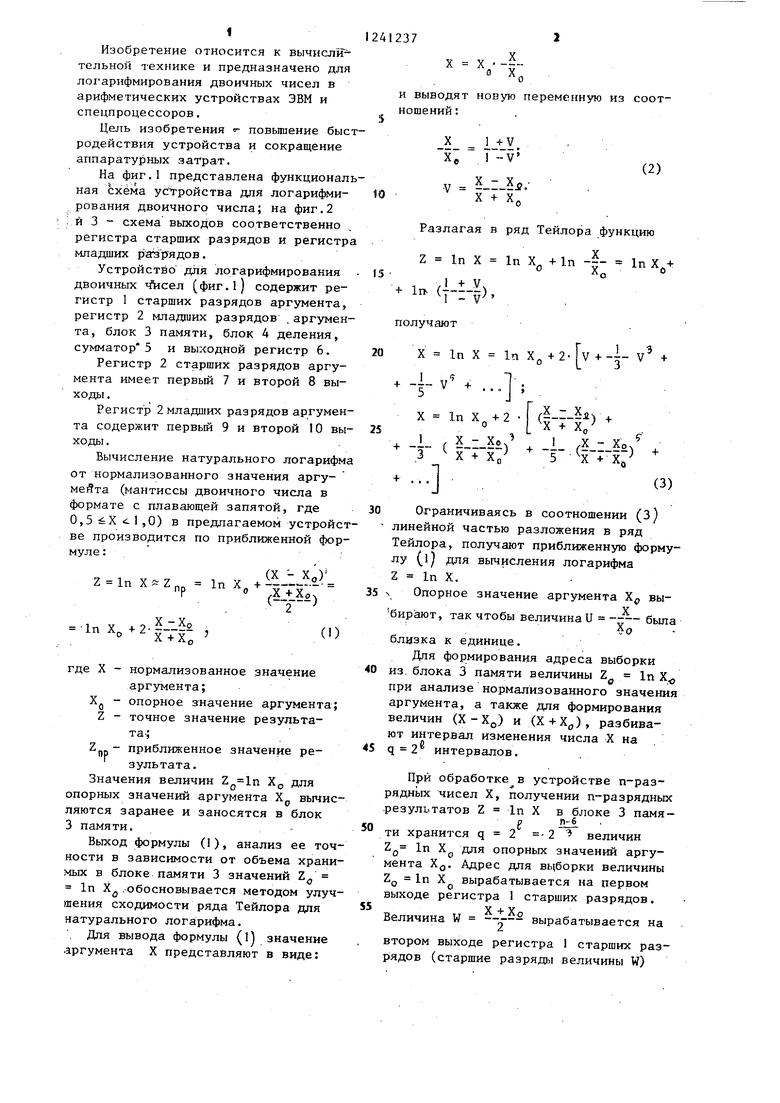

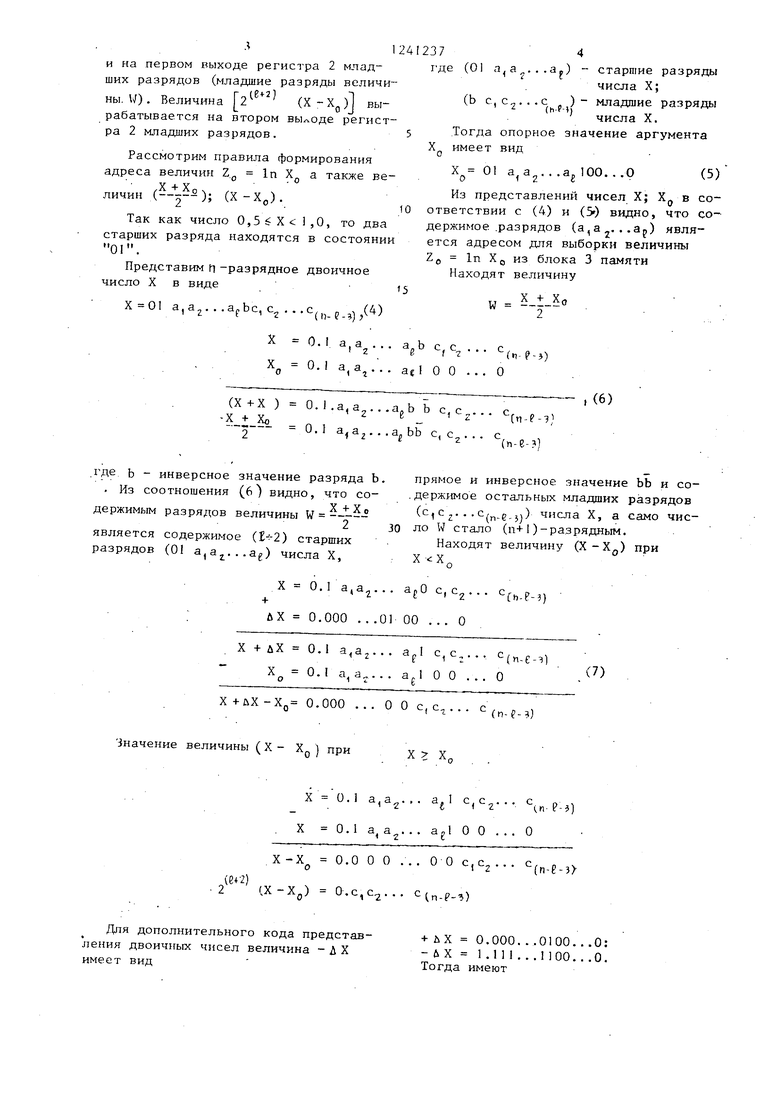

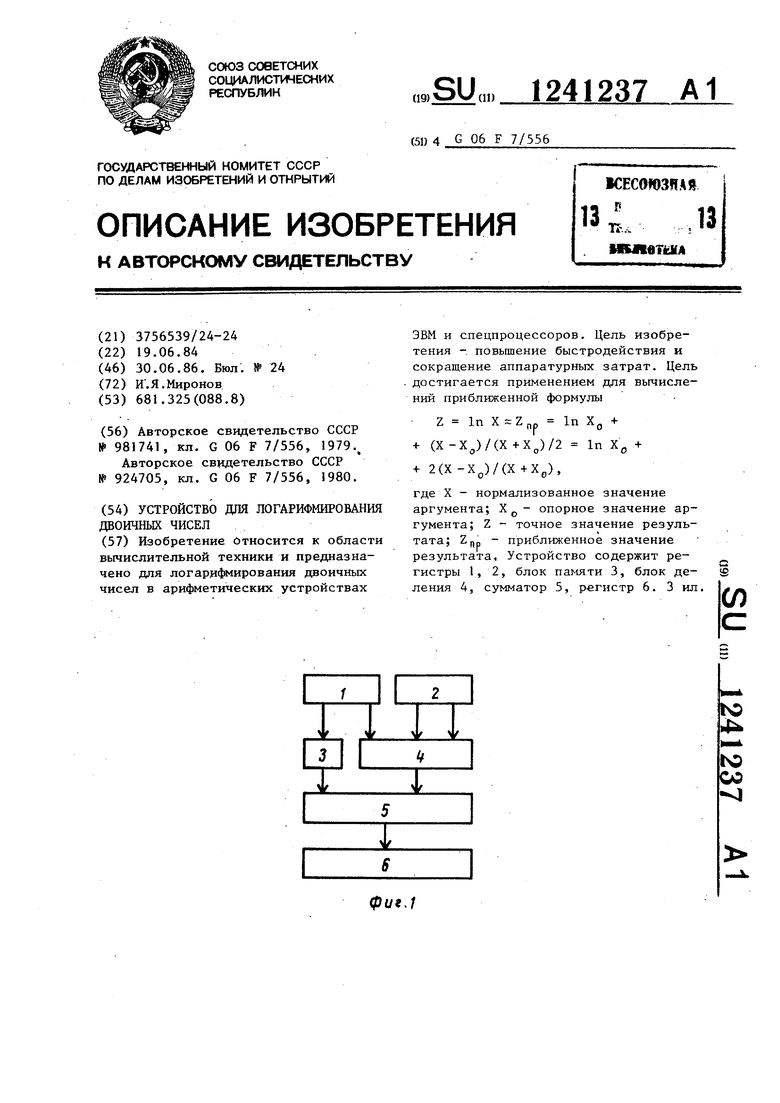

На фиг.1 представлена функциональная схема устройства для логарифмирования двоичного числа; на фиг.2 и 3 - схема выходов соответственно регистра старших разрядов и регистра младших рагз рядов.

Устройство для логарифмирования двоичных (фиг.1) содержит регистр 1 старших разрядов аргумента, регистр 2 младших разрядов .аргумента, блок 3 памяти, блок Д деления, сумматор 5 и выходной регистр 6.

Регистр 2 старших разрядов аргумента имеет первый 7 и второй 8 выходы .

Регистр 2 младших разрядов аргумента содержит первый 9 и второй 10 выходы .

Вычисление натурального логарифма от нормализованного значения аргу- мейта (мантиссы двоичного числа в формате с плавающей запятой, где 0,5бХ с1,0) в предлагаемом устройстве производится по приближенной формуле :

(X - Х)

Z lnX.Z,p 1пХ,-ь

(-,

- . 1 V J. 9 О

- In X, -Ь2.----- ,

(1)

где X - нормализованное значение

аргумента;

Xjj - опорное значение аргумента; Z - точное значение результата ;

Zji - приближенное значение результата.

Значения величин Х для опорных значений аргумента Хр вычисляются заранее и заносятся в блок 3 памяти.

Выход формулы (I), анализ ее точности в зависимости от объема хранимых в блоке памяти 3 значений In Хд.обосновывается методом улучшения сходимости ряда Тейлора для натурального логарифма. . Для вывода формулы (1) значение аргумента X представляют в виде:

1241237

V-x;

и выводят новую переменную из соотношений:

X,

V 1

(2)

10

V . X + X

Разлагая в ряд Тейлора функцию

Z In X In X +In In X + 15о

i(fH),

получают X In X In X, + 2- v + -|vn

-l-V...,,-;

x inx.2.|()4

Д - X,

3 X + X

...

Эf

X 1 ,X -

vT v-V 5 ,

(3)

Ограничиваясь в соотношении (З) линейной частью разложения в ряд Тейлора, получают приближенную формулу (l для вычисления логарифма Z In X.

Опорное значение аргумента Х выX бирают, так чтобы величина U была

. о близка к единице.

Для формирования адреса выборки из, блока 3 памяти величины 2 In Х при анализе нормализованного значения аргумента, а также для формирования величин (Х-Хо) и (Х + Х), разбивают интервал изменения числа X на интервалов.

При обработке в устройстве п-раз- ряднь1Х чисел X, получении п-разрядных .результатов Z In X в блоке 3 памяf Jlii ти хранится q 2 -2 величин

Z In Хр для опорных значений аргумента Хд.

Zo In Х

Адрес для вцборки величины вырабатывается на первом выходе регистра 1 старших разрядов.

Величина W

Х+Хо

вырабатывается на

втором выходе регистра I старших разрядов (старшие разряды величины W)

л12412374

и на первом выходе регистра 2 млад- где (01 ...а) старшие разряды ших разрядов (младшие разряды величи-числа X;

,,ч „ /V V Л(Ь с. с„. . .с „ ) - младшие разряды

ны. W). Величина 2 (X - X ) вы- 2 (-р-(

Lо J, числа X.

рабатывается на втором вьиоде регист , Тогда опорное значение аргумента

ра 2 младших разрядов. ,

. Хд имеет вид

Рассмотрим правила формирования ,, . ,

л-и1аа...а„1ии...и vjy адреса величин Z. In Х а также не- о

fy у )Из представлений чисел X; Х, в соличин (- 2 ;; U .. ответствии с (4) и (5-) видно, что соТак как число 0,5 6Х 1,0, то двадержимое .разрядов (a,a,j, ..Зр) явля- старших разряда находятся в состоянии ется адресом для выборки величины

01.Zo In Xjj из блока 3 памяти

Представим п-разрядное двоичноеНаходят величину

число X в виде 5 v L v

W -----° a,a2...apbc,C2...C(,g,/4)2

X 0.1 a,a... c, c . . . c X 0.I a,a... ael 0 0 ... 0

,(6)

.f; O.l.a,a... c,c... c,,,,

-.-- 0.1 a,a... c, c... c ,

. b - инверсное значение разряда b. прямое и инверсное значение ЬЬ и со- . Из соотношения (б) видно, что со- .держимое остальных младших разрядов

держимым разрядов величины W 2-° (с, с ,. . . c.g.,,) числа X, а само чис230 ло W стало (п+1)-разрядным.

является содержимое () старших. Находят величину (Х-Х) при разрядов (01 a,aj...ag) числа X, о

X 0.1 а,а... ajO с,с... с.,р., ЛХ 0.000 . . .01 00 . . . О

X + дХ 0.1 а, а 2... с, с,... C(g.,,

X 0. а, а.. . . а J О О . . . О .

о i

Х+йХ-Хц 0.000 ... о о с,с.... , Значение величины (X - Х. ) приX X

X 0.1 ... ... с. р X 0.1 а, а„... О О . .. О

1

Х-Х 0.0 о о ... 00 с,С2... (Х-Хд) 0-.с,с... с.р,)

Для дополнительного кода представ- +ЛХ 0.000. . .01 00. . ,0; ления двоичных чисел величина -ДХ -ЛХ 1.111...1100...0. имеет вид Тогда имеют

(X + &Х - Х) 0.000 ..

, ()

,--(х - XJ l.

Из выражения (7) и (8) видно, что величина (Х-Х Я в дополниUо J

тельном коде формируется путем .выдачи старшим разрядом инверсного значения b -и содержи- мого разрядов (с, с . . C(.g.,p, т.е.

2 Чх-Х,) bc,c...c,.,,j.

В предлагаемом устройстве для логарифмирования -двоичньпх: чисел формирование адреса (.) к величин

W 5-t , Q (Х-Х„) производится следующим образом.

В регистре 1 старших разрядов хранятся (1+2) старших разряда аргумента X; в регистре 2 младших разрядов хранятся остальные (п-1-2 ) младших разряда числа X.

Первый выход регистра 1 старших разрядов, который является адресом величины Z In Xg представляет собой прямые выходы всех, исключая два старших, разрядов регистра 1 старших разрядов.

X + Хо Величина W -г формируется

путем выдачи прямого кода из регистра 1 старших разрядов, прямого и инверсного содержимого старшего разряда и прямого кода всех остальных разрядов регистра 2 младших разрядов

Величина Q (X -Х) рорми- уется на втором выходе регистра 2 младших разрядов путем выдачи инверсного значения старшего и прямого кода остальных разрядов регистра 2.

Так как величина

I , -()

|X-XJ 2, то при вычислении величины

, . „(е+2)/X - ХоЛ

- - (ггх; :

достаточно в блоке 4 деления определить (п--2-1) его старших разрядов.

00 с,с..

(п-е-з)

(п-е-)

Для обеспечения выдачи в сумматор 5 величины

7 - d . Х +Хо 2(f+27

необходимо вьгход блока 4 деления подключить к второму входу сумматора 5 со сдвигом вправо на (1+2) разрядов.

Устройство Д/1Я логарифмирования двоичных чисел при реализации алгоритма по формуле () работает следуюшим образом.

Нормализованное п-разрядное значение аргумента X хранится в регистрах 1 и 2 старших и младших разрядов, имеющих разрядность соответствен-, но (1+2) (п-1-2), при этом выполняется условие 3(1+2) п, что позволяет получить точность результата Z 1п X, при которой абсолютная ошиб-; ка не превосходит половины дены младшего разряда п-разрядного результата.

На первом выходе регистра I старших разрядов вырабатывается адрес числа Z In Хд, которое поступает на выход блока 3 памяти. Адресом является содержимое f младших разрядов регистра 1 старших разрядов.

В блок А деления поступают вели

чины W и Q (Х -X,).

Делимое Q- 2 (X - Х) поступает в блок 4 со второго выхода регистра 2 младших, разрядов, а (-0+1 )-разрядX + Хс ньГи делитель W --- формируется

на втором выходе регистра 1 старших разрядов (1+2), т.е.,старших разрядов величины.W, и на первом выходе регистра. 2 младших разрядов (), т.е. младших разрядов величины W.

На выходе блока 4 деления, обрабатывающего числа в дополнительном коде величина

, , (г. X - Хо d - 2 . Z . ()

Так как выход блока 4 деления соединен с вторым входом сумматора 5 со сдвигом на (f+2) разрядов вправо, а выход блока памяти 3 соединен с первым входом сумматора 5, то в последний поступают величины

Z. In X

о

9 /--- --S-- f- Vv j- V A + Xo

Выработанный в соответствии мулой (1) результат

In Х 42(

пр - о Х + X с выхода сумматора 5 поступает в выходной регистр 6 и является выходной величиной устройства.

Формула изобретения

Устройство дця логарифмирования двоичных чисел,, содержащее регистры

(put, 2

Составитель А.Шуляпов Редактор Л.Пчелинская Техред О.Гортвай Корректор Л.Патай

Заказ 3490/44 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

старших и младших разрядов аргумента, выходной регистр, блок памяти, блок деления и сумматор, выход кото- рого соединен с входом выход1 ого регистра, первый выход регистра старших разрядов аргумента соединен с адресным входом блока памяти, о т - личающе е ся тем, что, с ,

целью повышения быстродействия, в нем второй выход регистра старших разрядов аргумента и первый выход регистра младших разрядов аргумента соединены с входом делителя блока деления, вход делимого которого соединен с вторым выходом регистра младших разрядов аргумента, выход блока памяти соединен с первым входом сумматора, выход блока деления

соединен с вторым входом сумматора со сдвигом в сторону младших разрядов на количество разрядов регистра старших разрядов аргумента.

Ю Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Функциональный преобразователь | 1983 |

|

SU1126968A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Функциональный преобразователь | 1980 |

|

SU962971A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Цифровой логарифмический преобразователь | 1987 |

|

SU1425665A1 |

Изобретение Относится к области вычислительной техники и предназначено для логарифмирования двоичных чисел в арифметических устройствах ЭВМ и спецпроцессоров. Цель изобретения -. повышение быстродействия и сокращение аппаратурных затрат. Цель достигается применением для вычислений приближенной формулы Z In 1п Хд + (Х-Х)/(Х+Х)/2 In Хо + + 2(Х-Х)/(Х+Хд), где X - нормализованное значение аргумента; опорное значение аргумента; Z - точное значение результата; Zpp - приближенное значение результата. Устройство содержит регистры 1,2, блок памяти 3, блок деления 4, сумматор 5, регистр 6. 3 ил. а (Q (Л 1 фиг.1

| Импульсный вариатор | 1981 |

|

SU981741A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-06-19—Подача