11

Изобретение относится к вьгчисли- тельной технике и может быть использовано для вычисления монотонно убы- вагощ1сс нелинейных функций цифрового аргумента в быстродействующих специализированных процессорах.

Целью изобретения является расширение диапазона за счет обеспечения работы измеряемых величин с положительными и отрицательными значениями аргумента,

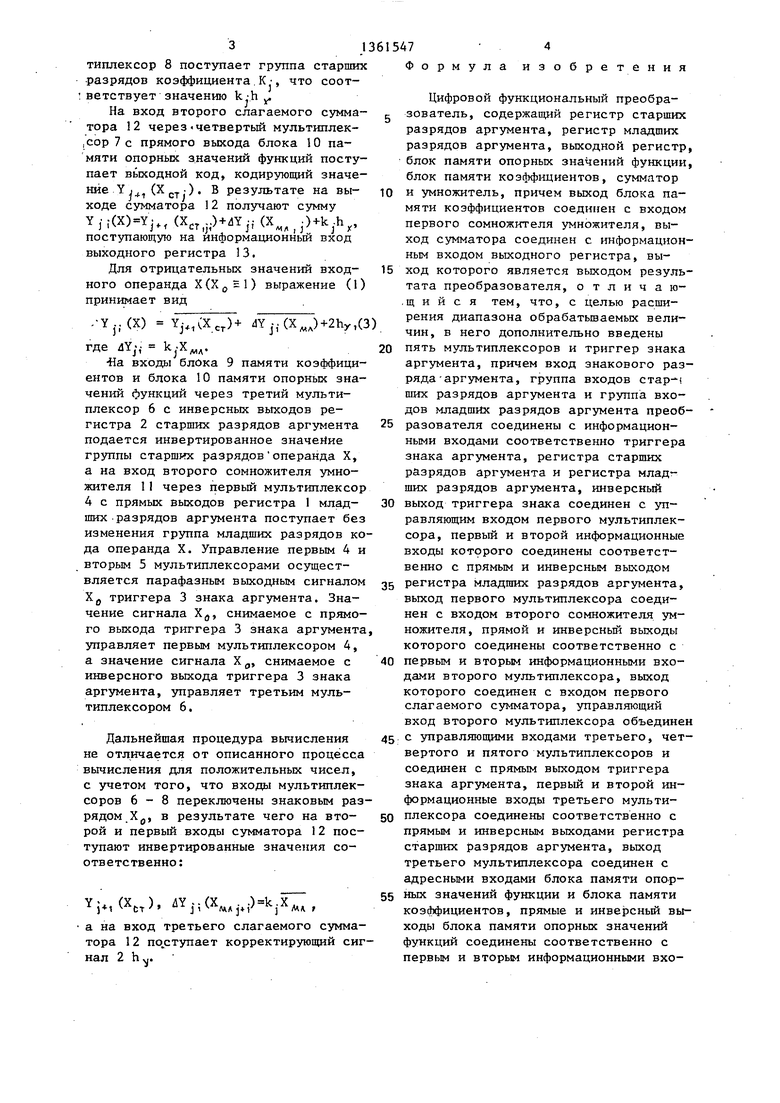

На чертеже представлена функциональная схема преобразователя.

Преобразователь содержит регистр .I младших разрядов аргумента, регистр 2 старших разрядов аргумента, триггер 3 знака аргумента, с первого по пятый мультиплексоры 4-8 соответственно, блок, 9 памяти коэффициентов , блок IО памяти опорных значений функции, умножитель 11, сумматор 12-и выходной регистр 13.

Преобразователь работает следующим образом.

Для положительных чисел дополнительный код операнда совпадает с прямым кодом и работа преобразователя аналогична работе известных устройст Для отрицательных чисел операнд преобразуют в прямой код следзтощим образом

+ h

np у где hj, - вес единицы младшего разряда операнда х.

Разбив из старшую и младшую группу разрядов, получаем

X

Пр ст Л1Л V

Для вычисления приращения функции в данном случае необходимо вычислить произведение

fvAO

( МА

hx)kxrkh.

Поскольку значение kh есть вели- коэффициента К-, которое поступает на

чина постоянная в диапазоне интерполяции, то она может быть всегда учтена в виде корректирующего слагаемого. С учетом сказанного вычисления в преобразователе производятся по следующему алгоритму

50

вход первого сомножителя умножителя 11, на вход второго сомножителя которого поступает с инверсных выходов регистра I младших разрядов аргумента через первый мультиплексор 4 инвертированное значение X . ,

YjS(X)X,©Y., (Х;.,,)+Хо н- ©4Yv:(X + X, h .

MA j

J

где X X ll Xj2 ;

i XQ - знаковый разряд операнда X;

XJiTj - старшие разряды операнда;

х .

OT/f

X ©X

OTJ

0

5

U U ь

/ j ,:

h - вес единицы младшего разряда операнда

h у 2.hy

4Yj, (X«,j,)k.(.) X ..- младшие разряды операнда;

ЛЛ t

J. - индекс опорных значений; i - индекс значений между двумя

опорными точками; Ьу вес единицы младшего разряда

функции; + - арифметическое сложение;

- арифметическое умножение; ф - логическая операция суммирования по mod2; л - логшгеское умножение. Величины Y (Хр|.) и Vi выбираются ИЗ первого и второго блоков 9 и 10 памяти.

Допустим, что знаковый разряд X О, т.е. аргумент положительный.

Для этого случая Лормула (1) бу-. г- дет иметь вид Y,(X)Y., (Х,,,рч-Л..(Х„..)1с.С2)

х Ъ т

0 где%У|;(Х,), J,- .

Работа устройства начинается с занесения кода аргумента в регистры I и 2 и триггер 3. Для положительных

5

значений входного операнда Х(Хд О) выходные сигналы, снимаемые с прямых выходов регистра 2 старших разрядов аргумента ,через третий мультиплексор 6 поступают на адресный вход блока 10 памяти опорных значений функции, на выходе которого формируется значение функции Y ;+,(,;) , заданное для XgT г , а также на адресный вход блока 9 памяти коэффициентов, на выходе которого формируется значение

0

5

вход первого сомножителя умножителя 11, на вход второго сомножителя которого поступает с инверсных выходов регистра I младших разрядов аргумента через первый мультиплексор 4 инвертированное значение X . ,

На выходе умножителя 11 формируется произведение , „ которое с помощью второго мультиплексора 5 снимается с прямого выхода умножителя 1I и подается на вход первого слагаемого сумматора 12,, на вход третьего слагаемого которого с выхода блока 9 памяти коэффициентов через пятый мультиплексор 8 поступает группа старших разрядов коэффициента , К , что соот- ветствует значению k h

На вход второго слагаемого сумматора 12 через«четвертьш мультиплек- сор 7с прямого выхода блока 10 памяти опорных значений функций поступает Бькодной код, кодирующий значение Y , (X ) . В результате на выходе сумматора 12 получают сумму Yj,-(X)Yj,,(X,,..)(X.)-Hk.h, поступающую на информационный вход выходного регистра 13.

Для отрицательных значений входного операнда Х() выражение (1) принимает вид

-Yj.;(X) ,,(X,,)+ dY,,-,.(X,)+2hy,(3

где ЛYJ, kyX,.

На входы блока 9 памяти коэффициентов и блока 10 памяти опорных значений функций через третий мультиплексор 6 с инверсных выходов регистра 2 старших разрядов аргумента подается инвертированное значение группы старших разрядов операнда X, а на вход второго сомножителя умножителя II через первый мультиплексор 4 с прямых выходов регистра 1 младших -разрядов аргумента поступает без изменения группа младших разрядов кода операнда X. Управление первым 4 и вторым 5 мультиплексорами осуществляется парафазным выходным сигналом Хд триггера 3 знака аргумента. Значение сигнала Х, снимаемое с прямого выхода триггера 3 знака аргумента управляет первым мультиплексором 4, а значение сигнала X д, снимаемое с инверсного выхода триггера 3 знака аргумента, управляет третьим мультиплексором 6.

Дальнейшая процедура вычисления не отличается от описанного процесса вычисления для положительных чисел, с учетом того, что входы мультиплексоров 6-8 переключены знаковым разрядом Х, в результате чего на второй и первый входы сумматора 12 поступают инвертированные значения соответственно:

YJ,, (X,,), iYj.;(X,.,.)k.X, ,

а на вход третьего слагаемого сумматора 12 по.ступает корректирующий сигнал 2 h v.

Формула изобретения

Цифровой функциональный преобразователь, содержащий регистр старших разрядов аргумента, регистр младших разрядов аргумента, выходной регистр, блок памяти опорных значений функции, блок памяти коэ фициентов, сумматор

и умножитель, причем выход блока памяти коэффициентов соединен с входом первого сомножителя умножителя, выход сумматора соединен с информационным входом выходного регистра, выход которого является выходом результата преобразователя, отличаю- .щ и и с я тем, что, с целью расширения диапазона обрабатьшаемых величин, в него дополнительно введены

пять мультиплексоров и триггер знака аргумента, причем вход знакового разряда аргумента, группа входов стар-ч ших разрядов аргумента и группа входов младших разрядов аргумента преобразователя соединены с информационными входами соответственно триггера знака аргумента, регистра старших разрядов аргумента и регистра младших разрядов аргумента, инверсный

выход триггера знака соединен с управляющим входом первого мультиплексора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходом

регистра младших разрядов аргумента, вькод первого мультиплексора соединен с входом второго сомножителя умножителя, прямой и инверсный выходы которого соединены соответственно с

первым и вторьм информационными входами второго мультиплексора, выход которого соединен с входом первого слагаемого сумматора, управляющий вход второго мультиплексора объединен

с управляющими входами третьего, четвертого и пятого мультиплексоров и соединен с прямым выходом триггера знака аргумента, первый и второй информационные входы третьего мультиплексора соединены соответственно с прямым и инверсным выходами регистра старших разрядов аргумента, выход третьего мультиплексора соединен с адресными входами блока памяти опорных значений функции и блока памяти коэффициентов, прямые и инверсный выходы блока памяти опорных значений функций соединены соответственно с первым и вторым информационными вхо5 13615476

дами четвертого мультиплексора, вы- вый и второй информационный входы ко- ход которого соединен с входом вто- торого соединены соответственно с вы- рого слагаемого сумматора, вход тре- ходами старших разрядов блока памяти тьего слагаемого которого соединен с коэффициентов и входом коррекции пре- выходом йятого мультиплексора, пер- « образователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Цифровой функциональный преобразователь | 1987 |

|

SU1444758A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для вычисления корня | 1985 |

|

SU1339556A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления функции табличным методом | 1986 |

|

SU1383337A1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления сложных математических функций, в частности монотонно убьшающих нелинейных функций в быстродействующих специализированных вычислителях. Цель изобретения - расширение диапазона обрабатываемых величин за счет обеспечения работы с положительными и отрицательными значениями аргумента. Преобразователь содержит регистр 1 младших разрядов аргумента, регистр 2 старших разрядов аргумента, триггер 3 знака аргумента, мультиплексоры 4, 5, 6, 7, 8, блок 9 памяти коэффициентов, блок 10 гтамяти опорных значений функции, умножитель 11, сумматор 12, выходной регистр 13. Преобразователь реализует таблично-алгоритмический способ вычисления на основе линейной интерполяции. Аргументы функции представлены в дополнительном коде, что обеспечивает работу как с положительными, так и с отрицательньми числами. 1 ил. G S

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровые таблично-алгоритмические функциональные преобразователи с линейной интерполяцией - Электронное моделирование, 1985, № 1, с.57. | |||

Авторы

Даты

1987-12-23—Публикация

1986-05-20—Подача