(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU809210A2 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1191911A1 |

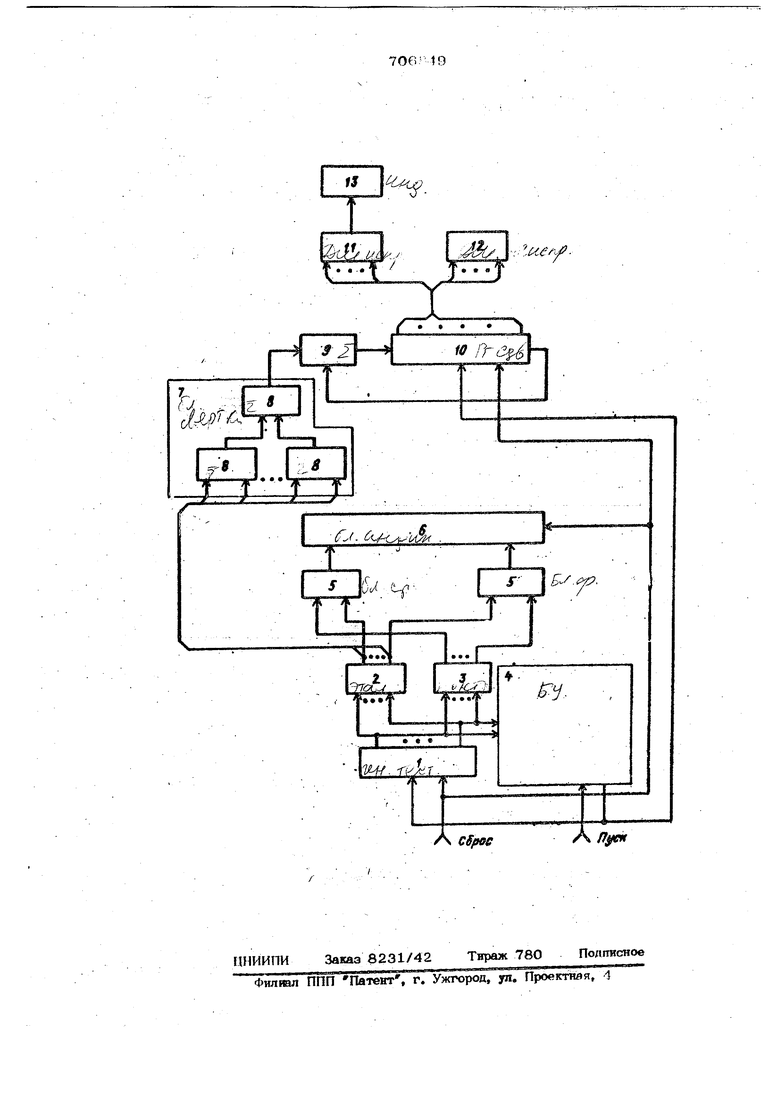

Изобретение относится к области автоматического контроля и днагностаки ра диоэпектронной аппаратуры, может быть использовано в систем контроля, обеспечивая увеличение достоверности и со:кращение временрг проверки партии однотипных издеп1гй. Известно устройство для контроля ци4 |ювых УЗЛОВ, содержащее генератор тестов, выходы которого соединены с эталон HbtM и контролируемым блоками, соединенными своими выходами с входами блоков сравнения, выходы - с блоком регист рации и индикации l. К недостаткам гизвестного устройстнй относятся низкая достоверность KOHTP V. ля, в случае идентичных дефектов в «талонном и проверяемом блоках, и значительная времени при контроле Па тии однотипных и.зделий. Наиболее близкv м техническим решением к изобретению является устройство для контроля ци4ровьтх блокгп 2, со- держащее гчтгоратор т«стор. вь.гхопы кото рсяго подключены к входу блока управления и к входам эталонного и контролируемых блоков, выходы которых через блоки сравнения подключены к блоку регистрации и индикации, выход и первый вход сумматора соединены соответственно с информационным входом и первым выходом регистра сдвига, вторые выходы которого подключены через дешифратор исправности к входу индикатора исправности, а выходы блока управления соединены с управляющими входами генератора тестов и регистра сдвига. Однако в этом устройстве возможна запись информации в регистр только из одного канала контролируемого блока, т.е. в устройстве отсутствует параллельная свертка выходного слова, что существенно увеличивает время контроля при последовательной обработке всех выходов контролируемого блока. Цель изобретеття - повышение 6MCTpv действия устройства. ч706 --..,., J Это достигается тем, что в устрой . ство введены дешифратор неистгравностей и блок пираш1далыюй свертки, входы ко торого подключены к выходам втапотюго блока, выход - к второму входу сумматора, а входы деши4ратора неисправйостей - к вторым выходам регистра сдвига. Блок-схема устройства представле1ю на чертеже. Она содержит генератор 1 тестов, эталонный 2 и контролируемый 3 блоки, блок 4 управления, блоки 5 сравнения, блок 6 регистрации и индикапии, блок 7 пирами дальной свертки, юстроенный из элементов 8 сумма по модулю 2, сумматоо 9, регистр Ю сдвига, дешифратор 11ио правности, дешифратор 12 неисправностей и индикатор 13 исправности. Устройство работает следующим ооразом. При поступлении команды пуск в блок 4 импульсы тактовой частоты поступают на генератор 1 и на вход. Сдвиг регистра 10. Генератор 1 выдает по всем выходам тестовые последовательности, поступающие на идентичные входы эталонного 2 и контролируемого 3 блоков. Ответные реакции блоков 2 и 3 сравниваются между собой блоками 5. В случае рассогласования в каналах контроля сбои регистрирует блок 6. При полном соответ ствии ответных реакций блоков 2 и 3 на тестовые последовательности, срабатывает индикатор блока 6. Выходные пбслёдовательности сигналов с эталонного блока 2 преобразуются в одну последовательнос сигналов при помощи элементов 8 блока 7, после Чего через сумматор 9 aanncbiBa ются в регистр 1О. Информация, которая переполняет |эегистр 10, так как числю разрядов его значительно меньше разрядтности выходной последовательности сигна лов с блока 7, поступает через сумматор 9 на информационный вход регистра lOi Дешифратор 11 и индикатор 13 ерабатывают при истинном значении информа ции, записанной в регистр 10, а дешифратор 12 перекодирует информацию (в tbrty ae искажения) в позиции неисправных элементов. Таким образом, npi контроле циф{ювьгх локор паяным УС-ТТЮЙСТВОМ становится озможным проверять ра отос пособнюсть дновременно двух блоков, получая инфорацию о годности первого из блоков, услового названного эталонным,по реакции, записанной в регистре, а другого - по оъ ветной реакции на входные тесты, сравниваемой первым блоком. Такое решение позволяет увеличить производительность устройства в два раза и исключает возл ожность принятия неисправных блоков с одинаковыми дефектами за исправные, что повышает достоверность контроля. Формула изобретения Устройство для контроля цифровых бЛОь. ков, содержащее генератор тестов, выходы которого подключены к входу блока управления и к входам эталонного и контролируемого блоков, выходы которых через блоки сравнения подключены к блоку регнстраичи и индикации, выход и первый вход сумматора соегшнены соответстве Но с информационным входом и первым выходом регистра сдвига, вторые выходы которого подключены через дешифратор исправности к входу индикатора исправноети, а выходы блока управления соединены с управляющими входа и генератора тестов и регистра сдвига, о т л и ч а KV. щ е (S с я .тем, что, с целью повышения быстродействия устройства, в него введены дешифратор неисправностей и блок пирамидальной свертки, входы которого -подключены к выходам эталонного блока, выход - к второму входу сумматора, а входы дешифратора неисправностей - к вторым выходам регистра сдвига. Источники информации, принятые во внимание при экспертизе 1.Выбор контрольных кодов для проверки цифровых схем на сложных схемных платах. Электроника, № 15, 1972. 2.Локализация неисправностей в микропроцессорных системах при помощи : шестнадцатиричных кодов, с лектроника. № 5, 1977, с, 23-33 (прототип).

I IS

t..-1.1. nilI J

,.

L

™

i.r

a

J J7

fj. .

I

TjoV.

a

0 Гге

B..

Ч

J

,.

/ k

.. .

A /7

A

Авторы

Даты

1979-12-30—Публикация

1978-02-23—Подача