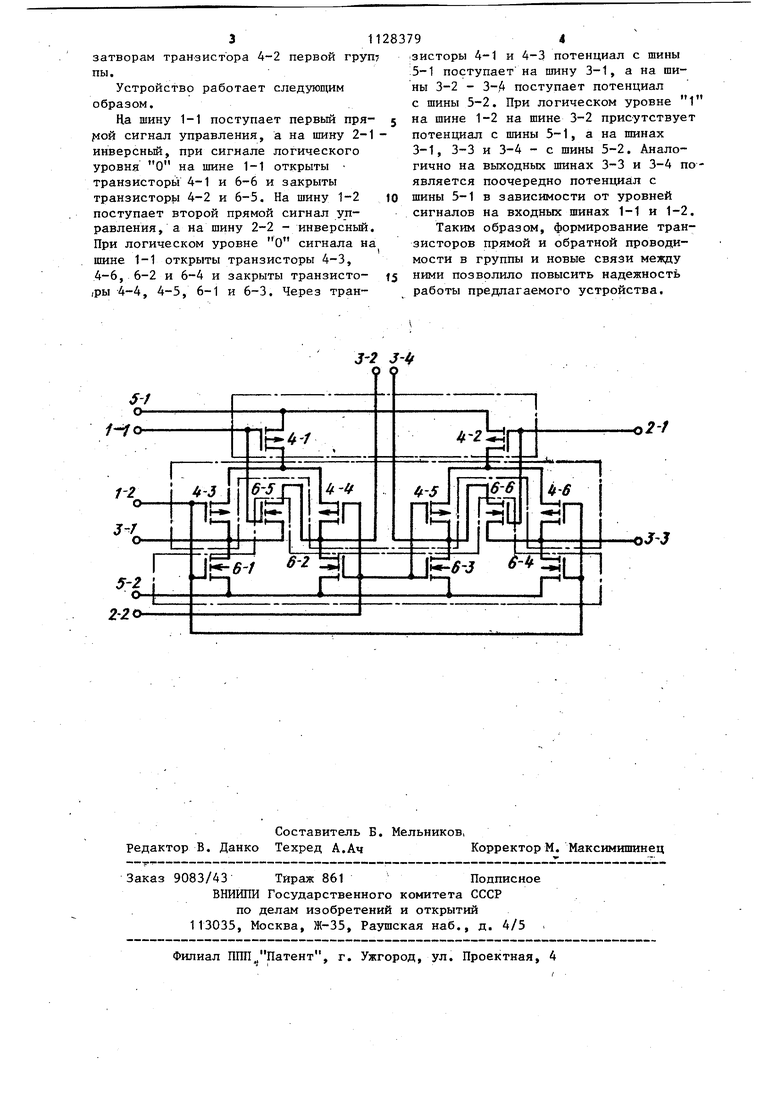

1 Изобретение относится к вычислительной технике и может быть исполь зовано при разработке универсальных и специализированных цифровых вычис лительных машин. Известен дешифратор, содержащий .резисторы, диоды и транзисторы, выходы которых подключены к соответст вующим шинам дешифратор л через диоды lj . Недостатком этого устройства явл ется низкая надежность из-за большо го количества компонентов в схеме. Наиболее близким техническим решением к изобретению является дешиф ратор на МДП-транзисторах, содержащий группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных входов, выходные шины, шины питания и элементы И-НЕ, входы которых подключены к сос5тветствующим шинам прямых и ин версных входов, а выходы соединены с соответствующими выходными шинами Yj . Недостатком известного устройств ва является его низкая надежность. Целью изобретения является повышение надежности. Поставленная цель достигается те что в дешифраторе на МДП-транзисторах, содержащем группы транзисторов прямой и обратной проводимости, шин прямых входов, шины инверсных входовх выходные шины .и шины питания, первая и вторая группы транзисторов состоят из транзисторов прямой, а третья группа - из транзисторов обратной проводимости, истоки транзис торов первой группы соединены с пер вой шиной питания, сток первого транзистбра первой группы - с истоками первого и второго транзисторов второй группы, а его затвор - с пер вой шиной прямого входа, сток второ го транзистора первой группы соединен с истоками третьего и четвертого транзисторов второй группы, а его затвор - с первой шиной инверсного входа, стоки перэого, второго, третьего и четвертого транзисторов третьей группы соединены с второй .шиной питания, затворы второго и третьего транзисторов второй группы с затворами второго и третье- .го транзисторов .третьей группы и с второй шиной инверсного вхо792Да, затворы первый и четвертых транзисторов второй и третьей группы с второй шиной прямого входа, первая выходная шина - со стоками первого транзистора второй группы и пятого транзистора третьей группы,, исток которого соединен со стоком второго транзистора второй группы, истоком второго транзистора третьей группы и второй выходной шиной, затвор пятого транзистора третьей группы соединен с затвором первого транзистора первой группы, третья выходная шина - с истоком четвертого транзистора третьей группы, стоком четвертого транзистора второй группы и стоком шестого транзистора третьей группы, затвор которого соединен с первой шиной инверсного входа, исток шесто- го. транзистора третьей группы соединен с истоком третьего транзистора третьей группы, стоком третьего транзистора второй группы и четвертой выходной шиной. На чертеже представлена принципиальная электрическая схема дешифратора на МДП-транзисторах. Дешифратор содержит шины 1.1 и 1.2 прямых входов, шины 2.1 и 2.2 инверсных входов, выходные шины 3.1- 3.4, транзисторы 4.1 - 4.2, истоки транзисторов 4.1 и 4.2 подключены к первой шине питания, затвор транзистора 4.1 соединен с первой шиной 1.1 прямого входа, затвор транзистора 4.2 с первой шиной 2.1 ицверсного входа, истока транзисторов 4.3 и 4.4 - со стоком транзистора 4-1 первой группы, транзисторы 4.5 и 4.6 истоками подключены к стоку транзистора 4-2 первой группы, стоки транзисторов 4-3 4-6 - соответственно к вькодным шинам 3.1 - 3.4, шины 5-1 и 5-2 - шины питания, причем истоки транзисторов 6-1 - 6-4 подключены к щине 5-2 питания, а затворы - к затвором транзисторов 4-3 - 4-6 второй группы соответственно, затворы транзисторрв 4-3 и 4-5 соединены с второй шиной 1-2 прямого входа, затворы транзисторов 4-4 и 4-6 - с второй шиной 2-2 инверсного входа, между стоками транзисторов 4-3 и 4-4 включен транзистор 6-5, затвор которого подключен к затвору транзисторов 4-1 первой группы, между стоками транзисторов 4-5 и 4-6 включен транзистор 6-6 h-типа, затвор которого подключен к

затворам транзистора 4-2 первой труп пы.

Устройство работает следующим образом,

На шину 1-1 поступает первый сигнал управления, а на шину 2-1 инверсньй, при сигнале логического уровня О на шине 1-1 открыты транзисторы 4-1 и 6-6 и закрыты транзисторы 4-2 и 6-5. На шину 1-2 поступает второй прямой сигнал управления, а на шину 2-2 - инверсньй. При логическом уровне О сигнала на шине 1-1 открыты транзисторы 4-3, 4-6, 6-2 и 6-4 и закрыты транзисто/ры 4-4, 4-5, 6-1 и 6-3. Через транзисторы 4-1 и 4-3 потенциал с шины 5-1 поступает на шину 3-1, а на шины 3-2 - 3-4 поступает потенциал с шины 5-2. При логическом уровне 1 на шине 1-2 на шине 3-2 присутствует потенциал с шины 5-1, а на шинах 3-1, 3-3 и 3-4 - с шины 5-2. Аналогично на выходных шинах 3-3 и 3-4 появляется поочередно потенциал с шины 5-1 в зависимости от уровней сигналов на входных шинах 1-1 и 1-2. Таким образом, формирование транзисторов прямой и обратной проводимости в группы и новые связи между ними позволило повысить надежность работы предлагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Формирователь импульсов | 1983 |

|

SU1123056A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064471A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Тактируемый Е-триггер | 1987 |

|

SU1492454A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Формирователь импульсов на МДП-транзисторах | 1987 |

|

SU1473072A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

ДЕШИФРАТОР НА МДП-ТРАНЗИСТОРАХ, содержащий группы транзисторов прямой и обратной проводимости, шины прямых входов, шины инверсных входов, выходные шины и шины питания, о тчличающийся тем, что, с целью повьшения надежности, первая и вторая группы транзисторов состоят из транзисторов прямой, а третья группа - ИЗ транзисторов обратной проводимости, истоки транзисторов первой группы соединены с первой шиной питании, сток первого транзистора первой г|)уппы соединен с истоками первого и второго транзисторов второй группы, а его затвор соединен с первой шиной прямого входа, сток второго транзистора первой группы соединен с истоками третьего и четвертого транзисторов второй группы. а его затвор - с первой шиной инверсного входа, стоки первого, второго третьего и четвертого транзисторов третьей группы соединены с второй шиной питания, затворы второго и третьего транзисторов второй группы соединены с затворами второго и третьего транзисторов третьей группы и с второй шиной инверсного входа, затворы первых и четвертых транзисторов второй и третьей группь соеди- нены с второй шиной прямого входа,первая .выходная шина соединена со стоками первого транзистора второй группы и пя.того транзистора третьей группы, исi ток которого соединен со стоком второго транзистора второй группы, истоком второго транзистора третьей группы и второй выходной шиной, затвор пятого транзистора третьей группы соединен с затвором первого транS зистора первой группы, третья выходная шина соединена с истоком четвертого транзистора -третьей группы, стою ком четвертого транзистора второй Х группы и стоком шестого транзистора э ч ;о третьей группы, затвор которого соединен с первой шиной инверсного вхоi;t,исток йёстого. транзистора третьей Ьруппы соединен с истоком третьего транзистора третьей группы, стоком третьего транзистора второй группы и четвертьй выходной шиной.

Авторы

Даты

1984-12-07—Публикация

1983-01-10—Подача