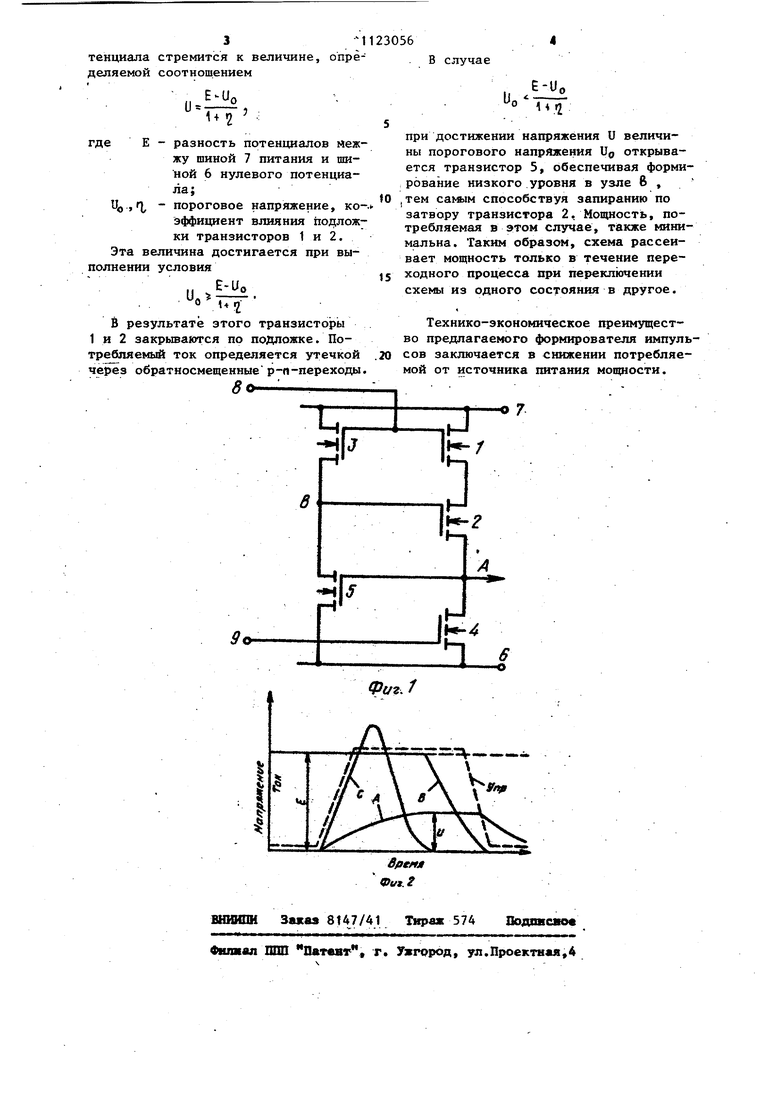

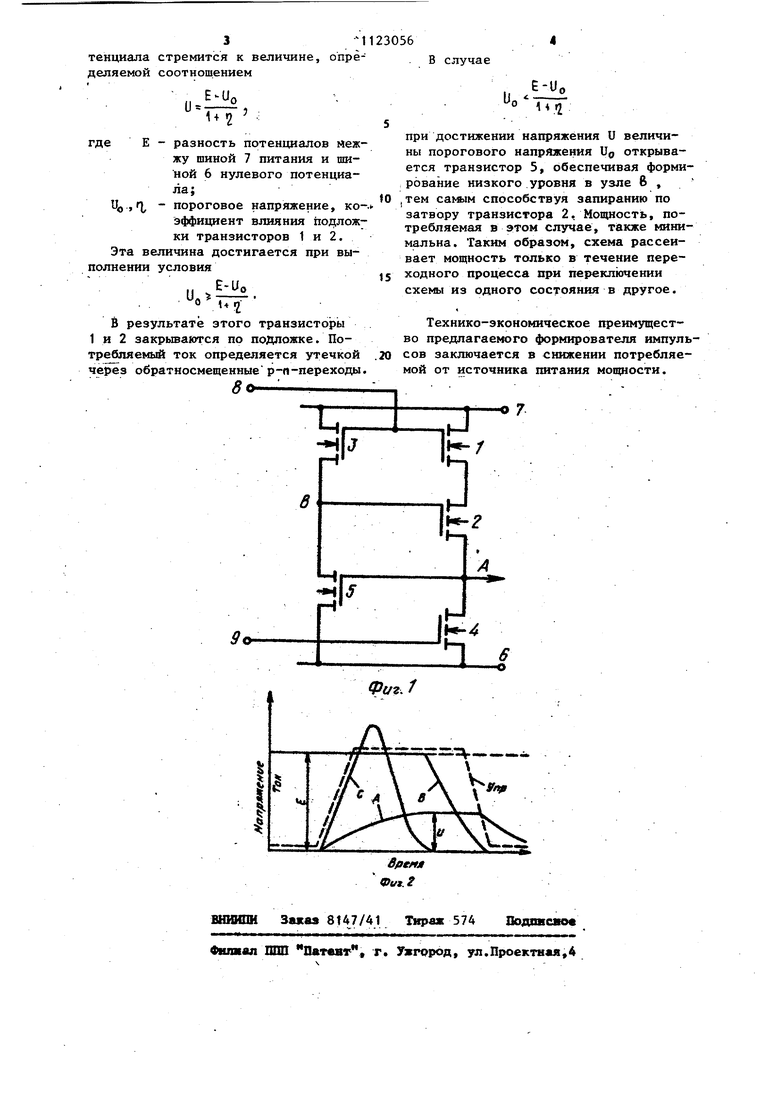

Изобретение относится к вычислительной технике и электронике и может быть использовано при построении устройств для считьшания информации из накопителей запоминающих устройст в качестве элемента, осуществляющего подзаряд емкостей, образуемых шинами данных. Известен формирователь импульсов для подзаряда емкостей, содержащий пару последовательно включенных ВДПтранзисторов, причем затвор и сток одного из транзисторов объединены tl 1 Недостатком данного устройства является непроизводительное потребле ние мощности источника питания за счет протекания сквозного тока через пару транзисторов в режиме формирова ния уровня предварительного заряда. Наиболее близким по технической сущности к изобретению является формирователь импульсов,. срдержакр1й последовательно включенные между шиной питания и общей шиной первый, второй МДП-транзистрры р-типа проводимости и третий, четвертый 1Щ1транзисторы п -типа проводимости, причем затворы первого и четвертого Щ11-транзисторов соединены со стоками второго и третьего ВДП-транзисторов, затворы которых являются соответственно инверсным и прямым управляюпщми входами С 2. Недостатком известного устройства является рассеяние мoщнoctи истояника питания в течение времени деист- . вяя управляющего импульса, обусловленное CKBosHbiM током через открытые транзисторы. Целью изобретения является снижение потребляемой мощности формирователя импульсов. Поставленная цель достигается тем, что в формирователь импульсов, содержащей первый и второй ЩЩ-транзисторы п-типа проводимости, третий 1ЗдП-траязистор р-типа проводимости, шину питания и шину нулевого потенциала причем исток первого зистора п-типа проводимости соединен со стоком второго МДП-транзистОра И-типа проводимости, затвор которого соединен со стоком третьего МДП-тран эистора р-типа проводимости, затвор первого ЩЩ транэистора и -типа проводимости является первым управляющим входом устройства, а сток соединен с шиной питания, введены четвертый и пятый МДП-транзисторы м-типа проводимости, причем исток третьего МДП-транзистора р-типа проводимости соединен с шиной питания-,. а. затвор с затвором первого МДП-транзистора П-типа про.водимости, истоки четверто го и пятого .МДП-транзисторов п -типа проводимости подключены к шине нулевого потенциала, затвор четвертого ОДП-транзистора и-типа проводимости является вторым управляющим входом устройства, сток четвертого ВДПтранзйстора п-типа проводимости соединен с истоком второго ЙЦП-траязистора П-типа проводимости и с затво,ром дятого ЩП-тран9Истор а я -типа проводимости, сток которого соединер ,со стоком третьего ВДП-транзистора р-типа проводимости. . На фиг. 1 представлена схема предлагаемого устройства; на .фиг. 2 кривые переходных процессов. Формирователь импульсов содержит первый 1 и второй 2 ВДП-транзисторы И-типа проводимости, третий 3 ВДПтранзистор р-типа проводимости, четвертый 4 и пятый 5 МИД-Транзисторы п-типа проводимости, шину 6 нулевого потенциала, шину 7 питания, шины 8 и 9 управления (входа). Устройство работает в .режиме начальной установки ив режиме подзаряда. В реЯиме. начальной установки на управлякйцих входах 8 и 9 установлены противопол хкные логические уровни О и t, открывакяцие транзисторы 3 и 4. : Открытые траэисторы обеспечивают в точках АИ Б формирова1ше уровней, -соответствукиих пOтeнциaJтa f шин 6 и 7 (tmsKfiA и высокий) соответqTBeHtfo. Потенциал узла А(низкий) является запирающим по отношеншо к . транзистору 5, поэтому схема представляет комплементарную структуру; величина потребляемого от источника питания тока определяется только токами утечки. В режиме подзаряда на управляш(их входах 8 и 9 установлены соответственно противоп.оложные логические уровни 1 и О, закрывающие транзисторы 3 и 4. Открьгоающийся при этом первый 1 транзистор и открытый пятый 5 транзистор обеспечивают изменение потенциала узла А. Напряжение между узлом А и шиной 6 нулевого по34123056

тенциала стремится к величине, определяемой соотношением

-разность потенциалов межгдежу шиной 7 питания и шиной 6 нулевого потенциала;

о. а

-пороговое напряжение, ко-эффициент влияния подложу ки транзисторов 1 и 2.

Эта величина достигается при выполнении условия

E-UO

2

в результате этого транзисто:ры 1 и 2 закрываются по подложке. Потребляемый ток определяется утечкой че:рёз обратносмещенные р-п-переходы.

9о-:-..

В случае

при достижении напряжения U величины порогового напряжения UQ открывается транзистор 5, обеспечивая формирование низкого уровня в узле 8 ,

,тем способствуя запиранию по затвору транзистора 2, Мощность, потребляемая в этом случае, также минимальна. Таким образом, схема рассеивает мощность только в течение переходного процесса при переключении из одного состояния в другое.

Технико-экономическое преимущество предлагаемого формирователя импульсов заключается в снижении потребляемой от источника питания мощности.

ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Формирователь импульсов для блоков памяти | 1985 |

|

SU1278973A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Формирователь импульсов | 1984 |

|

SU1226527A1 |

| Электронный ключ | 1985 |

|

SU1274147A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ, содержащий первый и второй МДП-транзисторы п-типа проводимости, третий МДП-транзистор р-типа проводимости, шину питания и пину нулевого потенциала, причем исток первого ОДПтранзистора и-т1ша проводимости соединен со стоком второго МДП-транзистора п-типа проводимос-ги, затвор которого соединен со стоком третьего ЩП-транзистора р-типа проводимости, затвор первого МДП-транзистора и проводимости является первым управляющим входом устройства, и сток соединен с шиной питания, отличающийся тем, что, с цепью снжкения потребляемой мощности, в него введены четвертый и пятый МДПтранзисторы п-типа проводимости, причем исток третьего МДП-транзистора р-типа проводимости соединен с шиной питания, а затвор - с затвором первого МДП-транзистора п-типа проводимости, истоки четвертого и пятого ЩЩ-транзисторов п-типа проводимости подключены к шине нулевого потенциала, затвор четвертого МЩ1-транзистора и-типа проводимости является вторым управляющим входом устройства, сток четвертого МДП-транзистора п-типа проводимости соединен с истоком второго ОДП-транзистора «-типа проводимости и с затвором пятого МДП-транзистора 1 -типа проводимости, сток которого соединен со стоком третьего МДП-транзистора р-типа проводимости.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4025801, - G j.tC 7/00, опублик | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент Великобритании | |||

| СПОСОБ СОЗДАНИЯ ГОМОЗИГОТНЫХ ЛИНИЙ РЖИ | 1992 |

|

RU2028044C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1984-11-07—Публикация

1983-08-22—Подача