Изобретение относится ic вычислительной технике и может быть использовано при разработке эапоминанздих устройство ЭВМ и систем хранения и переработки информации.

Цель изобретения - сокращение аппаратурных затрат.

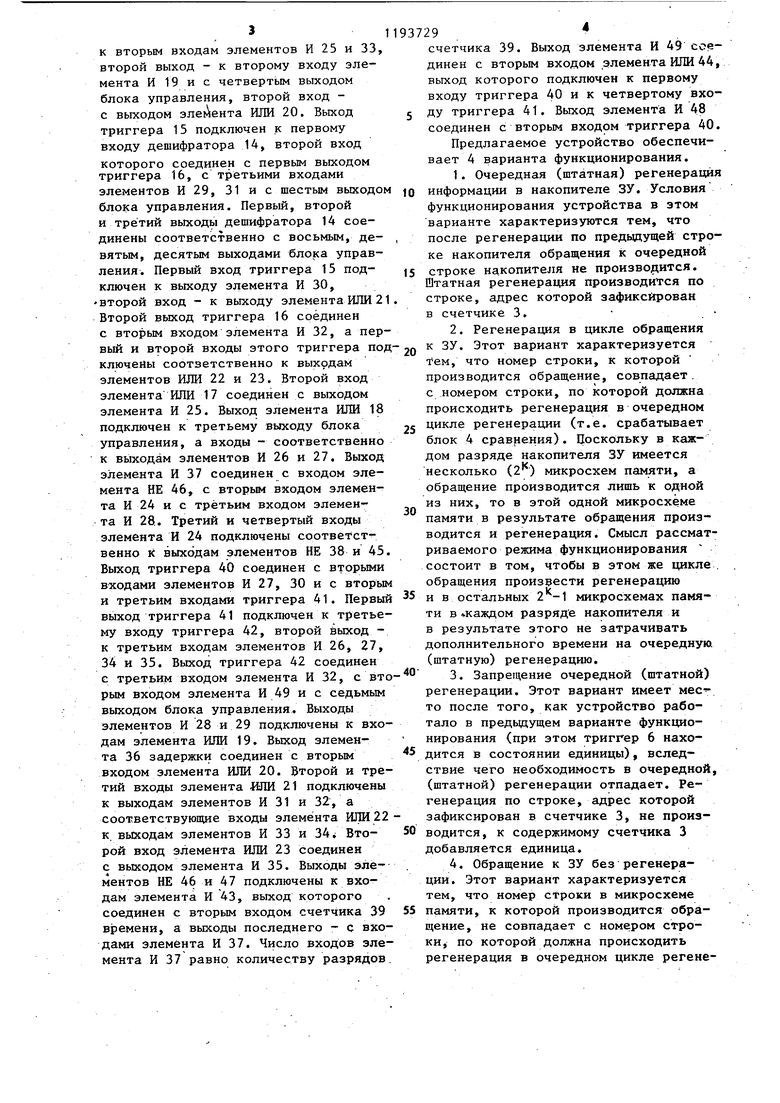

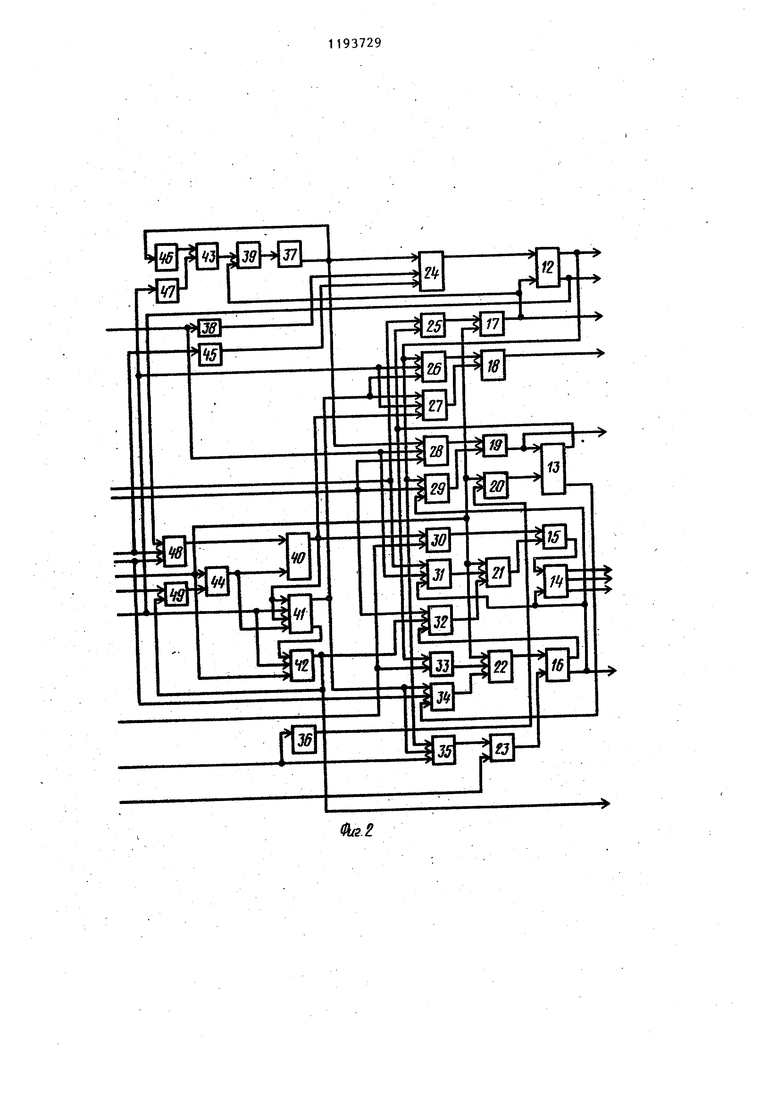

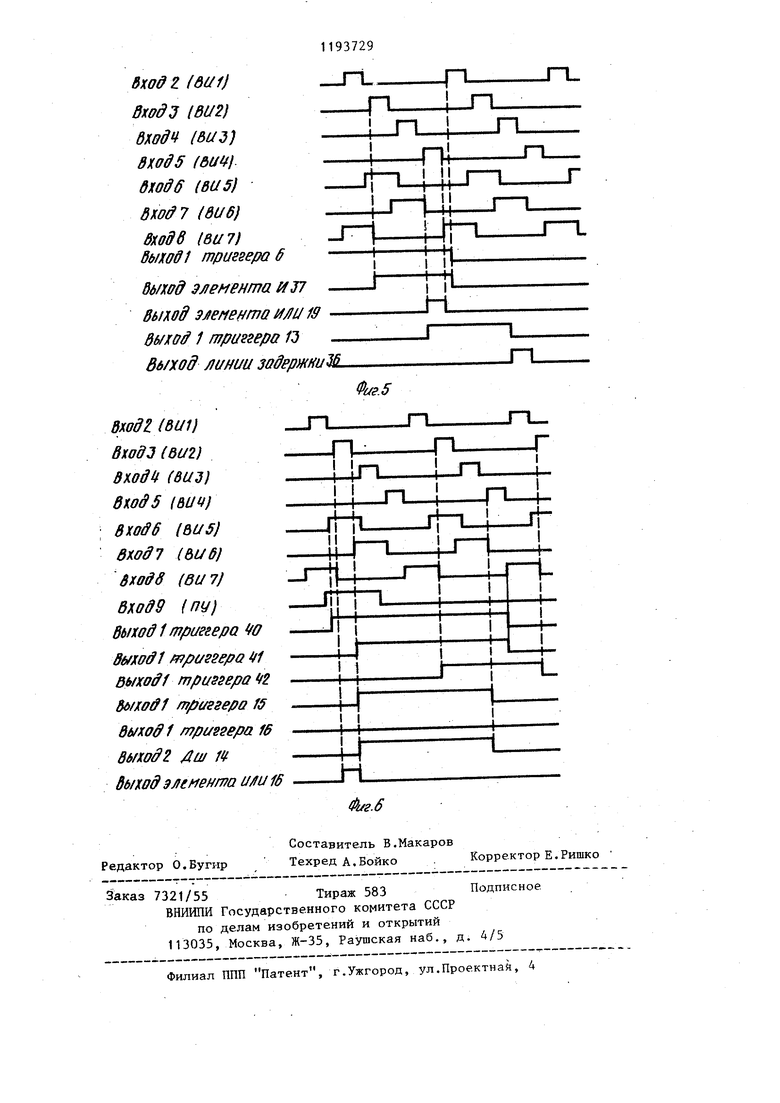

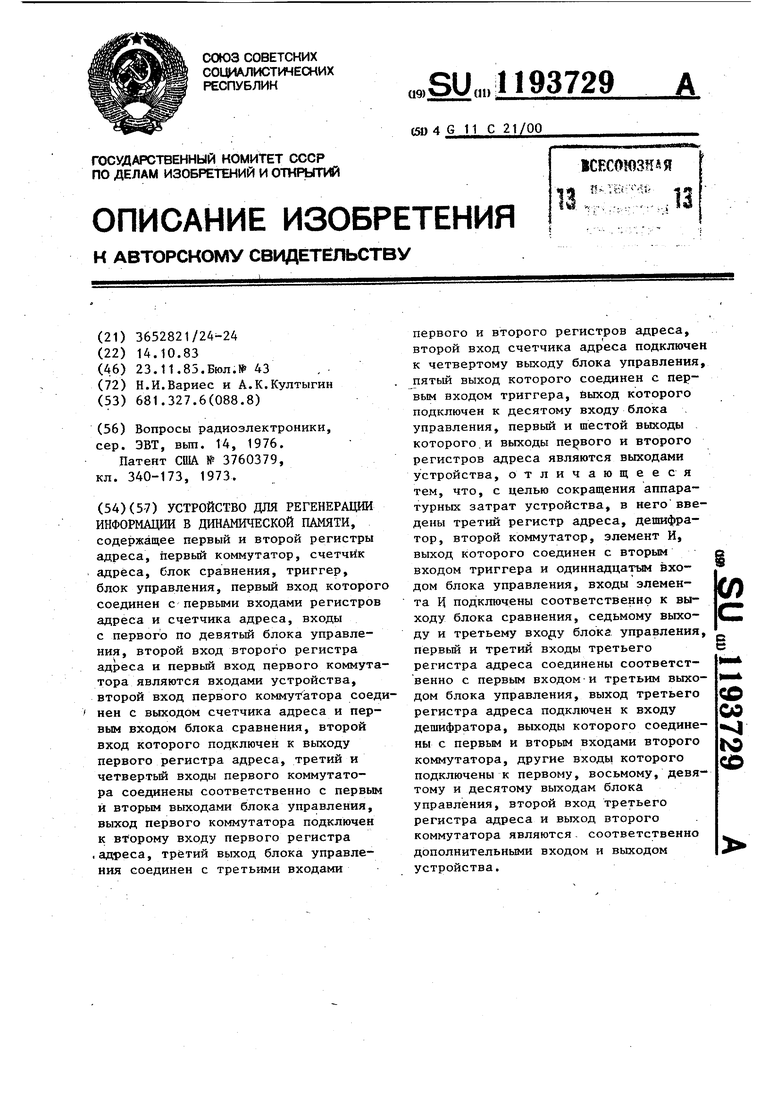

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока управления} на фиг. 3 - 6 временные диаграммы работы устройства. . .

Устройство содержит первый регистр 1,адреса, первый коммутатор 2, счетчик 3 адреса, блок 4 сравнения, второй регистр 5 адреса, триггер 6, блок 7 управления, третий регистр 8 адреса, дешифратор 9, второй коммутатор 10, элемент И 11.

Регистр 1 и счетчик 3 содержит п разрядов каждый, где п - количество двоичных разрядов, определяющих номер (адрес) строки в микросхемах, накопителя. В соответствии с этим нижеперечисленные соединения представляют собой совокупность п однотипных шин: десятого входа устройства с первым входом коммутатора 2; выхода коммутатора 2 с вторым входом регистр а 1; выхода счетчика 3 с вторым входом коммутатора 2 и с первым входом блока 4 сравнения; выхода регистра 1 с третьим выходом устройства и с вторым входом блока 4 сравнения.

Регистр 5 содержит m разрядов, где in - количество двоичных разрядов определякщих номер (адре.с) столбца в микросхемах накопителя. В соответствии с этим нижеперечисленные соединения представляют собой совокупность m однотипных шин$ одиннадцатого входа устройства с вторым входом регистра 5; выхода регистра 5 с четвертым вьпсодом устройства.

В зависимости от конфигурации накопителя m может быть равно или не равно п.

Регистр 8 содержит К разрядов, где К количество двоичных разрядов, определяющих номер (адрес) микросхемы памяти в каждом разряде накопителя. В соответствии с этим соединения двенадцатого входа устройства с вторым входом регистра 8 и выхода регистра 8 с входом дешифратора 9 представляют собой совокупность К однотипных шин, а соединения каждого из выходов дешифратора 9 с соответствующими входами коммутатора 10 представляют собой совокупность 2 однотипных шин. Третий вход коммутатора 10 так же, как первый и второй, имеет 2 контакта, однако все они объединены между собой, так что соединение третьего входа коммутатора 10 и первого выхода блока 7 управления представляет собой одну шину. Все остальные соединения на фиг. 1, не указанные вьш1е, также представляют собой одну шину. Блок 7 управления содержит R-S-триггеры 12 и 13, дешифратор 14, R-Sтриггеры 15 И 16, элементы ИЛИ 17 23, элементы И 24 - 35, элемент 36 задержки, элемент И 37, элемент НЕ 38 счетчик 39 времени, R-S-триггер 40, двухтактный J-К-триггер 41, D-триггер 42, элемент И 43, элемент ИЛИ 44, элементы НЕ 45 - 47, элементы И 48 и 49.

Первый вход блока управления соединен с первыми входами элементов ИЛИ 17, 20, 21, 22, 44 и триггера 42; второй вход - с первыми входами элементов И 25 и 31; третий вход - с первыми входами элементов И 26 и 27, триггера 41, с входом элемента НЕ 47 и с вторым .входом триггера 42; четвертый вход с первым входом элемента И 35 и с входом элемента 36 задержки; пятый вход - с первыми входами элементов И 28, 29, 32; шестой вход с первыми входами элементов И 34 и 48; седьмой вход - с первыми входами элементов И 30 и 33; восьмой - с первым входом элемента И 49; девятый вход - с вторым входом элемента И 48 и с входом элемента НЕ 45; десятый вход - с вторыми входами элементов И 28 и 31 и с входом элемента НЕ 38; одиннадцатый вход - с первым входом элемента ИЛИ 23. Первый выход триггера 12 подключен к первому выходу блоЛа управления и к вторым входам элементов И 26, 29 и 35, второй выход к второму выходу блока управления и к третьему входу элемента И 48. Первый вход триггера 12.соединен с выходом элемента И 24, второй вход - с выходом элемента ИЛИ 17, с первым входом счетчика 39 и с пятым выходом блока управления. Первый выход триггера 13 подключен к вторым входам элементов И 25 и 33, второй выход - к второму входу элемента И 19 и с четверть1м выходом блока управления, второй вход с выходом злеАента ИЛИ 20. Выход триггера 15 подключен к первому входу дешифратора 14, второй вход которого соединен с первым выходом триггера 16, с третьими входами элементов И 29, 31 не шестым выходо блока управления. Первый, второй и третий выходы дешифратора 14 соединены соответственно с восьмым, девятым, десятым выходами блока управления. Первый вход триггера 15 подключен к выходу элемента И 30, второй вход - к выходу элемента ИЛИ 2 Второй выход триггера 16 соединен с вторым входом элемента И 32, а пер вый и второй входы этого триггера под ключены соответственно к выхрдам элементов ИЛИ 22 и 23. Второй вход элемента ИЛИ 17 соединен с выходом элемента И 25. Выход элемента ИЛИ 18 подключен к третьему выходу блока управления, а входы - соответственно к выходам элементов И 26 и 27. Выход элемента И 37 соединен с входом элемента НЕ 46, с вторым входом элемента И 24 и с третьим входом элемента И 28. Третий и четвертый входы элемента И 24 подключены соответст венно к выходам элементов НЕ 38 и 45 Выход триггера 40 соединен с вторыми входами элементов И 27, 30 и с вторым и третьим входами триггера 41. Первый выход триггера 41 подключен к третьему входу триггера 42, второй выход к третьим входам элементов И 26, 27, 34 и 35. Вькод триггера 42 соединен с третьим входом элемента И 32, с вто рым входом элемента И 49 и с седьмым выходом блока управления. Выходы элементов И 28 и 29 подключены к входам элемента ИЛИ 19. Выход элемента 36 задержки соединен с вторым входом элемента ИЛИ 20. Второй и третий входы элемента ИЛИ 21 подключены к выходам элементов И 31 и 32, а соответствующие входы элемента ИЛИ 22 к. выходам элементов И 33 и 34 Второй вход элемента ИЛИ 23 соединен с выходом элемента И 35. Выходы элементов НЕ 46 и 47 подключены к входам элемента И 43, выход которого соединен с вторым входом счетчика 39 времени, а выходы последнего - с входами элемента И 37. Число входов элемента И 37 равно количеству разрядов 29 . счетчика 39. Выход элемента И 49 соединен с вторым входом элемента ИЛИ 44, выход которого подключен к первому входу триггера 40 и к четвертому входу триггера 41. Выход элемента И 48 соединен с вторым входом триггера 40. Предлагаемое устройство обеспечивает 4 варианта функционирования. 1. Очередная (штатная) регенерация информации в накопителе ЗУ. Условия функционирования устройства в этом варианте характеризуются тем, что после регенерации по предыдущей строке накопителя обращения к очередной строке накопителя не производится. Штатная регенерация производится по строке, адрес которой зафиксирован в счетчике 3. 2. Регенерация в цикле обращения к ЗУ. Этот вариант характеризуется Тем, что номер строки, к которой производится обращение, совпадает . с номером строки, по которой должна происходить регенерация в очередном цикле регенерации (т.е. срабатывает блок 4 сравнения). Поскольку в каждом разряде накопителя ЗУ имеется несколько (2) микросхем памяти, а обращение производится лишь к одной из них, то в этой одной микросхеме памяти в результате обращения производится и регенерация. Смысл рассматриваемого режима функционирования состоит в том, чтобы в этом же цикле, обращения произвести регенерацию и в остальных 2-1 микросхемах памяти в каждом разряде накопителя и в результате этого не затрачивать дополнительного времени на очередную1 (штатную) регенерацию. 3. Запрещение очередной (штатной) регенерации. Этот вариант имеет мес то после того, как устройство работало в предыдущем варианте функционирования (при этом триггер 6 находится в состоянии единицы), вследствие чего необходимость в очередной, (штатной) регенерации отпадает. Регенерация по строке, адрес которой зафиксирован в счетчике 3, не производится, к содержимому счетчика 3 добавляется единица. 4. Обращение к ЗУ без регенерации . Этот вариант характеризуется тем, что номер строки в микросхеме памяти, к которой производится обраение, не совпадает с номером строи, по которой должна происходить регенерация в очередном цикле регене $ рации (блок 4 сравнения не срабатывает, триггер 6 находится в состоянии нуля), . Рассмотрим подробно работу устройства в четырех вариантах функцио нирования. Перед началом работы происходит установка в нулевое состояние регистров 1,5 и 8, счетчиков 3 и 39, триггеров 6, 12, 13, 15, 16, 40, 41 42 сигналом, поступакицим на первый вход устройства (и соответственно на первый вход блока 7 управления). Сигнал установки в нулевое состояние с первого входа устройства попадает непосредственно на соответствующие входы регистров 1, 5 и 8 и счетчика 3; с первого входа бло|са 7 он попадает также на входы триггеров 40, 41, 13, 15, 16, 12 и счетчика 39 через элементы ИЛИ 44, 20, 21, 17, а на вход триггера 6 через элемент ИЛИ 1.7 и пятьй выход блока управления. Временная диаграмма работы устрой ства по первому варианту - очередной ((штатная регенерация)|информации представлена на фиг. .3. В этом варианте устройство работает следующим образом. Временной импульс ВЧ2, подаваемый на третий вход блока 7 управления, через элемент НЕ 47 и элемент И 43 проходит на счетный вход счетчика 39 времени и устанавливает его в состоя ние, соответствующее моменту проведе ния регенерации информации по очеред ной строке накопителя. После окончания переходных процессов в счетчике 39 срабатьшает элемент И 37, т.е на его выходе появляется сигнал единицы; выходной сигнал элемента И 37 (через элемент НЕ 46) закрывает элемент И 43, так что запрещается подача импульсов на счетный вход счетчика 39 времени, и вызьшает срабатывание элемента И 24, так как на остальных двух входах этого элемента, соединенных с выходами элементов НЕ 38 и 45, в данный момент присутствуют разрешающие потенциалы (на десятом входе блока управления потенциал равен нулю из-за того, что триггер 6 находится в нулевом соетоянии, а на девять1й вход блока управления нулевой потенциал посту.пает извне). Вследствие этого переключается в состояние единицы триг296гер 12. Сигнал логической единицы с первого выхода этого триггера через первьш выход блока 7 поступает на первый выход устройства, на третий (управляющий) вход коммутатора 2, на 2 шины третьего (информационного) входа коммутатора 10, а в блоке 7 - на вторые входы элементов И 26, 29 и 35. При этом через коммутатор 2 на информационные входы регистра 1 поступают сигналы с выхода счетчика 3, на информатдионные входы регистров 5 и 8 поступает нулевая информация, так как на одиннадцатом и двенадцатом входах устройства нулевая информация. По ВИ 2 в блоке 7 формируется управляющий сигнал записи в регистры 1, 5 и 8 (цепь - элементы И 26, ИЛИ 18, третий выход блока 7), при этом в регистр 1 записывается информация, соответствующая состоянию счетчика 3 (т.е. номер строки, по которой должна производиться регенерация), а в регистры 5, 8 - нулевая информация. Триггеры 40 и 41 остаются в нулевом состоянии, вследствие этого остается в нулевом состоянии и триггер 15, а триггер 16 переводится в единичное состояние управляющим сигналом, формируемым в цепи элементов и 35, ИЛИ 23 по НИ 3, поступающему на четвертые входы устройства и блока 7 управления. Сигналы, поступакщие с первых выходов триггеров 15 и 16, дешифрируются, и на первом выходе дешифратора 14 формируется сигнал, подаваемый на восьмой выход блока 7 и управляющий прохождением сигналов логической единицы с 2 шин третьего входа коммутатора 10 на пятьй выход устройства. Таким образом, на первом вькоде устройства имеется сигнал единицы, определяющий проведение штатной регенерации, на втором выходе - сигнал единицы, поступающий с первого выхода триггера 16 через шестой вькод блока 7, блокирующий режимы записи или считывания в накопителе, на третьем выходе - код адреса строки, в которой необходимо произвести регенерацию информации, на четвертом выходе - нулевой код, на пятом выходе (соединяемом с входами Выбор микросхемы микросхем памяти) - сигналы логической единицы, позволяющие осуществить регенерацию во всех микросхемах накопителя. В конце цикла регенерации в блоке 7 формиру ся управляющий сигнал (по ВИ 4), по ступающий на первый вход триггера 1 и через четвертый выход блока 7 упр ления на второй (счетный) вход счет чика 3 (элементы И 29, ИЛИ 19). По этому сигналу в счетчике 3 устанавливается код номера строки, в которой необходимо произвести регенерацию в следующий раз, и изменяется состояние триггера 13. Разрешающий сигнал логической единицы с первого выхода триггера 13 поступает на вторые входы элементов И 25 и 33. По ВИ1 (фиг. 3) в блоке 7 управления формируется сигнал установки в нулевое состояние триггера 12 и счетчика 39 времени (цепь - второ вход блока 7, элементы И 25, ИЛИ 17 При этом на первом выходе устройств появляется сигнал логического нуля, фиксирующий окончание цикла очерёдной регенерации, после установки в нулевоесостояние счетчика време. ни разблокируется цепь подачи счетны импульсов на его вход - для определ ,нйя момента следующей штатной реген рации. Кроме того, по ВИб формирует ся сигнал установки в нулевое состоя ние триггера 16 (цепь - седьмой ; вход блока 7, элементы И 33, ИЛИ-22) а по ВИЗ, задержанному элементом 36 задержки, - сигнал установки триггера 13 в нулевое состояние (цепь - четвертый вход блока 7, элемент 36 задержки, элемент ИЛИ 20). Временная диаграмма работы устройства по второму варианту функционирования (регенерация в цикле обращения к ЗУ) представлена на фиг. 4. I . . В этом варианте состояние счетчика 39 не соответствует моменту штатной регенерации, так что на выходе элемента И 37 имеет место сигнал логического нуля. Триггер 12 находит ся в нулевом состоянии. Сигнал логической единицы с второго выхода триг гера 12 поступает на четвертый управляющий вход коммутатора 2 (через второй выход блока 7) и на третий вход элемента И 48. На девятый вход устройства (блока 7) поступает сигнал обращения к ЗУ, а на шестой вход блока 7 - ВИ5, при совпадении этих сигналов срабатывают элемент И 48 и соответственно триггер 40 Сигнал логической единицы с выхода 729.8 триггера 40 поступает на вторые входы элементов И 27 и 30. На информацнонные входы регистров 5 и 8 поступают сигналы с одиннадцатого и двенадцатого входов устройства, соответствующие номеру .столбца в микросхеме памяти и номеру микросхемы памяти. Hai информационные входы регистра 1 через коммутатор 2 поступают сигналы с десятого входа устройства, соответствующие номеру строки в микросхеме памяти. В блоке 7 по ВИ2 формируется управляющий сигнал, по которому производится запись информации в регистры 1, и 8 (цепь - элементы И 27, ИДО 18, третий выход блока 7); по ВИ6 элементом И 30 формируется управлякяций сигнал, по которому срабатывает триггер 15. При этом на втором выхо- де дешифратора 14 формируется управляющий сигнал, поступающий -на девятьш выход блока 7, а затем на пятый вход коммутатора 10, и на выход этого коммутатора (на пятый выход устройства) проходят сигналы с второго, .выхода дешифратора 9, представляюидаё собой дешифрованный код адреса микросхемы памяти в накопителе,. к которой должно произойти обращение. На третий и четвертьй выходы устрой- ства с регистров 1 и 5 подаются сигналы кода адреса элемента памяти в микросхеме накопителя, на первый и второй выходы устройства - сигналы логического нудя (что означает сообщение об отсутствии режима штатной регенерации и разрешение обращения) . Перечисленные сигналы, подаваемые а выходы устройства, поступают на оответствующие входы ЗУ и обеспеивают обращение (запись или считыание) к одной из микросхем в каждом азряде накопителя. В выбранных икросхемах, в соответствии с принипом их работы, при этом осуществяется регенерация информации во сех запоминающих элементах выбраной строки. Следующий этап работы стройства должен обеспечить регеерацию информации по той же строке о всех остальных 2 -1 микросхемах амяти в каждом разряде накопителя. При работе устройства в варианте егенерации в цикле обращения коды регистре 1 и в счетчике 3 совпа- . ают, поэтому на выходе блока 4 срав-

9 ,

нения имеет место сигнал логической единицы. Сигнал единицы с выхода триггера 40 является разрешающим для срабатывания триггера 41, Последний срабатывает по фронту ВИ2, а сигнал с его первого выхода, поступаиций на третий вход (D-вход) триггера 42, вызывает срабатывание этого триггера, по фронту t следующего ВИ2. После срабатывания триггера 42 по ВИ2 элементом И 11 формируется управляющий сигнал, которьй изменяет состояние триггера 16 (цепь - элемент И 11, одиннадцатый вход блока 7, элемент ИЛИ 23). При этом времеиной импульс ВИ2 должен иметь длительность, не меньшую суммы времен срабатывания триггеров 42 и. 16. Срабатывание триггера 16 приводит к тому, что на втором выходе устройства формируется сигнал логической единицы, запрещаюпщй работу ЗУ в режиме записи или считьгоания и разрешаняций (совместно с сигнала ми на пятом выходе устройства) регенерацию в 2 -1 микросхемах памяти. Кроме того, исчезает управлякидий сигнал на втором выходе дешифратора 14 и появляется управляющий сигнал на его третьем выходе, которьй через десятый выход 6noka 7 поступает на шестой вход.коммутатора 10. При этом на выход коммутатора 10 (на пятый выход устройства) проходят сигналы с первого вьпсода дешифратора 9, которые являются инверсией Сигналов на втором выходе этого деЫифратора. Пepgчиcлeнныe сигналы Юбеспечивают регенерацию информации и микросхемах памяти, которые бьши иевыбранными при обращении к ЗУ.

Для установки в нулевое состояние триггеров 15, 16, 40, 41 и 42 в блоке 7 формируются следующие сигналы: по ВИ7 - сигнал, устанавливающий в нулевое состояние триггеры 40 и 41 Хцепь - восьмой вход блока 7, триггер 42, элементы И 49, ИЛИ 44); по ВИ1 - сигнал, поступающий иа второй вход триггера 15 (цепь - второй вход блока 7, элементы И 31, ИЛИ 21); по ВИ5 - сигнал, устанавливающий в нулевое состояние триггер 16 (цепьшестой вход блока 7, элементы И 34, ИЛИ 22); D-триггер 42 устанавливаетс в нулевое состояние по ВИ2, так как на D-вход этого триггера поступает сигнал логического нуля с первого выхода триггера 41.

10

193729

Триггер 6, установленный в единичное состояние после срабатывания триггера 42 (цепь - триггер 42, седьмой выход блока 7, блок 4 сравнения, элемент И 11), остается в нем до момента, когда счетчик 39 времени фиксирует, необходимость проведения штатной регенерации. В этот момент устройство .начинает работать в третьем варианте функционирования - запрещения штатной регенерации.

Временная диаграмма работы устройства в этом варианте представлена на фиг. ,5.

Триггер 6 находится в единичном состоянии, счетчик 39 времени по ВИ2 установлен в состояние, определяющее jMOMeHT проведения штатной (очередной) регенерации, так что на выходе элемента И 37 сформирован сигнал логической единицы. Этот сигнал указывает на необходимость проведения регенерации информации (и запрещения обращения к ЗУ), однако единичное состояние триггера 6 свидетельствует о том, что регенерация информации ino данной строке уже проведена (при обращении к ЗУ), так что проводить ее еще раз нецелесообразно. Регенера ,ция должна быть заблокирована, номер строки микросхемы накопителя в счетчике 3 изменен, счетчик 39 времени .должен быть установлен в нулевое состояние, запрещения обращения к ЗУ не должно быть. Это происходит следующим образом.

- Сигналы логической единицы с выхода триггера 6 и элемента И 37 поступают на элемент И 28, которьш срабатывает по ВИ4, и на выходе элемента ИЛИ 19 формируется сигнал, по которому изменяется состояние счетчика 3 и триггера 13. В счетчике 3 устанавливается код номера строки (на единицу больше предьщущего), в которой нужно будет произвести регенерацию в следующий раз. Элемент И-24 не срабатьшает, так как на его входе, соединенном с выходом элемента НЕ 38, нулевой потенциал, Триггер 12.остается в нулевом состоянии, и нулевой потенциал на первом выходе устройства не запрещает обращения к ЗУ. Кроме того, запрещается срабатывание элемента И 35, триггер 16 остается в нулевом состоянии, вследствие чего на втором и пятом выходах устройства остаются нулевые сигналы, запрещающие штатную регенеIIрацию. Сигнал логической единицы с первого выхода триггера 13 поступает на второй вход элемента И 25, и в блоке 7 по ВИ1 формируется управляющий сигнал, по которому устанавливаются в нулевое состояние счетчик 39 времени и триггер 6 (цепь - элемейты И 25, ИЛИ 17, пятый выход блока 7). Установка в нулевое состояние триггера 13 описана при работе устройства по первому варианту. Временная диаграмма работы устрой ства по четвертому варианту (обращение к ЗУ без регенерации) представле на на фиг. 6. Работа устройства по этому вариан ту протекает аналогично работе устройства на первом этапе второго вари анта: на первый и второй выходы устройства подаются сигналы логического 2912 нуля, что означает запрет регенерации и разрешение обращения,, на третий и четвертьй выходы - код адреса запоминающего элемента в микросхеме памяти, на пятьш - расшифрованный код номера микросхемы, к которой производится обращение. Так как в описываемом варианте состояние регистра 1 адреса не соответствует состоянию счетчика 3, то перехода к второму этапу (как это имеет место во втором варианте) не происходит. По окончании обращения устройство устанавливается в исходное (нулевое) состояние путем установки в нулевое состояние триггеров 40, 41, 42 и 15. С первыми тремя это происходит так же, как и во втором варианте, а триггер 15 устанавливается в нулевое состояние импульсом, формируемым по ВИ4 цепочкой - элементы И 32, ИЛИ 21.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ В ДИНАМИЧЕСКОЙ ПАМЯТИ, содержащее первый и второй регистры адреса, первый коммутатор, счетчик адреса, блок сравнения, триггер, блок управления, первый вход которого соединен с первыми входами регистров адреса и счетчика адреса, входы с первого по девятый блока управления, второй вход второго регистра адреса и первый вход первого коммутатора являются входами устройства, второй вход первого коммутатора соединен с выходом счетчика адреса и первым входом блока сравнения, второй вход которого подключен к выходу первого регистра адреса, третий и четвертый входы первого коммутатора соединены соответственно с первым и вторым выходами блока управления, выход первого коммутатора подключен к второму входу первого регистра .адреса, третий выход блока управления соединен с третьими входами первого и второго регистров адреса, второй вход счетчика адреса подключен к четвертому выходу блока управления, пятый выход которого соединен с первым входом триггера. Выход которого подключен к десятому входу блока . управления, первый и шестой выходы которого и выходы первого и второго регистров адреса являются выходами устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены третий регистр адреса, дешифратор, второй коммутатор, элемент И, выход которого соединен с вторым S входом триггера и одиннадцатым входом блока управления, входы элемента И подключены соответственно к выходу блока сравнения, седьмому выходу и третьему Bxofiy блока управления, первьш и третий входы третьего регистра адреса соединены соответственно с первым входом-и третьим выхо ;о оо ю дом блока управления, выход третьего регистра адреса подключен к входу дешифратора, выходы которого соединены с первым и вторым входами второго коммутатора, другие входы которого со подключены к первому, восьмому, девятому и десятому выходам блока управления, второй вход третьего регистра адреса и выход второго коммутатора являются. соответственно дополнительными входом и выходом устройства.

wn «w; Л« {еиз exofff (et/t}

(BUS)

B ffff7 (8l/ff)

txoffe (t)U7 - r-T

SutsS MfHennieifSi,iiJr gvt fffymKeflatt . fu/af g/ffffMMnae/e.-.J SMoff mpufiepaiv

6tae9 layfuttfflffffBM IВыход умеяентаам Вшод 1/араггера О SHK saKftemaMi/n Выхв9 a/t №ffmaifttfa.

dxofl tdui) df093 (Ot/f) Otaftf (виз) 1Лв95 вl/) 6s9ffe (6asi Лмед7 fei/fl Кю99 (du BHi9 toy) Btaaffi tafottepeW HHOffnyitfiteflen tvtefff fr Hotepaa ttntiJ i fnmefa ts вмшд1 щиаыуол tf ee/Mf/ J t ttatef 9MHfmta «w. Btaag CfCftV StniSi ВмМЗ Ляп

| Вопросы радиоэлектроники, сер | |||

| ЭВТ, вьт | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Патент США № 3760379, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1985-11-23—Публикация

1983-10-14—Подача