Изобретение относится к вычислительной технике и может быть использовано для возведения чисел в квадрат с контролем функционирования во время простоя.

Цель изобретения - повышение достоверности функционирования.

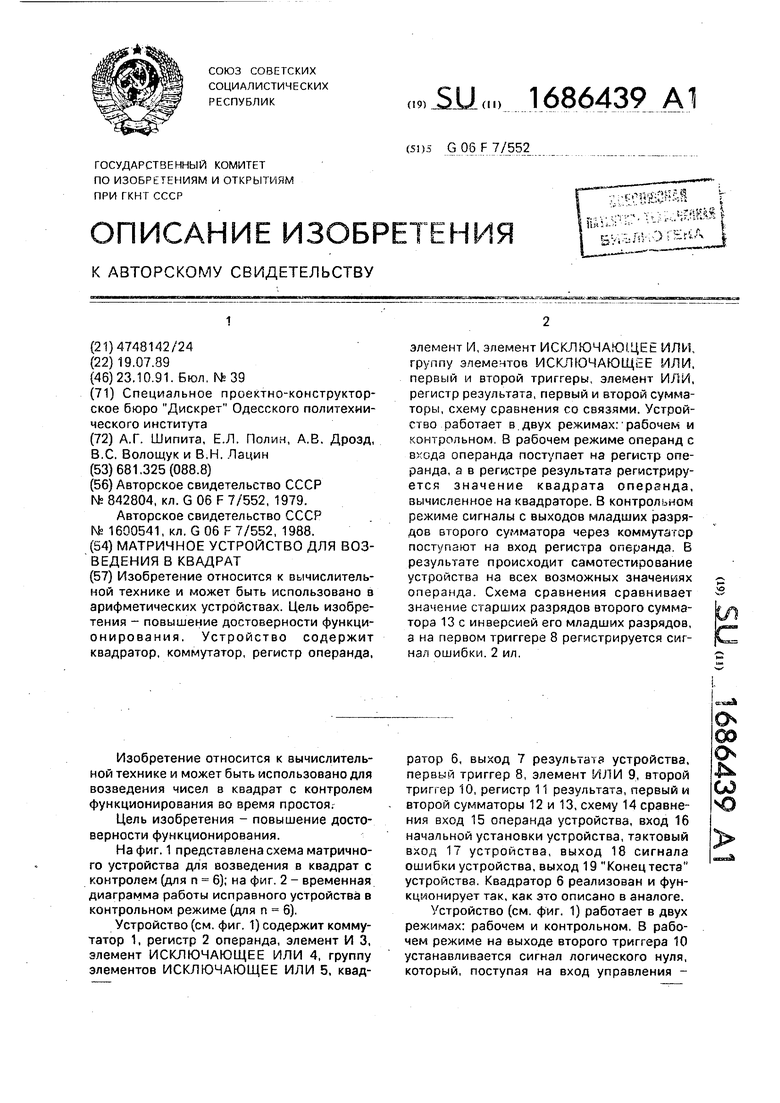

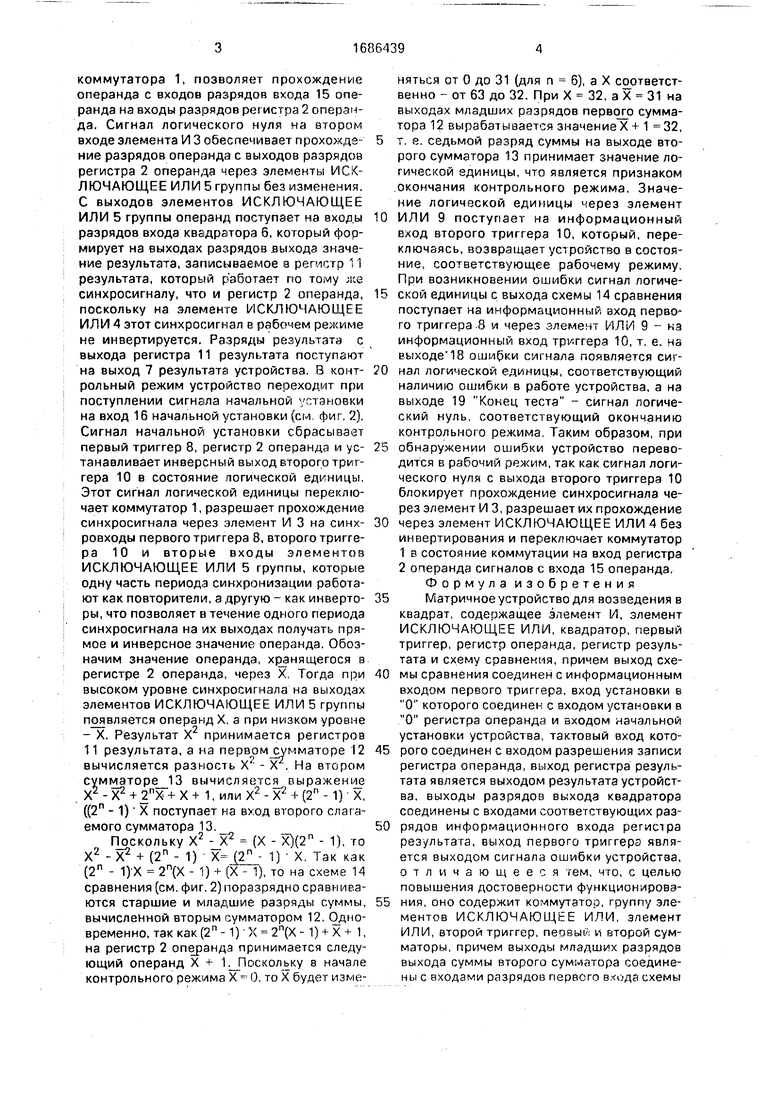

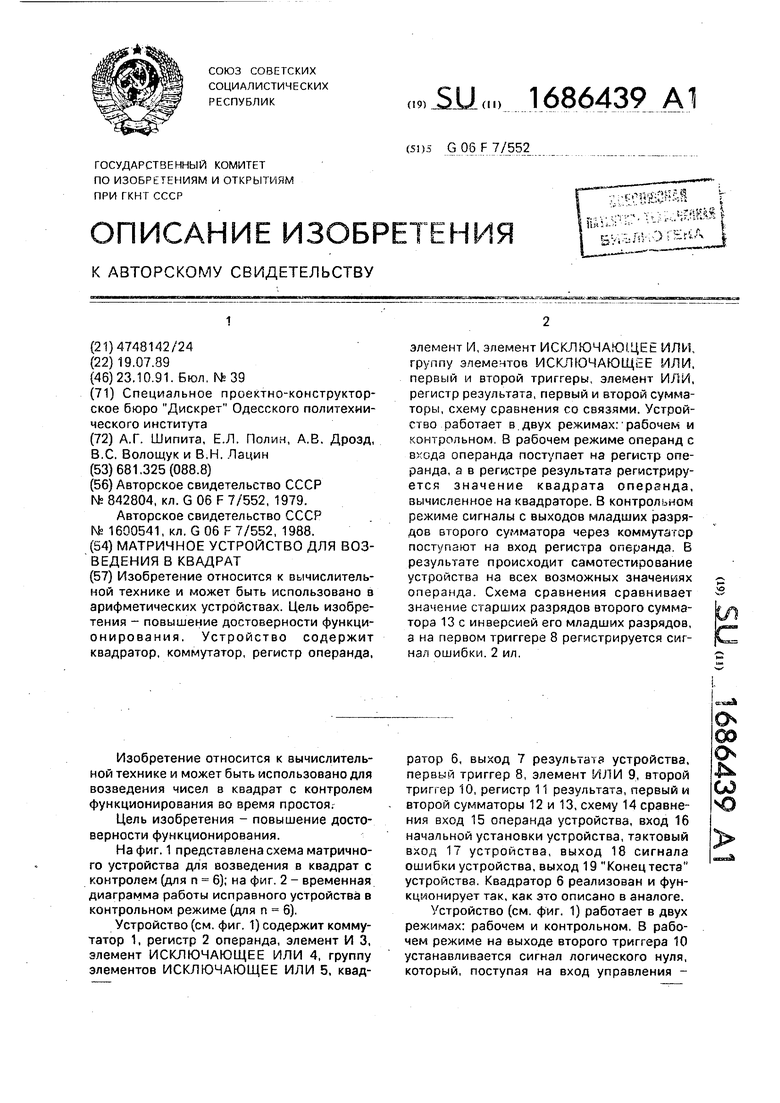

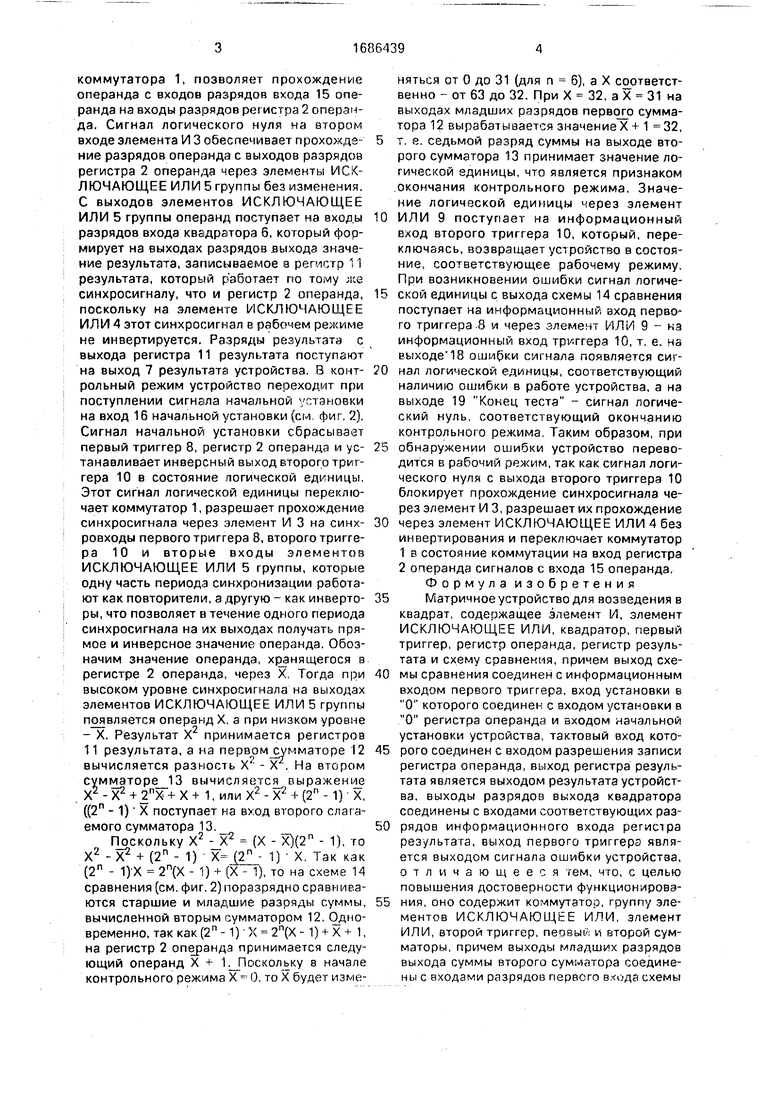

На фиг. 1 представлена схема матричного устройства для возведения в квадрат с контролем (для п 6); на фиг 2 - временная диаграмма работы исправного устройства в контрольном режиме (для п 6).

Устройство (см. фиг. 1) содержит коммутатор 1, регистр 2 операнда, элемент И 3 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5, квадратор 6, выход 7 резулыа. устройства, первый триггер 8 элемент лЛИ 9, второй трип ер 10, регистр 11 результата, первый и второй сумматоры 12 и 13, схему 14 сравнения вход 15 операнда устройства, вход 16 начальной установки устройства, тактовый вход 17 устройства, выход 18 сигнала ошибки устройства, выход 19 Конецтеста устройства. Квадратор 6 реализован и функционирует так. как это описано в аналоге. Устройство (см. фиг. 1) работает в двух режимах: рабочем и контрольном. В рабочем режиме на выходе второго триггера 10 устанавливается сигнал логического нуля, который, поступая на вход управления О 00

о

со о

коммутатора 1, позволяет прохождение операнда с входов разрядов входа 15 операнда на входы разрядов регистра 2 операнда, Сигнал логического нуля на втором входе элемента И 3 обеспечивает прохождение разрядов операнда с выходов разрядов регистра 2 операнда через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5 группы без изменения. С выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 группы операнд поступает на входы разрядов входа квадратора 6, который формирует на выходах разрядов выхода значение результата, записываемое в регистр 11 результата, который работает по тому же синхросигналу, что и регистр 2 операнда, поскольку на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 4 этот синхросигнал в рабочем режиме не инвертируется. Разряды результата с выхода регистра 11 результата поступают на выход 7 результата устройства. В контрольный режим устройство переходит при поступлении сигнала начальной у -тановки на вход 16 начальной установки (см фиг. 2). Сигнал начальной установки сбрасывает первый триггер 8, регистр 2 операнда и устанавливает инверсный выход второго триггера 10 в состояние логической единицы, Этот сигнал логической единицы переключает коммутатор 1, разрешает прохождение синхросигнала через элемент И 3 на синх- ровходы первого триггера 8, второго триггера 10 и вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 группы, которые одну часть периода синхронизации работают как повторители, а другую - как инверторы, что позволяет в течение одного периода синхросигнала на их выходах получать прямое и инверсное значение операнда. Обозначим значение операнда, хранящегося в регистре 2 операнда, через X. Тогда при высоком уровне синхросигнала на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 группы появляется операнд X, а при низком уровне - X. Результат X2 принимается регистров 11 результата, а на первом сумматоре 12 вычисляется разность X - X . На втором сумматоре 13 вычисляется выражение X -)2 + 2пХ + Х+ 1, или X2 -Х2 + (2П- 1) X, ((2П - 1) X поступает на вход второго слагаемого сумматора 13.

Поскольку X2 -J02 (X - Х)(2П - 1), то X2 - X2 + {2П - 1) Х- (2П - 1) X. Так как (2П - 1)Х 2П(Х - 1) + (X - 1), то на схеме 14 сравнения (см. фиг. 2) поразрядно сравниваются старшие и младшие разряды суммы, вычисленной вторым сумматором 12. Одновременно, так как (2П - 1) X - 2П(Х - 1) + X + 1, на регистр 2 операнда принимается следующий операнд X + 1.Поскол ку в начале контрольного режима X - 0. то X будет изменяться от 0 до 31 (для п - 6), а X соответственно - от 63 до 32. При X 32, а X 31 на выходах младших разрядов первого сумматора 12 вырабатывается значениеX + 1 32,

т. е. седьмой разряд суммы на выходе второго сумматора 13 принимает значение логической единицы, что является признаком окончания контрольного режима, Значение логической единицы «ерез элемент

0 ИЛИ 9 поступает на информационный вход второго триггера 10, который, переключаясь, возвращает устройство в состояние, соответствующее рабочему режиму. При возникновении ошибки сигнал логиче5 ской единицы с выхода схемы 14 сравнения поступает на информационный вход первого триггера 8 и через элемент ИЛИ 9 - на информационный вход триггера 10, т. е. на выходе 18 ошибки сигнала появляется сиг0 нал логической единицы, соответствующий наличию ошибки в работе устройства, а на выходе 19 Конец теста - сигнал логический нуль, соответствующий окончанию контрольною режима. Таким образом, при

5 обнаружении ошибки устройство переводится в рабочий режим, так как сигнал логического нуля с выхода второго триггера 10 блокирует прохождение синхросигнала через элемент И 3, разрешает их прохождение

0 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 без инвертирования и переключает коммутатор

1в состояние коммутации на вход регистра

2операнда сигналов с входа 15 операнда.

Формула изобретения

5Матричное устройство для возведения в

квадрат, содержащее элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, квадратор, первый триггер, регистр операнда, регистр результата и схему сравнения, причем выход схе0 мы сравнения соединен с информационным входом первого триггера, вход установки в О которого соединен с входом установки в О регистра операнда и входом начальной установки устройства, тактовый вход кото5 рого соединен с входом разрешения записи регистра операнда, выход регистра результата является выходом результата устройства, выходы разрядов выхода квадратора соединены с входами соответствующих раз0 рядов информационного входа регистра результата, выход первого триггера является выходом сигнала ошибки устройства, отличающееся тем, что, с целью повышения достоверности функционировэ5 ния, оно содержит коммутатор, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, второй триггер, пеовьж и второй сумматоры, причем выходы младших разрядов выхода суммы второго сумматора соединены с входами разрядов первого схемы

сравнения и входами разрядов первого информационного входа коммутатора, второй информационный вход которого соединен с входом операнда устройства, аыход коммутатора соединен с информационным входом регистра операнда, выходы рээрч/Кв которого соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы которых соединены с входами соответствующих разрядов входа квадратора, выход регистра результата соединен входом первого слагаемого первого CVMMS- тсра, выхол суммы которого соединен с входом первого слагаемого второго сумматора, выходы старших разрядов выхода ;уммы ко- орого соединены с входами разрядов второго входа с.семы сравнения выходы разрядов выхода кьэдрэторя соедии мы с инверсными входами соответствующих разрядов входа второго слагаемого первого суммятора, пход переноса которою соединен с входом переноса второго сумма ора и входом уровня логической единицы устрой ства, вход начальной установки которого соединен с установки в О второго триггера, информационный вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соот- ветстпенно с выходом (п + 1)-го (п - разрядность операнда) разряда выхода суммы второго сумматора и выходом схемы сравнения, тактовый вход устройства соединен с первыми входами элемента И и элемента

0 ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с управляющим входом коммутатора, инверсным выходом второго трип ерл и выходом Конб Д тест-з устройст ва, выход элемента ; соединен с вторыми

Ь входами элег нтов ИСКЛЮЧАЮЩЕЕ ИПИ группы, рходаг/и ра пешенчя записи перао- го и второгг, тоиггер, в выход элемента АС- КЛЮЧАЮЦГЕ И ПИ соединен с ьходом разрешения зяпис регисгоа результата,

0 выход К-го (К 1 - п) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединен с прямым входом К-го разряда и инверсным входом (п + К)-го разряда входа второго слагаемого вторе го сумматора

ft, 77 8х.16

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления многочленов | 1988 |

|

SU1617445A1 |

| Устройство для вычисления полиномов | 1989 |

|

SU1674112A1 |

| Процессорный модуль | 1989 |

|

SU1674111A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

Изобретение относится к вычисли гепо- ной технике и может быть использовано а арифметических устройствах. Цель изобретения - повышение достоверности функционирования. Устройство содержат квадратор, коммутатор, регистр операнда, элемент И, элемент ИСК пюЧАЮЩЫг. ИЛИ группу эпементоч ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй триггеры элемент ИЛИ. регистр результата, первый и второй сумма торы, схему сравнения го связями. Устройство работает в двух режимах рабочем и онтрольном В рабочем режиме операнд с D уда операнда поступает на регистр операнда, а в регистре результата регистрируется значение квадрата операнда, вычисленное на квадраторе В контрольном режиме сигналы с выходов младших разрядов второго сумматора через коммутатор поступают на вход регистра операнда В результате происходит самотестирование устройства на всех возможных значениях операнда Схема сравнения сравнивает значение старших разрядов второго сумматора 13 с инверсией его младших разрядов з на первом триггере 8 регистрируется сигнал ошибки 2 ил. 1Л

Вш.б/1.2 %% 0 X 7 X 2 30 X g OF

бш.бл.З

fib/x. ff/i. %%% Йь/х.б/1 5

8wx.ft.eШ1

П

OXgnmrg/iT 29 ХЗЗХЖХ 32 X 31 X32

Вых.бл.10 ЛШ

0fcM.ft.77 ШПШЗХ J6VV XJ727- X 7/53 X Щ9 /Щ

ль/х.а.й .725XJ« wj3ew7. .«7х.

ймх.а. 7J ШШХвИлШ

.7Л.

Ф«/гг

П

I УЖ

| Матричное устройство для возведенияВ КВАдРАТ | 1979 |

|

SU842804A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство Ne 1600541,кл.G 06 г 7/552, 1988 | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-10-23—Публикация

1989-07-19—Подача