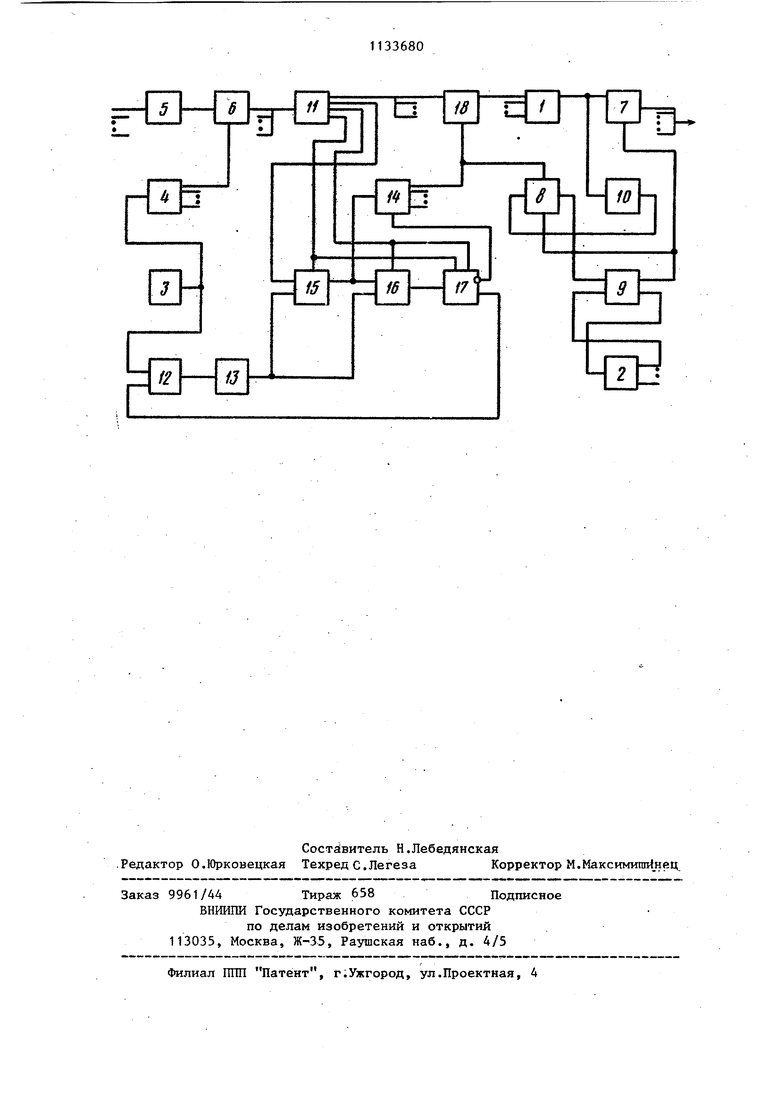

Изобретение относится к технике связи и может быть использовано в узлах коммутации телеграфных каналов повьшенной пропускной способнос.ти. Известно адресно-коммутационное устройство, содержащее входные регистры, входы которых соединены с соответствующими входящими адресно информационными магистралями, выходные регистры, выходы которых соединены с соответствующими исходящими адресно-информационными магистралями распределитель тактов, выходы которого подключены к управляющим входам соответствующих входных регистров, дешифратор и блоки памяти, при этом вьпсоды всех входных регистров объединены и подключены к .входу дешифратора и входам блоков памяти, выходы которых соединены с входами соответствующих выходных регистров,-причем выходы дешифратора соединены с управ ляющими входами соответствующих блоков памяти Л . Недостатком устройства является низкая пропускная способность, связанная с необходимостью передачи по каналу связи, кроме данных информации, адресов входной и выходной маги стралей . Наиболее, близким к изобретению является адресно-коммутационное устройство, содержащее накопитель, выходной распределитель и последовательно соединенные блок сигналов iопорной частоты и входной распредели тель, а в каждом коммутируемом канале - последовательно соединенные входной регистр и входной ключ, выходной ключ, счетчик состояний, решающий блок и генератор одиночног импульса, при этом управляющий вход входного ключа соединен с соответст вующим выходом входного распределителя, выход накопителя соединен с сигнальным входом выходного ключа соответствующего коммутируемого кана ла и входом генератора одиночного импульса, выход которого соединен с информационным входом счетчика сос тояний, к выходу которого подключен первый вход решающего блока, второй вход которого соединен с соответствующим выходом выходного распределителя, к входу которого подключен пер вый выход решающего блока, второй выход которого соединен с управляющи ми входами счетчика состоянии и выходного ключа 2j . Недостаток известного устройства - низкая пропускная способность, связанная с невозможностью передачи по .одной адресно-информационной магистрали информации от нескольких источников. Цель изобретения - повьш1ение пропускной способности. Для достижения цели в адресно-коммутационное устройство, содержащее накопитель, выходной распределитель и последовательно соединенные блок сигналов опорной частоты и входной распределитель, а в каждом коммутируемом канале - последовательно соединенные входной регистр и входной ключ, выходной ключ, счетчик состояний, решающий блок и генератор одиночного импульса, при этом управляющий вход входного ключа соединен с соответствующим выходом входногораспределителя, выход накопителя соединен с сигнальным входом выходного ключа соответствующего коммутируемого канала и входом генерато а одиночного импульса, выход которого соединен с информационным входом счетчика состояний, к выходу которого подключен первый вход решающего блока, второй вход которого соединен с соответствующим выходом выходного рас- . пределителя, к входу которого подключен первый выход решающего блока, второй выход которого соединен с управляющими входами счетчика состояний и выходного ключа, введены общие для всех коммутируемых каналов первый и второй блоки памяти, буферный регистр, мультиплексор, счетчик адресов, дешифратор и элемент И, а в каждый коммутируемый канал - ключ памяти, причем выход входного ключа соединен с входом буферного регистра, информационный выход которого соединен с информационным входом ключа памяти, управляющий вход которого соединен с входом прямого счета счетчика состояний и с соответствующим выходом дешифратора, адресный вход первого блока памяти соединен с первым, вькодом буферного регистра, второй выход которого соединен с управляющим входом мультиплексора и первым управляющим записью входом второго блока памяти, третий выход буферного регистра соединен с управ311ляющим записью входом первого блока памяти и вторым управляющим записью входом второго блока памяти, инверсный выхо которого соединен с управляющим входом дешифратора, выход клю ча памяти соединен с информационным входом накопителя, прямой выход второго блока памяти соединен с первым входом элемента И, выход которого соединен с входом счетчика адресов, выход которого соединен с информационным входом первого блока памяти и первым входом мультиплексора, второй вход которого соединен с выходом пер вого блока памяти, и входом дешифратора, выход мультиплексора соединен с информационным входом второго блока памяти, второй вход элемента И соединен с выходом блока сигналов опорной частоты. На чертеже представлена структурная электрическая схема предлагаемого адресно-коммутационного устройства. Устройство содержит накопитель 1 выходной распределитель 2, блок 3 сигналов опорной частоты, входной распределитель 4, входной регистр 5 входной ключ 6, выходной ключ 7, счетчик 8 состояний, решающий блок 9 генератор 10 одиночного импульса, буферный регистр 11, элемент И t2, счетчик 13 адресов, дешифратор 14, первый блок 15 памяти, мультиплексор 16, второй блок 17 памяти и ключ 18 памяти. Устройство работает следующим образом. Информация от М источников по N адресно-информационным магистралям () поступает на входные регистры 5 . Входной распределитель 4 по сигналам блока 3 подключает входные регистры 5 через входные ключи 6 к буферному регистру 11. При подключении i-ro входного регистра 5 (где ) на вькоде буферного регистра 11 появляется информационное слово, состоящее из адресной части, в которой закодирован К-й номер источника информации (где ), собственно информационной части и служебной информации, содержащей признаки начала работы источника Начало информации и ее конца Конец информации (наличие или отсутст вие логической единицы на соответствующих разрядах адресно-информационного слова). При этом адресная часть поступает на адресные входы первого блока 15 памяти, информационная часть - на вход ключей 18, признак Начало информации, - на управляющий записью вход первого блока 15 памяти и управляющий записью единицы вход второго блока 17 памяти, признак Конец информации - на управляющий вход мультиплексора 16 и . управляющийзаписью нуля вход второго блока 17 памяти. Перед началом работы накопитель 1, первый блок 15 памяти и второй блок 17 памяти обнуляются, а на счетчике 13 выставляется начальный код, равный единице, поэтому на прямом выходе второго блока 17 памяти присутствует логический ноль, запрещающий прохождение сигналов опорной частоты через элемент И 12 на счетчик 13, число на выходе которого является адресом первой свободной зоньпамяти накопителя 1 и поступает на входную информационную шину первого блока 15 памяти. При появлении на выходе буферного регистра 11 признака Начало информации в первый блок 15 памяти по адресу, являющемуся номером начавшего работать источника информации, записывается показание счетчика 13, а затем оно из первого блока 15 памяти поступает на дешифратор 14, на управляющем входе которого находится логическая единица с инверсного выхода второго блока 17 памяти, разрешающая дешифрацию. Сигнал с выхода дешифратора 14 поступает на соответствующий ключ 18 и открывает его для прохождения информационной части с буферного регистра 11 в свободную зону памяти буферного регистра 11. Кроме того, признак Начало информации производит запись во второй блок 17 памяти логической единицы, означающей, что зона с данным адресом в накопителе 1 занята под прием информации. Появившаяся в результате этого на выходе второго блока 17 памяти логическая единица поступает на элемент И 12, разрешая прохождение сигналов опорной частоты на счетчик 13, который производит перебор адресов на входе второго блока 17 памяти через мультиплексор 16, до появления на прямом выходе второго блока 17 памяти логического нуля, закрывающего t элемент И 12. Наличие логического нуля в j-й ячейке памяти второго блока 17 памяти, где , означает, что j-я зона памяти в накопителе 1 свободна для приема информации от нового источника, В случае начала работы такого источника на выходе буферного регистра 11 .появляется признак Начало информации и описан-Ю доз

ный процесс повторяется. Таким образом, по мере появления новых работающих каналов в первом блоке 15 памяти происходит запись по адресам, являющимся номерами работающих источников адресов зон памяти накопителя 1, в которых происходит накопление, информации с прикрепленного источника.

В процессе работы появление информационного слова без служебных признаков от какого-либо источника вызывает считывание из первого блока 15 памяти адреса зоны памяти накопителя 1 , в которой происходит накопление информации.от данного источника, дешифрацию этого адреса и включение соответствующего ключа 18.

В случае окончания работы источни ка информации на выходе буферного регистра 11 появляется признак Конец информации, который поступает на управляющий вход мультиплексора 16 и подключает выход первого блока 15 памяти к адресному входу второго блока 17 памяти. Кроме того, признак Конец информации поступает на управляющий записью нуля вход второго блока памяти. Таким образом, по адресу, являющемуся адресом зоны памяти накопителя 1, в которую поступала информация с данного источника, во второй блок 17 памяти записывается логический ноль, означающий осво1133

в состояние прямого счета и изменяет его состояние. Этот же сигнал открывает ключ 18, и информация переписывается в зону памяти накопителя 1, закрепленную в настоящее время за данным источником информации.

К выходам зон памяти накопителя 1 подключены генераторы 10 одиночного импульса, формирующие сигнал при передаче одного блока данных из соответствующей зоны накопителя 1. Эти сигналы поступают на соответствующие счетчики 8.

При наличии сигнала от генераТора 10 одиночного импульса и решающего блока 9 одного информационного канала счетчик 8, закрепленный за этим информационнь1м каналом, работаг ет в режиме обратного счета. При установлении одного из счетчиков 8 в нулевое состояние на его выходе формируется нуль, меняющий сигнал на выходе соответствующего выходного ключа 7 и переводящий выходной распределитель 2 в следующее состояние, определяющее вывод информации из следующей зоны накопителя 1.

Предлагаемое устройство позволяет передавать по одним и тем же входным адресно-информационным магистралям информацию от нескольких источников, что приводит к существенному увеличению пропускной способности. 6 бождение данной зоны памяти накопителя 1 для приема информации от другого источника. Занятие освободившей ся зоны осуществляется после выставления адреса данной зоны на счетчике 13 и появления на выходе буферного регистра 11 служебного признака Начало информации. Наличие единицы на одном из выходепшфратора 14 ставит счетчик 8

-I - //

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресно-коммутационное устройство | 1987 |

|

SU1515378A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

АДРЕСНО-КОММУТАЦИОННОЕ УСТРОЙСТВО, содержащее накопитель, выходной распределитель и последовательно соединенные блок сигналов опорной частоты и входной распределитель, а в каждом коммутируемом канале - последовательно соединенные входной регистр и входной ключ, выходной ключ, счетчик состояний, блок и генератор одиночного импудьса, при этом управляющий вход входного ключа соединен с соответствующим выходом.входного распределителя, вькод накопителя соединен с сигнальным входом вькодного ключа соответствующего коммутируемого канала и входом генератора одиночного импульса, выход которого соединен с информационным входом счетчика состояний, к выходу которого подключен первьй вход рещающего блока, второй вход которого соединен с соответствз щим выходом выходного распределителя, к входу которого подключен первый выход решающего блока, второй выход которого соединен с управляющими входами счетчика состояний и выходного ключа, отличающеес я тем, что, с целью повышения пропускной способности, в него введены общие для нсех коммутируемых каналов первый и второй блоки памяти, буферный регистр, мультиплексор, счетчик адресов, дещифратор и элемент И, а в каждьш коммутируемый канал -ключ.памяти, причем выход входного ключа соединен с входом буферного регистра, информационный выход которого соединен с информационным входом ключа памяти, управляющий вход которого соединен с входом прямого счета счетчика состояний и с соответствзтощим выходом дешифратора, адресный вход первого блока памяти соединен с первым выходом буферного регистра, второй выход кото1эого сое§ динен с управляющим входом мультиплексора и первым управляющим за(Л писью входом второго блока памяти, третий выход буферного регистра соединен с управляющим записью входом первого блока памяти и вторым управляющим записью входом второго блока памяти, инверсный вькод которого соединен с управляющим входом 00 С«9 дешифратора, выход ключа памяти соединен с информационным входом накопиat) теля, прямой выход второго блока па00 мяти соединен с первым входом элемента И, выход которого соединен с входом счетчика адресов, которого соединен с информационным входом первого блока памяти и первым входом мультипле.ксора, второй вход которого соединен с выходом первого блока памяти и входом дешифратора, выход мультиплексора соединен с информационным входом второго блока памяти, второй вход элемента И соединен с выходом блока сигналов опорной частоты.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для асинхронной пространственной коммутации | 1974 |

|

SU493037A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Контактное устройство для панелей газоразрядных индикаторов | 1976 |

|

SU641688A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-01-07—Публикация

1983-05-06—Подача