Изобретение относится к вычислительной -технике, в частности, к устройствам контроля ЭВМ, и может быть использовано при построении устройств программного и микропрограммного управления с высокой достоверностью функционирования,Цель изобретения - расширение функциональных возможностей устройства за счет контроля значений логических условий при реализации ветвей микропрограмм.

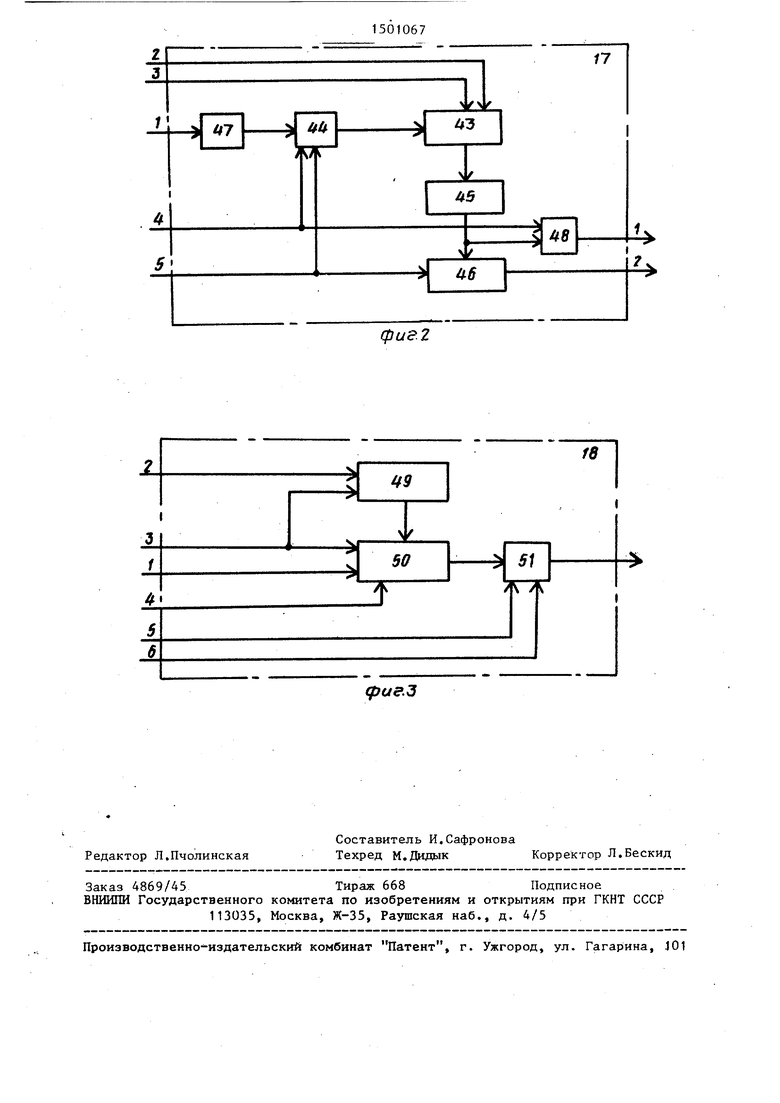

На фиг с 1 пpkвeдeнa функциональная схема устройства; на фиг, 2 - схема блока управления эталонами логических условий; на фиг, 3 - схема блока формирования эталонов логических ус- ловий.

Устройство содержит блок 1 памя- ти, мультиплексор 2, сумматор 3 по модулю два, регистр 4 результата, первый элемент ИЛИ 5, элемент 6 задержки, регистр 7 данных, блок 8 анализа логических условий, блок 9 мо- дификации кода контроля, счетчик 10, блок 11 элементов И, второй элемент ИЛИ 12, блок 13 элементов ИЛИ-НЕ первый 14, второй 15 и третий 16 элементы И, блок 17 управления эталонами логических условий, блок 18 формирования эталонов логических условий, третий элемент ИЛИ 19, четвертьй элемент И 20, схему 21 сравнения, вход 22 обращения устройства, вход 23 начальной установки устройства, первый тактовый вход 24 устройства, вход 25 адреса микрокоманды устройства, вход 26 логического условия

0

5

0 5 Q г

устройства, вход 27 записи и вход 28 считывания логического устройства, вход 29 управления режимом устройства, вход 30 кода операции устройства, вход 31 кода контроля устройства, вход 32 разрешения контроля условных переходов устройства, вход 33 разрешения модификации кода контроля устройства, второй тактовый вход 34 устройства, выход 35 признака ошибки и выход 36 кода ошибки устройства, вход 37 задания числа эталонов и вход 38 записи числа эталонов устройства, вход 39 задания контроля логических условий устройства, вход 40 записи эталонов и вход 41 задания кода эталонов устройства и выход 42 признака конца контроля логических условий устройства.

Блок управления эталонами логических условий образуют счетчик 43, первый элемент И 44, элемент ИЛИ 45, второй элемент И 46, элемент 4 7 задержки и элемент И-НЕ 48,

Блок формирования эталонов логических условий содержит элемент ИЛИ 49, регистр 50 сдвига и элемент И 51.

Устройство работает в двух основных режимах: контроль следования микрокоманд микропрограммы с неизвестными (до вьшолнения микрокоманд) значениями логических условий (режим 1.) и с известными значениями этих условий, что соответствует контролю следования микрокоманд ветви микропрограммы с контролем значений логических условий (режим 2),

в первом режиме устройство работает следующим образом.

Перед поступлением на входы устройства первой микрокоманды контролируемой микропрограммы на соответствующую линию входа 23 устройства подается сигнал установки в О регистра 4 результата, что исключает появление единичного сигнала на выходе 35 признака ошибки устройства до начала контроля. На вход 39 устройства подается нулевой код, поступающий на второй вход третьего элемента 20 И и через четвертый и шестой входы соответственно блоков 17 и 18 на элемент И-НЕ 48 и элемент И 51. На выходе элемента И-НЕ 48, являющегося выходом 42 признака конца контроля логических условий устройства, вырабатывается нулевой сигнал, позволяющий в режиме 1 продолжать процесс контроля микропрограммы. С выходов элементов И 20 и 51 (через выход блока 18) нулевые коды поступают на входы схемы 21 сравнения. В связи с равенством кодов на входах схемы 21 сравнения указанньм блок формирует нулевой сигнал, поступающий на вход соответствующего разряда контроля значений логических условий регистра 4 результата. В связи с тем, что нулевой код на входе 39 устройства устанавливается на все время работы устройства в режиме 1j в процесс контроля следования микрокоманд в указанный разряд всегда записывается О. Таким образом, на выходе 35 устройства исключается появление сигнала ошибки по результату контроля значений логических условий. При этом значения сигналов на входах 37, 38, 40 и 41 устройства обеспечивающих контроль значений логических условий, могут быть произвольными.

Из микропрограммного устройства управления (МУУ) считывается первая (очередная) микрокоманда, контрольная часть которой совместно с выработанным МУУ адресом следующей микрокоманды поступает на входы устройства.

Код. адреса следукщей микрокоманды поступает на вход адреса микрокоманды устройства, а код контроля контрольной части микрокоманды - на вход 31 устройства. Кроме того, в контрольной части микрокоманды могут со0

10676

держаться все поля, коды которых управляют отдельными блоками предлагаемого устройства, т.е. соответствукщие

g входам 27, 28, 29, 31, 32 и 33 устройства, или их часть. В последнем случае поля, соответствующие указанным входам, не включаются в контрольную часть микрокоманд, так как являQ ются операционными и используются совместно НУУ для вьфаботки следующего адреса и предлагаемым устройством. Поляшг, которые могут стать операционными, являются поля, соответст5 вующие входам 27, 28 и 29.

С входа 31 устройства код контроля поступает на первьй вход блока 9 модификации кода контроля. Если считанная микрокоманда - не микрокоманда ветвления (безусловного перехода), то на входах 28, 29, 32 и 33 устанавливаются н левые коды, блокирующие поступление информации через первьп 14, второй 15 и третий 16 элементы И и блок 11 элементов И из блока 8 анализа логических условий и счетчика 10.

8результате на второй и третий входы блока 9 и на первьй и второй входы элемента ИЛИ 12 поступают О. Так как нулевые коды модификации на входах блока 9 не изменяют разрядов кода контроля, поступаюпщх на вторые входы указанных блоков, на выходе блока

9модификации кода контроля устанавливается тот же код, что и на первом

5 входе блока 9. По нулевому сигналу с выхода второго элемента ИЛИ 12, поступающему на управляющий вход мультиплексора 2, код контроля через второй вход мультиплексора передается на его выход, далее на первый вход сумматора 3 по модулю два, на второй вход которого с входа 25 устройства поступает адрес следукщей микрокоманды. По синхросигналу, поданному с входа 23 устройства, производится запись результата выполнения в блок 3 поразрядной операции ИСКПЮ- ЧАЩЕЕ- ИЛИ в регистр 4 результата.

5

0

0

Наличие 1 хотя бы в одном разряде регистра результата 4 свидетельствуют об ошибке и приводит к вьфа- ботке на выходе первого элемента ИЛИ 5 и выходе 35 признака ошибки устройства сигнала 1. Указанный сигнал может быть использован для блокировки выработки синхронизиругсщих импульсов в МУУ или для прерывания микропрограммы с последующей передачей

управления микропрограмме диагностики ошибок, использугацей в качестве исходной диагностической информации код на втором выходе 36 устройства.

При отсутствии ошибки формируются нулевые коды на выходе регистра 4 результата и на выходах 35 и 36 устройства.

Если на входы устройства (из МУУ) считывается микрокоманда перехода (ветвления) по модифицируемым логическими условиями адресам, то на вход 28 считывания логического условия поступает код, содержащий в одном из разрядов 1, остальных - О На входы 31 и 25 устройства поступают код контроля, соответствующий данной микрокоманде, и адрес следующей микрокоманды, а на входы 29, 32 устройства и разряды управления блоком 11 элементов И входа 33 устройства, как ив случае контроля микрокоманд безусловного перехода, - О. Код с входа 28 устройства поступает на третий вход блока 8 анализа логических условий. Указанное логическое условие может быть сформировано на выходе блока 8 либо непосредственно .под управлением данной микрокоманды Iперехода, либо в одной из предьщущих микрокоманд. Для МУУ, в которых следующий адрес вырабатывается пос ле счифывания очередной микрокоманды из микропрограммной памяти используются оба способа формирования логи- ческого условия.

При контроле условных переходов по произвольным микропрограммным адресам удравление выполнением опера- ций приема, запоминания, хранения, считывания логических условий, осуществляемых блоком 8 анализа логических условий, производится с входов 27, 28 и 34 устройства так же, как и при контроле переходов по модифицируемым логическими условиями адресам. При этом на входе 33 разрешения модификации кода контроля устанавливается нулевой код, запрещающий модификацйю кода контроля, установ- ленного на входе 31 устройства в блоке 9 с выходов блока 1 1 элементов И и третьего элемента И 16, На входе 32 разрешения контроля условных пере

ходов устройства устанавливается код 1, открывающий по второму входу второй элемент И 15 и обеспечивающий передачу считываемого под управле

j -

5

нием входа 28 устройства бита логического условия с выхода блока 8 через второй элемент И 15 и на второй вход второго элемента ИЛИ 12, Так как на первом входе второго элемента ИЛИ 12 - о, вследствие маскирования выхода первого элемента И 14 по его второму входу с входа 29 управления режимами устройства, управление мультиплексором 2 осуществляется битом указанного логического условия. При нулевом бите условия на выход мультиплексора 2 передается код контроля, соответствующий одному из адресов перехода и транслируемым без изменений через блок 9 модификации кода контроля с входа 31 устройства, В противном случае, если бит условия равен 1, на выход мультиплексора 2 передается код с его первого входа. Формирование указанного кода зависит от организации соответствующего МУУ, В частности при совмещении в МУУ операций считывания очередной микрокоманды и выработки адреса следующей микрокоманды формирование кода должно производиться в микрокоманде, предшествующей микрокоманде формирования управляющего мультиплексора 2 бита условия. Именно по разрешающему сигналу на входе 22 устройства по адресу на входе 25 адреса микрокоманды устройства, равного ад- р-есу следующей микрокоманды, производится считывание из блока памяти 1. Код, считанный из блока 1 памяти, равный второму из контролируемых адресов перехода, к началу следующего цикла записывается в регистр 7 данных по сигналу, подаваемому с входа 24 устройства на его первый вход.

Таким образом в следующей микрокоманде на выход мультиплексора 2 подается контрольный код с его первого или второго входа, Вьфаботка сигнала на выходе 35 признака ошибки устройства с использованием блоков 3-5 устройства производится описанным ранее образом. При контроле следующих друг за другом микрокоманд условных переходов по произвольным адресам совмещается контроль текущих переходов и выборка из блока 1 памяти контрольных кодов, используемых в следующих циклах.

Для контроля переходов по многоразрядным кодам, например, по коду операции, адресу микропрограммы обра

9

ботки прерываний и т.п. указанньй к с входа 30 кода операций устройства через информационный вход счетчика 10 предварительно записьшается в эт блок. Запись производится при нулевом коде на входе 29 управления режмом устройства по синхроимпульсу с входа 34 устройства, поступагадему соответственно на вход управления счетом и счетный вход счетчика 10.

При выполнении микрокоманды собсвенно контроля перехода данного тип (возможно совмещение записи и контроля в одной микрокоманде) на входе 32 разрешения контроля условных перходов устройства, на входе 29 управления режимом и в разряде управлени элементом И 16 входа 33 разрешения модификации кода контроля устройств устанавливаются нулевые коды. По едничному коду с входа 33 разрешения модификации кода контроля устройств через открытые по второму входу элементы И блока 11 на третий вход блока 9 модификации кода контроля подаются разряды кода из счетчика 10. С входа 31 устройства на первый вход блока 9 подается код контроля, содержащий нули в разрядах, соответствующих считываемым разрядам из счетчика 10. Так как с выхода третьего элемета И 16 на второй вход блока 9 передается О, на выходе указанного блока в соответствии с его функционированием вырабатывается код контроля, который по сформированному на элементе ИЖ 12 нулевому сигналу управления мультиплексором 2 передается на первый вход сумматора по модулю два 3. Дальнейшие действия по вьфа- ботке сигналов на выходах 35 и 36 устройства аналогичны описанным.

Контроль правильности повторений одной микрокоманды или группы последовательных микрокоманд заданное число раз осуществляется следующим образом.

В предшествующей микрокоманде по нулевому коду на входе 29 управления режимами устройства по синхроимпульсу с второго тактового входа 34 устройства производится загрузка числа повторений с входа 30 устройства в счетчик 10. В последней микрокоманде группы по входу 29 управлени режимом устройства, установленному в режим счета (код 1) по синхроимпульсу с входа 34 устройства, из содер

10

15

0

1067

10

жимого счетчика 10 вычитается единица. Полученный код из счетчика 10 через блок элементов ИЛИ-НЕ 13, преобразованный последним в битовый код, поступает далее на открытый по второму входу сигналом с входа 29 устройства первый элемент И 14, а затем на второй элемент НЛИ 12, на второй вход которого подается О из блокированного нулевым кодом с входа 32 устройства второго элемента И 15. Таким образом на управляющем входе мультиплексора 2 устанавливается указанный битовый код. При нулевом значении этого кода, означающегог что необходимо по крайней мере еще раз повторить контролируемую группу микрокоманд, т.е. содержимое счетчика 10 - не нулевое, на выход мультиплексора 2 подается код контроля, транслируемый через блок 9 при маскировании выходов второго 15 и третьего 16 элементов И и блока 11 элементов 25 И нулями с входов 32, 33 и 31 устройства. Если указанный битовый код равен 1, что означает вьтолнение группы микрокоманд заданное число раз, т.е. в счетчике содержится нуль, на выход мультиплексора 2 подается контрольный код из регистра данных 7, записанный в этот регистр после его считывания в предшествующей микрокоманде из блока 1 памяти (формирование информации в регистре 7 изложено при описании режима контроля условных переходов по произвольным адресам). Функционирование блоков 3, 4 и 5 по выработке результатов контроля на входах 35 и 36 устройства соответствует описанному. Контроль следования микрокоманд внутри повторяемой группы обеспечивается любым из описанных выше режимов, не изменяющих содержимое счетчика 10.

0

5

0

О

5

В устройстве возможно совмещение описанных режимов контроля. В частности, обеспечивается проверка в одной микрокоманде переходов по произвольным или модифицируемым адресам и одновременно по части кода счетчика, переходов по модифицируемым логическим условием адресам и одновременно по дополнительному гщ- ресу при равенстве нулю содержимого счетчика. Для первой и второй из указанных типов проверок используются блоки устройства и коды на его вхо10

n

дах, как это указано при описании режима контроля переходов по многоразрядным кодам. Кроме того, для oбecпeчeния подачи считываемого под управлением входа 28 устройства из блока 8 на управляющий вход мультиплексора 2 логического условия на вхо де 32 устройства устанавливается код 1, обеспечивающий прохождение сигнала условия через второй элемент И

15(первьй тип проверок). Для обеспечения передачи логического условия

из блока 8 через третий элемент И

16на второй вход блока 9 с входа 33 устройства подается код

рой тип проверок). В результате обеспечивается коммутация соответствующих цепей передачи логического условия и возможность совместного использо- 20 вания режимов контроля. Для третьего типа совместных проверок используются блоки и входы устройства, как это

1 (вто15010

5

Если загрузка счетчика 43 и регистра 50 сдвига осуществляется в одном 1щкле с контролем первой микрокоманды контролируемой ветви неко- 5 торой микропрограммы (допустимо загрузку осуществлять отдельным циклом) , то отдельные поля контрольной части микрокоманды поступают на соот ветствующие входы устройства вместе с адресом следующей микрокоманды из МУУ, как и при работе устройства в первом режиме. При этом значения на входах определяются типом считанной команды (безусловного перехода, ветв

было указано при описании режимов

контроля правильности повторений мик- 25 ления по произвольным или модифици- рокоманд заданное число раз и контро- руемым адресам, прехода по многораз- ля переходов по модифицируемым логи- рядным кодам) и подрежимом ее конт- ческими условиями, адресам.

роля (например, контроль числа повторений группы микрокоманд), а работа

При работе устройства во втором

роля (например, контроль числа повторений группы микрокоманд), а работа

режиме (с контролем значений логичес-30 блоков устройства по контролю следования адресов осуществляется соответственно первому режиму, причем параллельно с контролем значений логических условий.

ких условий) необходимо ввести в блок 17 управлениями эталонами логических условий и в блок 18 формирования эталонов логических условий соответственно код числа эталонных значений и коды самих эталонных значений. Указанные коды устанавливаются на вхо-г дах 37 и 41 устройства. На входах

38и 40 записи числа и записи эталонов устройства устанавливаются сигналы разрешения записи (соответственно равные О и 1), а на входе

39устройства - единичный сигнал разрешения контроля логических условий.

вания адресов осуществляется соотве ственно первому режиму, причем параллельно с контролем значений логи ческих условий.

35 Код с входа 28 считывания логического условия устройства поступает параллельно на третий вход блока 8 и вход третьего элемента ИЛИ 19, а бит логического условия - с выход

40 блока 8 на первые входы второго 15, третьего 16 элементов И и параллель но на третий вход четвертого элемен И 20. В зависимости от того, являет ли первая микрокоманда микропрограм

По синхросигналу, поступающему с вто-дЗ ветви микрокомандой ветвления

или нет, на входе элемента ИЛИ 19 устанавливается соответственно единичный или нулевой код, поступающий на первый вход четвертого элемента 20 И и через пятый вход блока 18 на третий вход элемента И 51. Так как на втором входе указанных элементов И устанавливается единичный сигнал, подаваемый с входа 39 устройства (д элемента И 51 он подается через шес той вход блока 18), то управление прохождением бита логического услов из блока 8 и соответствующего ему эталонного значения из регистра 50

рого тактового входа 34 устройства через первый вход блока 18 на синхро- вход регистра 50 сдвига, на входах записи и сдвига которого установятся единичные сигналы, полученные по сигналу с входа 40 через третий вход блока 18, производится запись кода эталонных значений логических условий с входа 41 устройства через четвертый вход блока 18 в регистр 50 сдвига. Тем же синхросигналом, поступающим через первый вход блока 17, элемент 47 задержки через открытый с входа .39 устройства по первому входу эле10

20

1067. 12

мент И 44 на счетный вход счетчика 43, на входе записи и информационном входе которого установятся коды, подаваемые соответственно с входа 38 устройства через третий вход блока 17 и с входа 37 устройства через второй вход блока 17, производится запись кода числа эталонных значений логических условий в счетчик 43.

Если загрузка счетчика 43 и регистра 50 сдвига осуществляется в одном 1щкле с контролем первой микрокоманды контролируемой ветви неко- 5 торой микропрограммы (допустимо загрузку осуществлять отдельным циклом) , то отдельные поля контрольной части микрокоманды поступают на соответствующие входы устройства вместе с адресом следующей микрокоманды из МУУ, как и при работе устройства в первом режиме. При этом значения на входах определяются типом считанной команды (безусловного перехода, ветв25 ления по произвольным или модифици- руемым адресам, прехода по многораз- рядным кодам) и подрежимом ее конт-

ления по произвольным или модифици- руемым адресам, прехода по многораз- рядным кодам) и подрежимом ее конт-

роля (например, контроль числа повторений группы микрокоманд), а работа

блоков устройства по контролю следования адресов осуществляется соответственно первому режиму, причем параллельно с контролем значений логических условий.

Код с входа 28 считывания логического условия устройства поступает параллельно на третий вход блока 8 и вход третьего элемента ИЛИ 19, а бит логического условия - с выхода

блока 8 на первые входы второго 15, третьего 16 элементов И и параллельно на третий вход четвертого элемента И 20. В зависимости от того, является ли первая микрокоманда микропрограм ветви микрокомандой ветвления

или нет, на входе элемента ИЛИ 19 устанавливается соответственно единичный или нулевой код, поступающий на первый вход четвертого элемента 20 И и через пятый вход блока 18 на третий вход элемента И 51. Так как на втором входе указанных элементов И устанавливается единичный сигнал, подаваемый с входа 39 устройства (для элемента И 51 он подается через шестой вход блока 18), то управление прохождением бита логического условия из блока 8 и соответствующего ему эталонного значения из регистра 50

13

сдвига и третьего входа элемента И

20и первого входа элемента И 51 на их выходы осуществляется сигналом н их первом и третьем входах. При нулевом сигнале на первом и третьем входах элементов И 20 и 51 происход блокировка вьщачи логического услов и соответствукщего ему эталонного значения. В результате с выхода элемента И 51 и блока 18 и с выхода четвертого элемента И 20 на первый

и второй входы схемы 21 сравнения поступают О, по которым на выходе последнего вьфабатывается нулевой сигнал, поступающий далее на вход соответствующего разряда регистра 4 результата. На другие разряды регисра 4 результата поступает код с вы- хбда сумматора 3 по модулю два, несущий информацию о контроле следования микрокоманд и используемый дл выработки признака и кода ошибки на выходах 35 и 36, как это было описано ранее.

При единичных сигналах на первом и третьем входах элементов И 20 и 5 (выполняется микрокоманда ветвления на второй и первьй входы схемы 21 сравнения считываются логическое условие, по которому- осуществляется ветвление в микрокоманде, и соответствующее ему эталонное значение. Пр одинаковых значениях на входах схем

21сравнения вырабатывает на выходе нулевой сигнал. Если значения на входах схемы 21 различны, то на выходе вырабатывается единичный сигна ошибки по контролю значений логических условий,- который записывается в соответствующий разряд регистра 4 результата и приводит к появлению ошибки на выходе 35 устройства. Возможные действия по ошибке контроля значения логических условий такие же, как и указанные ранее при описании первого режима работы устройства.

При отсутствии сигнала ошибки на выходе 35 устройства осуществляется считывание на входы устройства полей следующей микрокоманды ветви. Если контроль указанной микрокоманды не сопровождается загрузкой счетчика 43 и регистра 50 сдвига, то на входах 38, 40 снимаются управляюпще сигналы загрузкой (соответственно устанавливаются единичный и нулевой сигналы) . Если микрокоманда не являет10

01067

14

ся микрокомандой ветвления, нулевой сигнал с выхода третьего элемента 19 ИЛИ поступает на второй вход элемента И 44 (через пятьм вход блока 17), блокируя поступление синхросигнала с входа устройства 34, через первый вход блока 17, элемент 47 задержки, элемент И 44 на счетный вход счетчика 43. Таким образом, содержимое счетчика 43 не изменяется. При ненулевом значении счетчика 43 на выходе элемента ИЛИ 45 выработается единичный сигнал, поступающий на 15 первые входы элементов И-НЕ 48 и И 46, На выходе элемента И-НЕ 17 и выходе 42 устройства вырабатывается нулевой сигнал незавершенности контроля значений логических условий. Ну- 20 левой сигнал с пятого входа блока 17 (с выхода элемента ИЛИ 19), поступивший на второй вход элемента И 46, формирует нулевой сигнал на его выходе и на втором выходе блока 17, 25 который через второй выход блока 18 поступает на второй вход элемента ИЛИ 49. Так как и на первый вход элемента ИЛИ 49 подается через третий вход блока 18 нулевой сигнал с входа 40 устройства с выхода этого элемента на вход сдвига регистра 50 сдвига поступает нулевой сй гнал. На вход записи регистра 50 сдвига также поступает, сигнал с третьего входа блока 18 (со входа 40 устройства), Нулевые сигналы на входах записи и г. . сдвига регистра 50 сдвига обеспечивают запрет тактирования по сигналу на его синхровходе. Таким образом, содержимое регистра 50 сдвига не изменяется. Так как на выходе третьего элемента ИПИ 19 вьфабатывается нулевой сигнал (микрокоманда не является микрокомандой ветвления), этим сигналом блокируется появление ошибки по результату контроля логических значений,.

30

35

40

5

Если очередная микрокоманда является микрокомандой ветвле 1ия, то единичный сигнал с выхода третьего элемента ИЛИ 19, поступающий через пятый вход блока 17 на втодые входы соответственно элементов И 44 и 46, снимает блокировку с этих элементов. Та- КИМ образом, на выходе элемента И 46 и далее на втором выходе блока 17, втором входе блока 18, выходе элемента ИЛИ 49 и входе .сдвига регистра 50 сдвига установится единичный сигнал разрешения сдвига. По синхросигналу с входа 34 устройства, поступившему через первый вход блока 18 на синхровход регистра 50 сдвига, происходит сдвиг содержимого этого регистра, в результате которого на его выход поступает следующее эталонное значение логического условия. По тому же синхросигналу, поступившему через первый вход блока 17, элемент 47 задержки, открытьй элемент И 44 на счетный вход счетчика 43 изменяется (например, уменьшение) его содержимое на единицу. Последующая работа по сравнению логического условия и полученного эталонного значения с.оответствует описанному.

После использования последнего эталонного значения из регистра 50 сдвига содержимое счетчика 43 становится равным нулю, В этом случае на выходе элемента ИЛИ 45 вырабатывается нулевой сигнал, устанавливающий н

со счетным входом счетчика, вход записи и информационный вход которого являются соответственно входом зап и- си и входом задания числа эталонов устройства, группа выходов счетчика подключена к группе входов элемента ИЛИ, выход которого соединен с первыми входами второго элемента И и

элемента И-НЕ, вторые входы которых объединены соответственно с вторым и третьим входами первого элемента И и подключены соответственно к выходу третьего элемента ИЛИ устройства и входу задания режима контроля логических условий устройства, выход элемента И-НЕ является выходом признака конца контроля логических условий устройства, выход второго элемента И соединен с первым входом элемента ИЛИ блока формирования эталонов . логических условий, второй вход которого объединен с входом записи регистра сдвига и подключен к входу

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода микропрограмм | 1987 |

|

SU1430959A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет контроля значений логических условий при реализации ветвей микропрограмм. Цель достигается тем, что в устройство, содержащее блок 1 памяти, мультиплексор 2, сумматор 3 по модулю два, регистр 4 результата, первый элемент ИЛИ 5, элемент 6 задержки, регистр 7 данных, блок 8 анализа логических условий, блок 9 модификации кода контроля, счетчик 10, блок 11 элементов И, второй элемент ИЛИ 12, блок 13 элементов ИЛИ-НЕ, первый, второй и третий элементы И 14, 15, 16, дополнительно введены блок 17 управления эталонами логических условий, блок 18 формирования эталонов логических условий, третий элемент ИЛИ 19, четвертый элемент И 20, блок 21 сравнения. Устройство для контроля хода микропрограмм помимо контроля следования микрокоманд (безусловного перехода, ветвления по произвольным или модифицируемым адресам, перехода по многоразрядным кодам), микропрограмм и контроля заданного числа повторений микрокоманд микропрограммы обеспечивает расширение функциональных возможностей контроля за счет обеспечения контроля значений логических условий, используемых при выполнении микрокоманд ветвления микропрограммных ветвей с известными эталонными значениями условий. 3 ил.

выходе блока элемента И-НЁ 48 и да- 25 записи эталонов устройства, синхролее на первом выходе блока 17 и выхо- .

де 42 устройства единичный сигнал,

означающий завершение этапа контроля

значений логических условий. Указанг

ный сигнал может быть использован, 30

например, для прерывания процесса

контроля микрокоманд.

вход и информационный вход регистра сдвига блока формирования эталонов логических условий соединены соответ ственно с вторым тактовым входом и входом задания кода эталона устройства, вход разрешения сдвига и выход регистра сдвига соединены соответственно с выходом элемента ИЛИ и первы входом элемента И блока формирования эталонов логических условий, второй и третий входы которого подключены соответственно к входу задания режима контроля логических условий устройства и выходу третьего элемента ИЛИ устройства, выход элемента И бло ка формирования эталонов логических условий соединен с первым входом схе мы сравнения, второй вход которой соединен с выходом четвертого элемента И устройства, первьм и второй входы которого подключены соответственно к выходу третьего элемента ИЛИ и входу задания режима контроля логических условий устройства, третий вход четвертого элемента И соединен с выходом блока анализа логических условий, группа входов третьего элемента ИЛИ соединена с группой входов считывания логических условий устрой ства, выход схемы сравнения соединен

35

40

Формула изобретения

Устройство для контроля хода микропрограмм по авт. св. № 1430959, отличающееся тем, что, с Целью расширения функциональных возможностей за счет контроля значений логиче ских условий при р-еали- зации ветвей микропрограмм, в него введены блок управления эталонами логических условий, блок формирования эталонов логических условий, третий элемент ИЛИ, четвертый элемент И, . схема сравнения, причем блок управления эталонами логических условий со- держит счетчик, два элемента И, элемент ИЛИ, элемент И-НЕ, элемент задержки, блок формирования эталонов логических условий содержит регистр сдвига, элемент И, элемент ИЛИ, в блоке управления эталонами логических условий первый вход первого элемента И через элемент задержки подключен

50

вход и информационный вход регистра сдвига блока формирования эталонов логических условий соединены соотве ственно с вторым тактовым входом и входом задания кода эталона устройства, вход разрешения сдвига и выхо регистра сдвига соединены соответст венно с выходом элемента ИЛИ и перв входом элемента И блока формировани эталонов логических условий, второй и третий входы которого подключены соответственно к входу задания режи ма контроля логических условий устройства и выходу третьего элемента ИЛИ устройства, выход элемента И бл ка формирования эталонов логических условий соединен с первым входом сх мы сравнения, второй вход которой соединен с выходом четвертого элемента И устройства, первьм и второй входы которого подключены соответст венно к выходу третьего элемента ИЛИ и входу задания режима контроля логических условий устройства, третий вход четвертого элемента И соединен с выходом блока анализа логических условий, группа входов третьего эле мента ИЛИ соединена с группой входо считывания логических условий устро ства, выход схемы сравнения соедине

к второму тактовому входу устройства, с (т+1)-м входом регистра результавыход первого элемента И соединен

вход и информационный вход регистра сдвига блока формирования эталонов логических условий соединены соответственно с вторым тактовым входом и входом задания кода эталона устройства, вход разрешения сдвига и выход регистра сдвига соединены соответственно с выходом элемента ИЛИ и первым входом элемента И блока формирования эталонов логических условий, второй и третий входы которого подключены соответственно к входу задания режима контроля логических условий устройства и выходу третьего элемента ИЛИ устройства, выход элемента И блока формирования эталонов логических условий соединен с первым входом схемы сравнения, второй вход которой соединен с выходом четвертого элемента И устройства, первьм и второй входы которого подключены соответственно к выходу третьего элемента ИЛИ и входу задания режима контроля логических условий устройства, третий вход четвертого элемента И соединен с выходом блока анализа логических условий, группа входов третьего элемента ИЛИ соединена с группой входов считывания логических условий устройства, выход схемы сравнения соединен

с (т+1)-м входом регистра результата.

фие.2

Авторы

Даты

1989-08-15—Публикация

1988-01-05—Подача