О9

О СО

d

со

Изобретение относится к вычислительной технике, в частности к устройствам контроля ЭВМ, и может быть использовано при построении устройств программного и микропрограммного управления с высокой достоверностью функционирования.

Цель изобретения - повьшение достоверности и оперативности контроля.

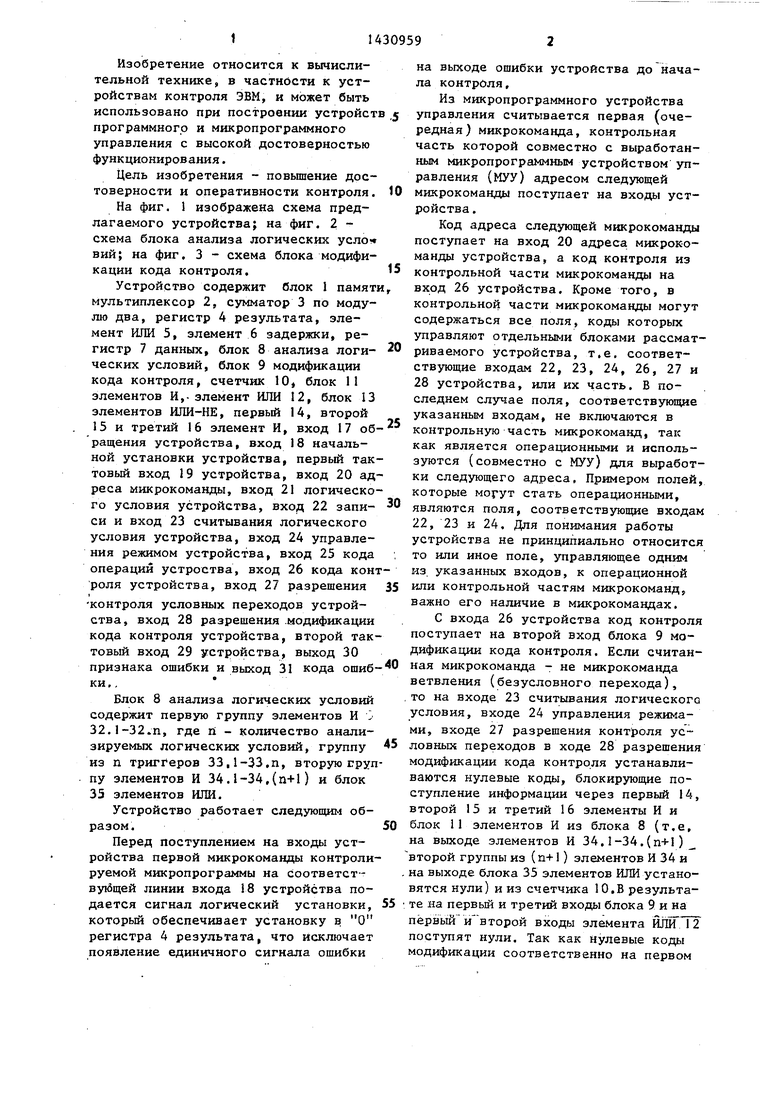

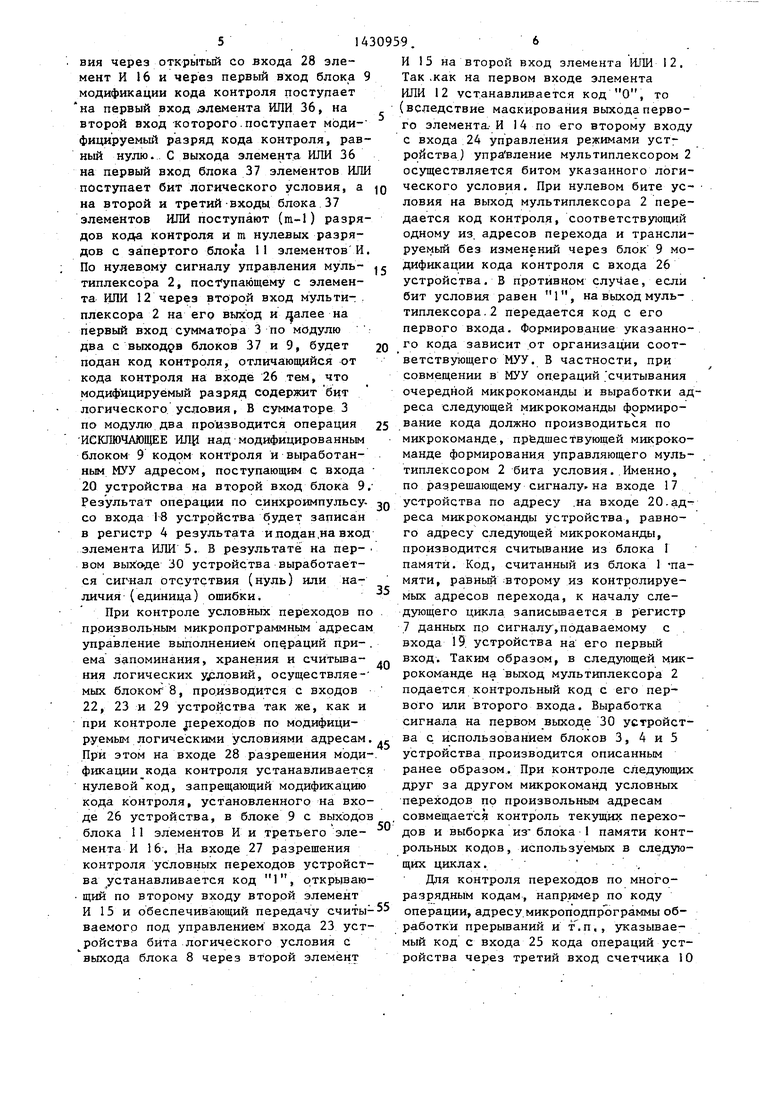

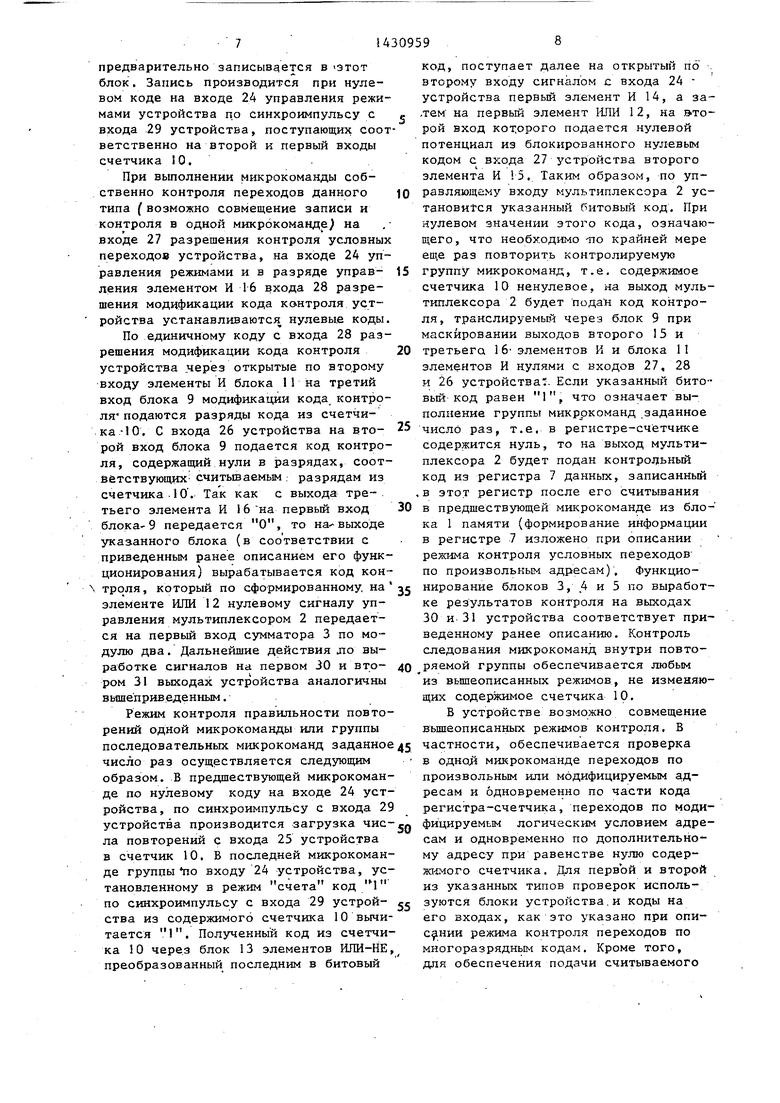

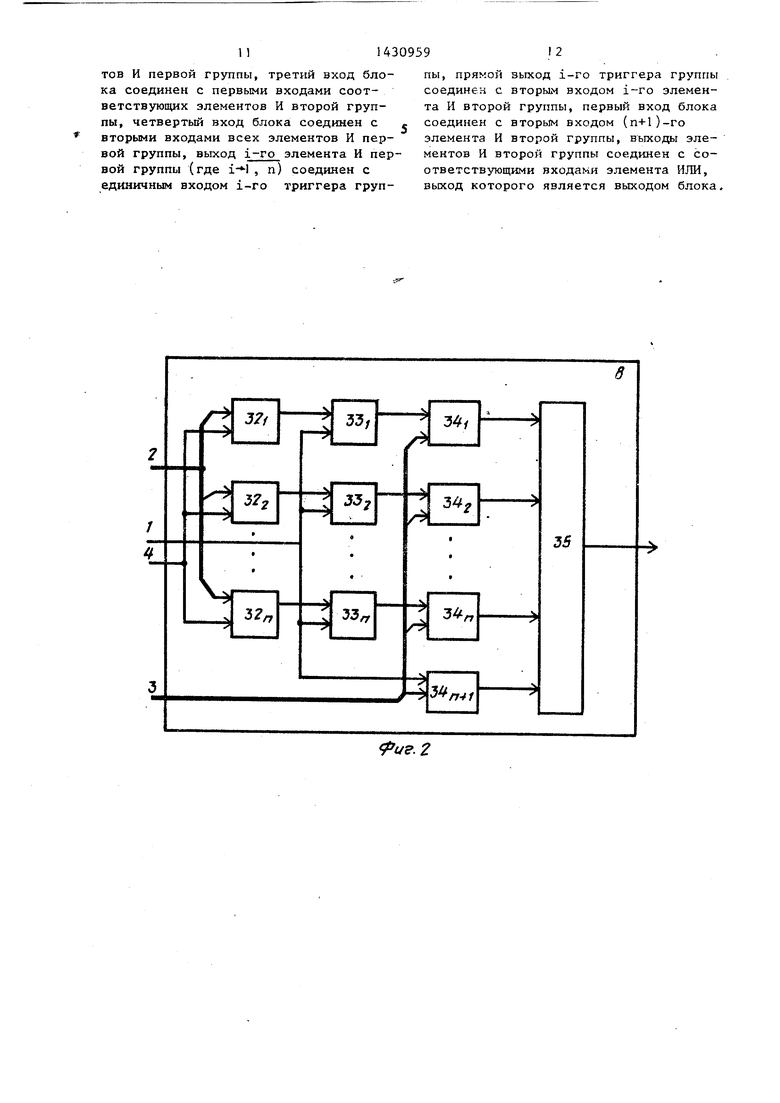

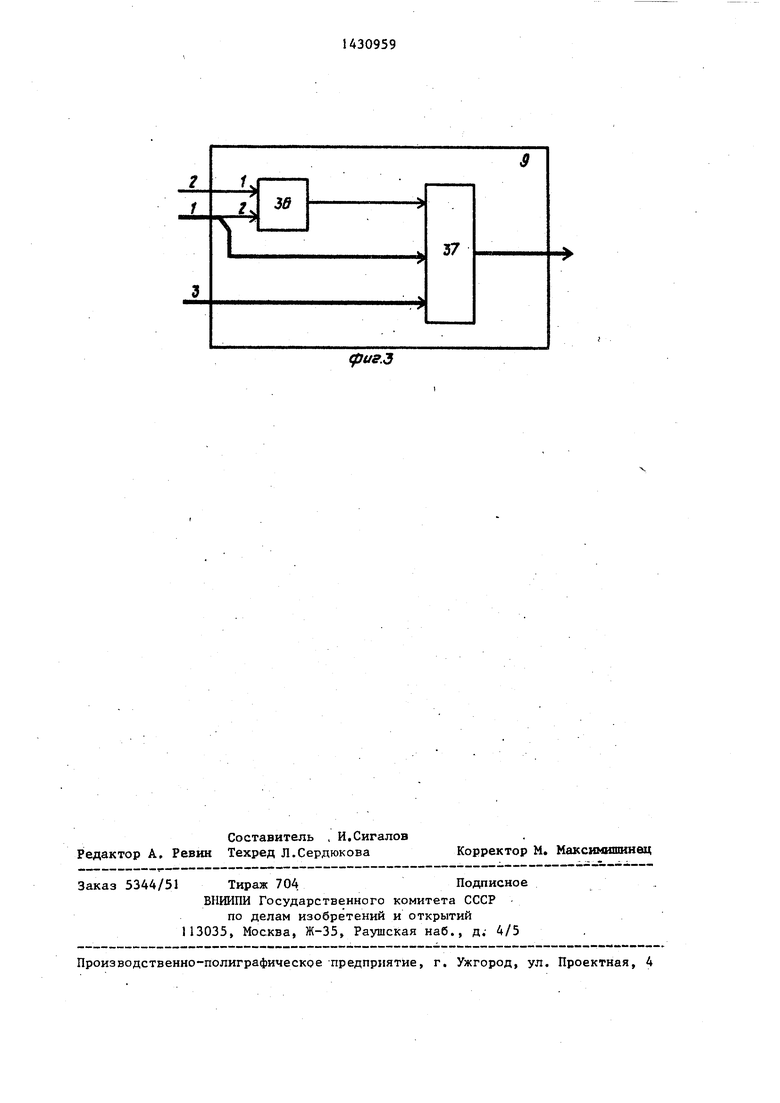

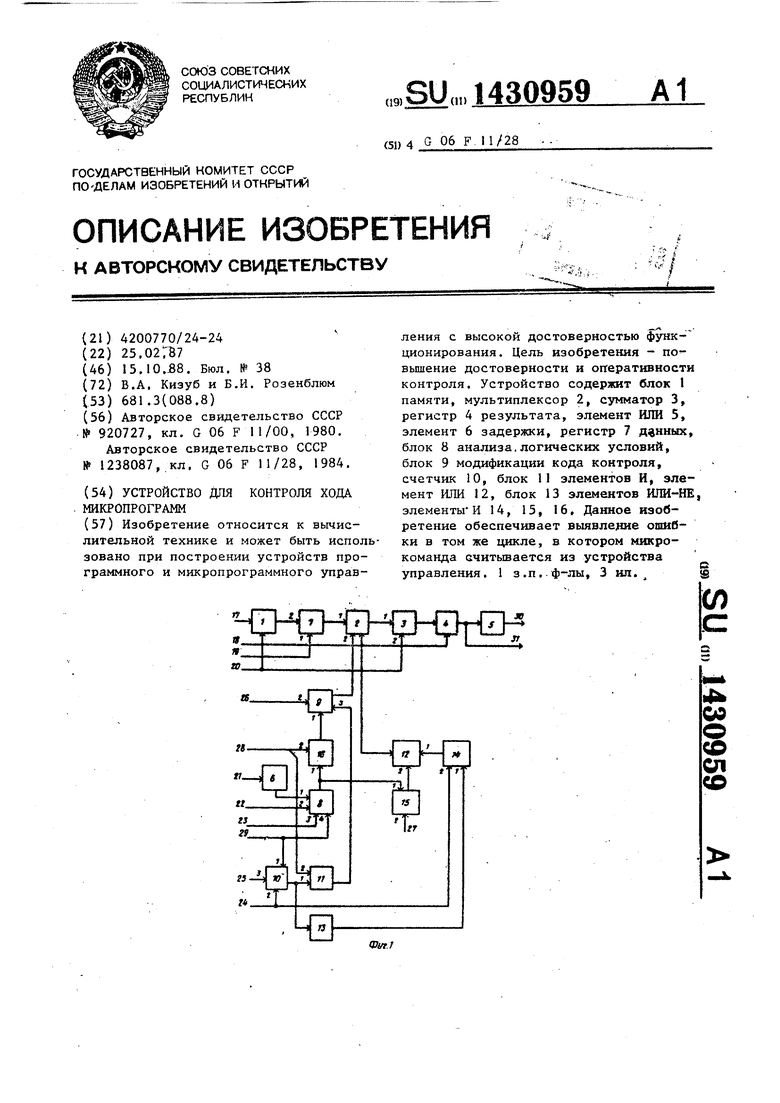

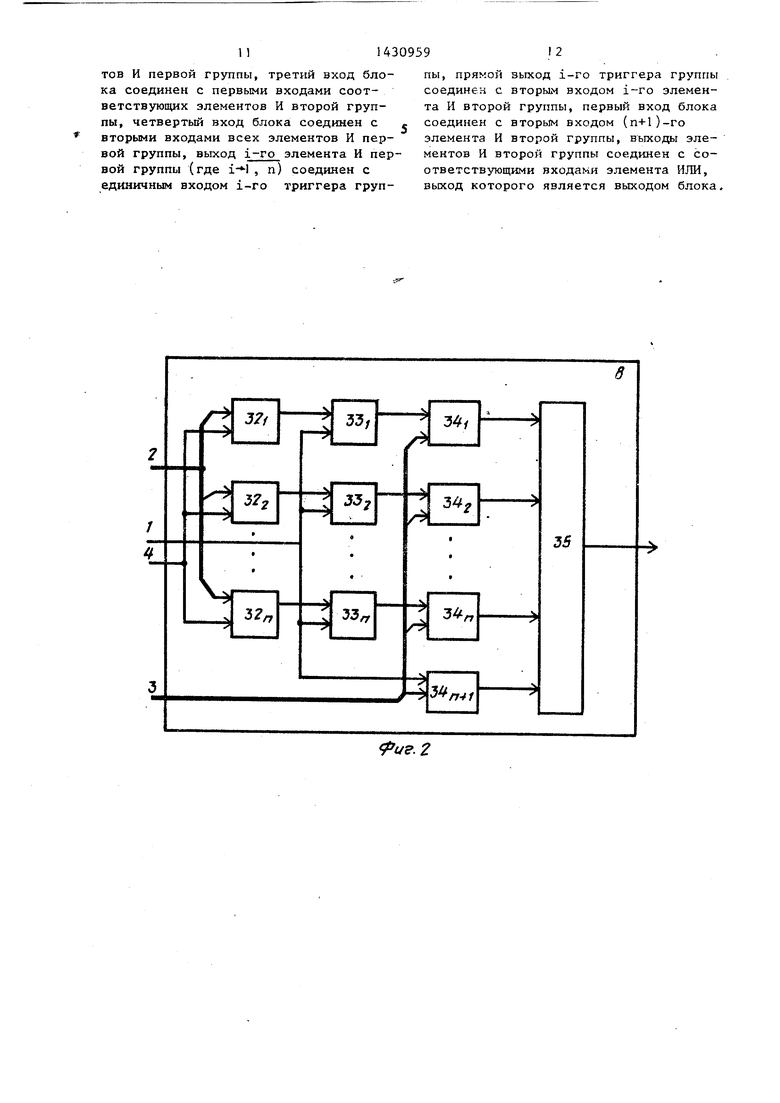

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - схема блока анализа логических усло« вий; на фиг, 3 - схема блока модификации кода контроля.

Устройство содержит блок 1 памяти мультиплексор 2, сумматор 3 по модулю два, регистр 4 результата, элемент ИЛИ 5, злемент 6 задержки, регистр 7 данных, блок 8 анализа логических условий, блок 9 модификации кода контроля, счетчик 10 блок 11 элементов И,-злемент ИЛИ 12, блок 13 элементов ИЛИ-НЕ, первый 14, второй 15 и третий 16 элемент И, вход 17 обращения устройства, вход 18 начальной установки устройства, первый тактовый вход 19 устройства, вход 20 адреса микрокоманды, вход 21 логического условия устройства, вход 22 записи и вход 23 считывания логического условия устройства, вход 24 управления режимом устройства, вход 25 кода операций устроства, вход 26 кода конт роля устройства, вход 27 разрешения

контроля условных переходов устройства, вход 28 разрешения .модификации кода контроля устройства, второй тактовый вход 29 устройства, выход 30 признака ошибки и выход 31 кода ошибки,.

Блок 8 анализа логических условий содержит первую группу элементов И 32.1-32.П, где и - количество анализируемых логических условий, группу из п триггеров 33,1-33,п, вторую группу элементов И 34 .1-34,(п+1) и блок 35 элементов ИЛИ.

Устройство работает следующим образом.

Перед поступлением на входы устройства первой микрокоманды контролируемой микропрограммы на соответст- вуйщей линии входа 18 устройства подается сигнал логический установки, которьш обеспечивает установку в. О регистра 4 результата, что исключает появление единичного сигнала ошибки

на выходе ошибки устройства до начала контроля,

Из микропрограммного устройства

управления считывается первая (очередная) микрокоманда, контрольная часть которой совместно с выработанным микропрограммным устройством управления (МУУ) адресом следующей

микрокоманды поступает на входы устройства.

Код адреса следующей микрокоманды поступает на вход 20 адреса микрокоманды устройства, а код контроля из контрольной части микрокоманды на вход 26 устройства. Кроме того, в контрольной части микрокоманды могут содержаться все поля, коды которых управляют отдельными блоками рассматриваемого устройства, т.е. соответствующие входам 22, 23, 24, 26, 27 и 28 устройства, или их часть. В последнем случае поля, соответствующие указанным входам, не включаются в контрольную часть микрокоманд, так как является операционными и используются (совместно с МУУ) для выработки следующего адреса, Примером полей, которые могут стать операционными,

являются поля, соответствующие входам 22, 23 и 24. Для понимания работы устройства не принципиально относится то Ш1И иное поле, управляющее одним из, указанных входов, к операционной

или контрольной частям микрокоманд, важно его наличие в микрокомандах,

С входа 26 устройства код контроля поступает на второй вход блока 9 модификации кода контроля. Если считанная микрокоманда - не микрокоманда ветвления (безусловного перехода), ,то на входе 23 считывания логического условия, входе 24 управления режимами, входе 27 разрешения контроля ус

ловных переходов в ходе 28 разрешения модификации кода контроля устанавливаются нулевые коды, блокирующие поступление информации через первый 14, второй 15 и третий 16 элементы И и

блок 11 элементов И из блока 8 (т.е, на выходе элементов И 34,1-34. (п+1 ) второй группы из (п+1) элементов И 34 и на выходе блока 35 элементов ИЛИ установятся нули) и из счетчика 10,В результа те на первый и третий входы блока 9 и на первый и второй входы элемента поступят нули. Так как нулевые коды модификации соответственно на первом

входе элемента tUlH 36 и третьем входе блока 37 элементов ИЛИ не изменяют разрядов кода контроля, поступающих на вторые входы указанных блоков,то на выходе блока 9 модификации кода контроля установится тот же код, что и на втором входе блока 9. По нулевому сигналу с выхода элемента ИЛИ 12, поступившему на управляющий входмуль типлексора 2, код контроля через второй вход мультиплексора 2 передается на его выход и далее на первый вход сумматора 3 по модулю два, на второй вход которого со входа 20 поступает адрес следующей микрокоманды По синхросигналу, поданному со второго уйравляющего входа 18, производится запись результата выполнения в блоке 8 поразрядной операции ИСКЛЮЧАЮЩЕЕ ИЛИ в регистр 4 результата.

Наличие единицы хотя бы в одном разряде регистра 4 результата свидетельствует об ошибке и приводит к .выработке на выходе элемента ИЛИ 5 и первом выходе 30 устройства сигнала единицы. Указанный сигнал может быть использован для блокировки выработки синхронизирующих импульсов в МУУ или для прерьшания микропрограммы с последующей передачей управления микропрограмме диагностики ошибок, использующей в качестве исходной диагностической информации код на выходе 3 устроства. При отсутствии ошибки формируются нулевые коды на выходе регистра 4 результата и на выходах 30 и 31 устройства.

Если на входы устройства (из МУУ) поступает микрокоманда перехода по модифицируемым логическим условиям адресам, то на вход 23 считывания . логического условия поступает код, содержащий в одном из разрядах единицу, а в остальных - нули. .На входы 26 и 20 устройства поступает код контроля, соответствующий данной микрокоманде, и адрес следующей микрокоманды, а на входы 24 и 27 устрой- ства и разряды управления блоком I1 элементов И входа 28 устройства (как и в случае контроля микрокоманд безусловного перехода) - нули. Код со входа 23 устройства поступает на третий вход блока 8 анализа логических условий и далее отдельными разрядами - на управляющие входы элементов И 34,Г-34.(п+1) второй группы из (п+1) элементов И,в результате чего п

5

0

5

из (п+1) элементов И этой группы будут заблокированы по выходу нулевыми разрядасш указанного кода, а один, на который поступает единичный разряд кода, - открыт, пропуская на вход блока 35 элементов Ш1И и далее на выход блока 8 бит логического условия. Указанное логическое условие может быть сформировано на выходе блока В либо непосредственно под управлением данной микрокоманды перехода, либо в одной из предыдущих микрокоманд. Для МУУ,I в которых следующий адрес вырабатьшается после считьшания очередной микрокоманды из микропрограммной памяти, использу5С-тся оба способа формирования логического условия. В МУУ, осуществляющих в одном цикле совмещение указанньк операций, может быть использован только второй из способов , В соответствии с первым способом код с входа 2 логического условия устройства поступает через элемент 6 задержки на первый вход блока 8 анализа логических условий. Если необходимо запомнить код условия, то на вход 22 записи логического условия подается код, содержащий все нули, кроме единственного разряда, равного единице, по которому открывается соответствующий элемент И первой группы из п элементов И 32.1-32,п, По синхроимпульсу, поданному со входа 29

с устройства через открытый элемент И первой группы из п элементов И 32.1- 32.11 на управляю ций вход соответствующего триггера из группы п триггеров 33.1-33.п,логическое условие запишется в этот триггер. Считывание этого кода на выходе блока 8 осуществляется вышеописанным образом, при равенстве первых п разрядов (n+l)- разрядного кода на входе 23 считьша5 ния логического условия и .п-разрядно го кода на входе 22 записи логического условия. Если предварительное запоминание не требуется, то на входе 22 устанавливается нулевой код, а на входе 23 разряд устанавливается в ,

0

0

0

единицу (т,е, элемент И 34,(п+1) открыт), остальные п разрядов - в нули, В соотв етствии со вторым способоА производится только считывание на g выходе блока 8 логических условий, предварительно записанного ,в один из триггеров группы триггеров 33,1-ЗЗ.п одной из предыдущих микрокоманд. С , выхода блока 8 бит логического уело10

20

25

51430959

ИЯ через открытьш со входа 28 элеент И 16 и через первый вход блока 9 одификации кода контроля поступает

на первый вход элемента ИЛИ 36, на второй вход которого.поступает моди- ицируемый разряд кода контроля, равный нулю. С выхода элемента ИЛИ 36 на первый вход блока 37 элементов ИЛИ поступает бит логического условия, а на второй и третий-входы блока 37 элементов ИЛИ поступают (т-1) разрядов кода контроля и m нулевых разрядов с за пертого блока 11 элементов И. По нулевому сигналу управления муль- типлексора 2, поступающему с элемента КШИ 12 через второй вход мульти- . плексора 2 на его выход и на первый вход сумматора 3 по модулю два с выходрв блоков 37 и 9, будет подан код контроля, отличающийся от кода контроля на входе 26 тем, что модифицируемый разряд содержит бит логического условия, В сумматоре 3 по модулю два производится операция ИСКЛЮЧАЮЩЕЕ ИЛ над Модифицированным блоком 9 кодом контроля и выработанным МУУ адресом, поступающим с входа 20 устройства на второй вход блока 9. Результат операции по синхроимпульсу- со входа 18 устройства будет записан в регистр 4 результата иподан.на вход элемента ИЛИ 5, В результате на первом выходе 30 устройства выработается сигнал отсутствия (нуль) или наличия (единица) ошибки.

При контроле условных переходов по произвольным микропрограммным адресам управление выполнением операций при-. ема запоминания, хранения и считьша- ния логических у гловий, осуществляемых блококг 8, производится с входов 22, 23 и 29 устройства так же, как и при контроле терехоДов по модифицируемым логическими условиями адресам, -с При этом на входе 28 разрешения моди-. фикации кода контроля устанавливается нулевой код, запрещающий модификацию кода контроля, установленного на входе 26 устройства, в блоке 9 с выходов блока 11 элементов И и третьего элемента И 16, На входе 27 разрешения контроля условных переходов устройства устанавливается код 1, рткрывающий по второму входу второй элемент И 15 и обеспечивающий передачу считы-55 ваемогр под управлением входа 23 устройства бита логического условия с

выхода блока 8 через второй элемент

30

35

40

0

0

5

-с

55

30

35

40

И 15 на второй вход элемента ИЛИ 12. Так .как на первом входе элемента ИЛИ 12 устанавливается код О, то (вследствие маскирования выхода первого элемента- И 14 по его второму входу с входа 24 управления режимами устройства) упра вление мультиплексором 2 осуществляется битом указанного логического условия. При нулевом бите ус- - ловия на выход мультиплексора 2 передается код контроля, соответствующий одному из, адресов перехода и транслируемый без изменений через блок 9 модификации кода контроля с входа 26 устройства. В противном случае, если бит условия равен 1, на выход муль- . типлексора.2 передается код с его первого входа. Формирование указанного кода зависит от организации соответствующего МУУ. В частности, при совмещении в МУУ операций считывания очередной микрокоманды и выработки адреса следующей микрокоманды формирование кода должно производиться по микрокоманде, предшествующей микрокоманде формирования управляющего мультиплексором 2 бита условия..Именно, по разрешающему сигналу на входе 17 ус-тройства по адресу .на входе 20.адреса микрокоманды устройства, равного адресу следующей микрокоманды, производится считывание из блока 1 памяти. Код, считанный из блока 1 -памяти, равный второму из контролируемых адресов перехода, к началу следующего цикла записьшается в регистр 7 данных по сигналу,подаваемому с входа 19. устройства на его первый вход. Таким образом, в следующей мик- рокоианде на выход мультиплексора 2 подается контрольный код с его первого или второго входа. Выработка сигнала на первом выходе 30 устройства с. использованием блоков 3, 4 и 5 устройства производится описанным ранее образом. При контроле следующих друг за другом микрокоманд условных переходов по произвольным адресам совмещается контроль текущих переходов и выборка ИЗ блока 1 памяти контрольных кодов, используемых в следующих циклах. ,

Для контроля переходов по многоразрядным кодам, например по коду операции, адресу.микроподпрограммы обработки прерываний и т .п., указываемый код с входа 25 кода операций устройства через третий вход счетчика 10

7 14309598

предварительно записывается в«этоткод, поступает далее на открытый по . блок. Запись производится при нуле-второму входу сигналом с входа 24 - вон коде на входе 24 управления режи-устройства первый элемент И 14, а замами устройства по синхроимпульсу с с-тем на первый элемент ИЛИ 12, на вто- входа 29 устройства, поступающих соот-рой вход кот.орого подается нулевой ветственно на второй и первый входыпотенциал из блокированного нулевым счетчика 10. .кодом с входа 27 устройства второго

При вьтолнении микрокоманды соб-элемента И 15. Таким образом, по уп- ственно контроля переходов данного юравляющему входу мультиплексора 2 ус- типа (возможно совмещение записи итановится указанный битовый код. При контроля в однор микрокоманде на ,нулевом значении этого кода, означаю- входе 27 разрешения контроля условныхщего, что необходимо -по крайней мере переходов устройства, на входе 24 уп-еще раз повторить контролируемую равления режимами и в разряде управ- 15группу микрокоманд, т.е. содержимое ления элементом И 16 входа 28 разре-счетчика 10 ненулевое, на выход муль- шения модификации кода контроля уст-типлексора 2 будет подак код контро- ройства устанавливаются нулевые коды.ля, транслируемый через блок 9 при

По единичному коду с входа 28 раз-маскировании выходов второго 15 и

решения модификации кода контроля 20третьего 16- элементов И и блока 11

устройства .через открытые по второмуэлементов И нулями с входов 27, 28

входу элементы И блока 1 Г на третийи 26 устройства. Если указанный битовход блока 9 модификации кода контро-вый код равен 1, что означает выля подаются разряды кода из счетчи-полнение группы микрокоманд заданное

ка.-Ю. С входа 26 устройства на вто- 25число раз, т.е. в регистре-счетчике

рой вход блока 9 подается код контро-содержится нуль, то на выход мультиля, содержащий нули в разрядах, соот-плексора 2 будет подан контродьный

ветствующих считьшаемым, разрядам изкод из регистра 7 данных, записанный

счетчика. 10. Так как с выхода тре-,.в этот регистр после его считывания

тьего элемента И 16 на первый вход 30в предшествующей микрокоманде из блоблока-9 передается О, то на выходека 1 памяти (формирование информации

указанного блока (в соответствии с в регистре 7 изложено при описании

приведенным ранее описанием его функ-режима контроля условных переходов

ционирования) вырабатывается код кон-по произвольным адресам). Функцио троля, который по сформированному, на jjнирование блоков 3, .4 и 5 по выработэлементе ИЛИ 12 нулевому сигналу уп-ке результатов контроля на выходах

равления мультиплексором 2 передает-30 и-31 устройства соответствует прися на первый вход сумматора 3 по мо-веденному ранее описанию. Контроль

дулю два. Дальнейшие действия ло вы-следования микрокоманд внутри повтоработке сигналов на первом 30 и вто- 40ряемой группы обеспе чивается любым

ром 31 выходах устройства аналогичныиз вьшеописанных режимов, не изменяювыше приведенным.щих содержимое счетчика 10.

Режим контроля правильности повто- В устройстве возможно совмещение

рений одной микрокоманды или группывьщ1еописанных режимов контроля. В

последовательных микрокоманд заданное45частности, обеспечивается проверка

число раз осуществляется следзпощим в одной микрокоманде переходов по

образом. В предшествующей микрокоман-произвольным или модифицируемым адде по нулевому коду на входе 24 уст-ресам и одновременно по части кода

ройства, по синхроимпульсу с входа 29регистра-счетчика, переходов по модиустройства производится загрузка чис-сдфицируемым логическим условием адрела повторений с входа 25 устройствасам и одновременно по дополнительно

в счетчик 10. В последней микрокоман-му адресу при равенстве нулю содерде группы по входу 24 устройства, ус-ш мого счетчика. Для первой и второй

тановленному в режим счета код М из указанных типов проверок испольпо синхроимпульсу с входа 29 устрой- зуются блоки устройства.и коды на

ства из содержимого счетчика 10 вьми-его входах, как это указано при опитается 1. Полученный код из счетчи-с нии режима контроля переходов по

ка 10 через блок 13 элементов ИЛИ-НЕ,многоразрядньгм кодам. Кроме того,

преобразованный последним в битовыйдля обеспечения подачи считываемого

91

под управлением входа 23 устройства из блока 8 на управляюпщй вход мультиплексора 2 логического условия на входе 27 устройства устанавпивается код I, обеспечивающий прохождение сигнала условия через второй элемент И 15 (первый тип .проверок), Для обеспечения передачи логического условия из блока 8 через элемент И I6 на nep вьй вход блока 9 с входа 28 устройства подается код 1 (второй тип проверок). Тем самым обеспечивается коммутация соответствующих цепей передачи логического условия и возмож- ность совместного использования режимов контроля. Для третьего типа совместных проверок используются блоки и входы устройства,как это бьшо указано при описании режимов контроля правильности повторений микрокоманд заданное число раз и контроля перекодов по модифицируемым логическими условиями адресам.

-Формула изобретения

1, Устройство для контроля хода

микропрограмм, содержащее блок памяти, мультиплексор, сумматор по.модулю два,, регистр результата, первый элемент ИЛИ и элемент задержки, причем выход мультиплексора соединен с первым входом сумматора по модулю

10

S 0

5

0

дом мультиплексора, вход адреса микрокоманды устройства соединен с адресным входом блока памяти и вторым входом сумматора по модулю два, выход элемента задержки соединен с перйым входом блока анализа логических условий, вькод регистра результата является выходом кода ошибки устройства, входы кода контроля,кода операции, записи и считьшания логического условия устройства соединены с первым входом блока модификации контроля, с информационным входом счетчика, с вторым и третьим входами блока анализа логических условий, второй так-. товый вход устройства соединен с четвертым входом блока анализа устройства и счетным входом счетчика, выход которого соединен с первыми входами элементов И блока элементов И и входами элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И, вход управления устройства соединен с входом направления счета счетчика и вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ; в ыход блока анализа логических .условий соединен с первыми входами второго и третьего элемент . тов и, вход разрешения контроля условных, переходов соединен с вторым входом второго элемента И, выход ко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода микропрограмм | 1988 |

|

SU1501067A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств программного и микропрограммного управления с высокой достоверностью функ- ционирования. Цель изобретения - по вьшение достоверности и оггеративнести контроля. Устройство содержит блок 1 памяти, мультиплексор 2, сумматор 3, регистр 4 результата, элемент ШШ 5, элемент 6 задеряски, регистр 7 данных, блок 8 анализа.логических условий, блок 9 модификации кода контроля, счетчик 10, блок 11 элементов И, элемент ИЛИ 12, блок 13 элементов ИЛИ-НЕ, элементы И 14, 15, 16, Данное изобретение обеспечивает выявле ние ошибки в том же цикле, в котором микрокоманда считывается иэ устройства управления. 1 з.п. ф-лы, 3 ил.

два, выход которого соединен с инфор-35 торого соединен с вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с управляющим входом мультиплексора, вход разрешения модификации кода контроля устройства соединен с вторыми входами блока элементов И и с вторым входом третьего элемента И, выходы третьего элемента И и блока элементов И соединены соответственно с вторым и трет тьим в.ходами блока модификации контроля, выход которого соединен с вторым информационным входом мультиплексора .

мационным входом регистра результата,- выход регистра результата соединен с входами первого элемента РШИ, выход которого является выходом признака ошибки устройства, входы обращения, 40 начальной установки и логического условия устройства соединены соответственно с входом чтения блока памяти, входом начальной установки регистра результата и входом элемента задерж- 45 ки, отличающееся там, что, с целью повышения достоверности и оперативности контроля, в устройство введены регистр данных, блок: анализа логических условий, блок моди д фикации кода контроля, счетчик, блок элементов И, второй элемент ИЛИ, блок элементов ИЛИ-НЕ, первый, второй и третий элементы И, причем первый тактовый вход устройства и выход блока g памяти соединены соответственно с входом записи и информационным входом регистра данных, выход которого соединен с первым информационным вхоторого соединен с вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с управляющим входом мультиплексора, вход разрешения модификации кода контроля устройства соединен с вторыми входами блока элементов И и с вторым входом третьего элемента И, выходы третьего элемента И и блока элементов И соединены соответственно с вторым и трет тьим в.ходами блока модификации контроля, выход которого соединен с вторым информационным входом мультиплексора .

2, Устройство по п, чающееся тем, за логических условий содержит первую группу из п элементов И, где п - количество анализируемых логических условий, п триггеров, вторую группу из п+1 элементов И и элемент ИЛИ, причем первый вход блока соединен с входами установки в О всех триггеров группы, второй вход блока соединен с первыми входами соответствующих элемен1

что

о т л и - блок аналитов и первой группы, третий вход блока соединен с первыми входами соответствующих элементов И второй группы, четвертый вход блока соединен с е вторыми входами всех элементов И первой группы, выход i-ro элемента И первой группы (где , п) соединен с единичным входом i-ro триггера группы, прямой зьгход i-ro триггера группы соединен с вторым входом i-ro элемента И второй группы, первый вход блока соединен с вторым входом (п+1)-го элемента И второй группы, выходы элементов И второй группы соединен с соответствующими входами элемента ИЛИ, выход которого является выходом блока,

и.2

ериг.э

| Микропрограммное устройство управления с контролем | 1980 |

|

SU920727A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода микропрограммы | 1984 |

|

SU1238087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1987-02-25—Подача