первого коммутатора, с первым входо элемента И и с первым входом задани режима устройства второй вход задания режима которого подключен к управляющему входу второго коммутатора, первьш вход первой группы которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с выходом rrt-ro разряда первого регистра, с вторым выходом устройства, первый вход второй группы второго коммутатора подключен к выходу первого элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ, второй вход первой группы и второй вход второй группы второго коммутатора, объединенньш с вторым управляющим входом вида операции третьего блока суммирования, подключены к четвертым информационным входам устройства, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу знакового разряда третьего блока суммирования, fri -и и (fcn +1)-й разряды второго блока сумирования подключены соответственно к первому и второму входам второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход коИзобретение относится к вычислительной технике и может быть исполь- вано в специализированных цифровых вычислительных устройствах.

Цель изобретения - расширение области применения устройства за счет увеличения диапазона входных данных, вычисления суммы произведений и вычисления квадратичной функции,

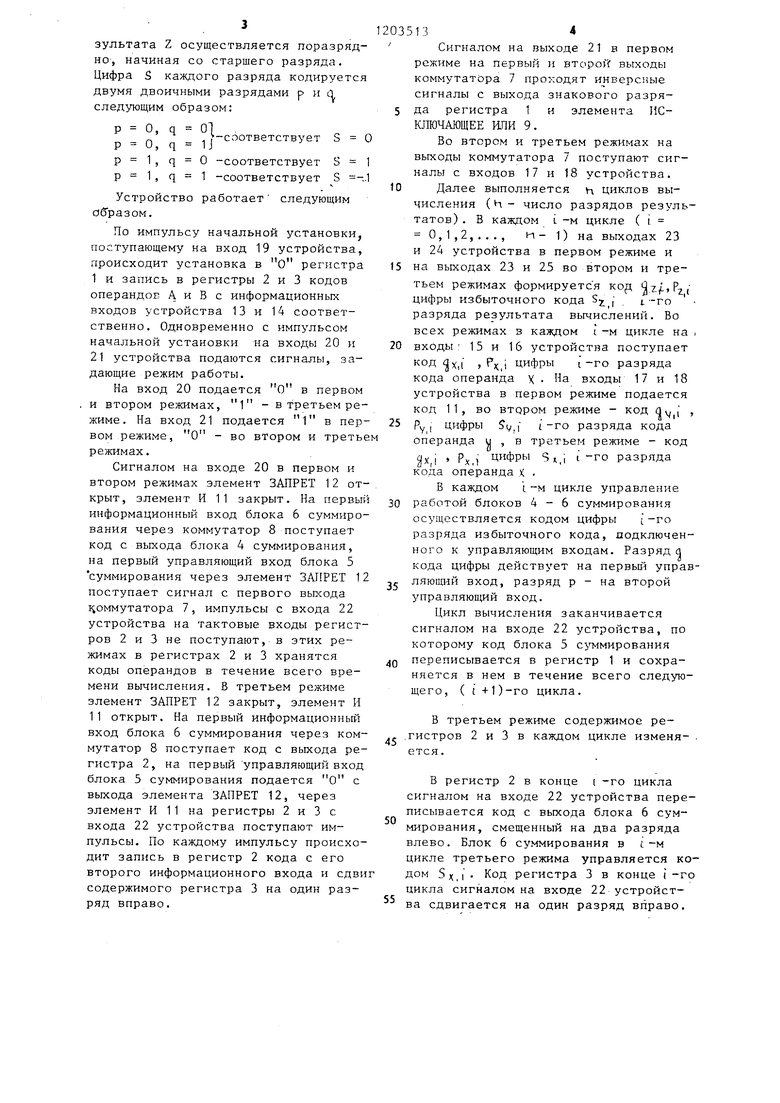

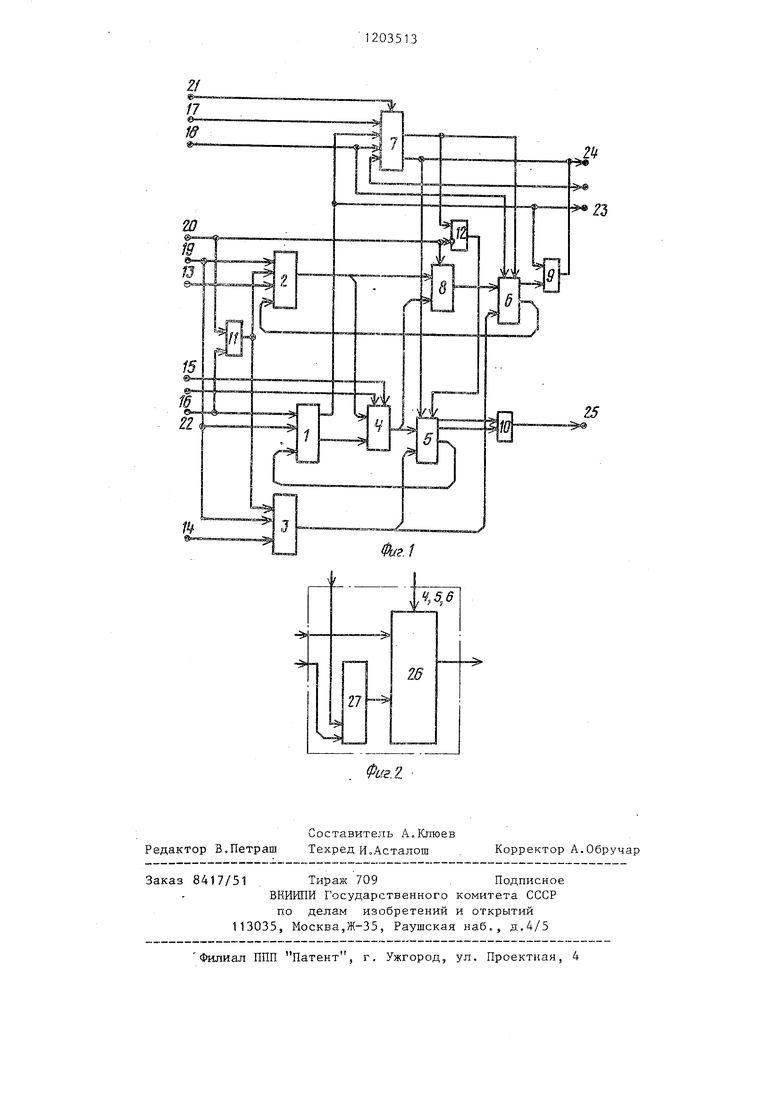

На фиг. 1 представлена схема вычислительного устройства; на фиг. 2 - схема блока суммирования.

Вычислительное устройство содержит регистры 1-3, блоки 4-6 суммирования, коммутаторы 7 и 8, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и 10, элемент И 11, элемент ЗАПРЕТ 12, первый 13, второй 14, третьи 15 и 16, четвертые 17 и 18 информационные входы, вход 19 начальной установки, первый 20 и второй 21 входы задания режима, тактовый вход 22, выходы 23 - 25. 13

торого подключен к третьему вьгходу устройства, вторые управляющие входы приема информации второго и третьего регистров подключены к выходу элемента И, второй вход которого подключен к тактовому входу устройства (hn- число разрядов первого регистра).

2. Устройство по п. 1, отличающееся тем, что блок мирования содержит сумматор-вычита- тель и блок элементов И, причем первый и второй информационные входы блока суммирования соединены соответственно с первым информационным входом сумматора-вычитателя и информационным входом блока элементов И, первый и второй управляющие входы вида операции блока суммирования соединены соответственно с упраляющими входами сумматора-вычитателя и блока элементов И, выход блока элементов И соединен с вторым инфор .мационным входом сумматора-вычитателя, выход которого является выходом блока суммирования.

Блок суммирования содержит сумма- тор-вычитатель 26 и блок 27 элементов И.

При отсутствии сигнала на управ- ляющем. входе коммутатора 7 на его выход передается информация с второй группы входов, при наличии сигнала на управляющем входе - проинвертиро- ванная информация с первой группы входов. Блоки 4-6 суммирования складывают при значении входов вида операции 01, вычитают - при 11, повторяют на выходе код первого информационного входа - при 00, 10. Вычислительное устройство работает в трех режимах. В первом реА

жиме вычисляется функция 2 х,

В

во втором - функция Z Ах+Ву,втре- тьем - функция Z Ах+Вх . Операнды А и В представлены параллельным двоичным кодом, отрицательные числа - дополнительным кодом. Прием операндов х и у, а также выдача результата Z осуществляется поразрядно, начиная со старшего разряда. Цифра S каждого разряда кодируется двумя двоичными разрядами р и п следующим образом:

-соответствует

р О,q 0

Р О,q и

р 1 ,q О -соответствует S 1

Р 1 ,q 1 -соответствует S -..1

Устройство работает следующим об разом.

По импульсу начальной установки, поступающему на вход 19 устройства, происходит установка в О регистра

Iи запись в регистры 2 и 3 кодов операндов А и В с информационных входов устройства 13 и 14 соответственно. Одновременно с импульсом начальной установки на входы 20 и 21 устройства подаются сигналы, задающие режим работы.

На вход 20 подается О в первом и втором режимах, 1 - в третьем режиме. На вход 21 подается 1 в первом режиме, О - во втором и третье режимах.

Сигналом на входе 20 в первом и втором режимах элемент ЗАПРЕТ 12 от- крыт, элемент И 11 закрыт. На первый информационный вход блока 6 суммирования через коммутатор 8 поступает код с выхода блока 4 суммирования, на первый управляющий вход блока 5 суммирования через элемент ЗАПРЕТ 12 поступает сигнал с первого выхода г;оммутатора 7, импульсы с входа 22 устройства на тактовые входы регистров 2 и 3 не поступают, в этих режимах в регистрах 2 и 3 хранятся коды операндов в течение всего времени вычисления. В третьем режиме элемент ЗАПРЕТ 12 закрыт, элемент И

IIоткрыт. На первый информационный вход блока б суммирования через коммутатор 8 поступает код с выхода регистра 2, на первый управляющий вход блока 5 суммирования подается О с выхода элемента ЗАПРЕТ 12, через элемент И 11 на регистры 2 и 3 с входа 22 устройства поступают импульсы. По каждому импульсу происходит запись в регистр 2 кода с его второго информационного входа и сдви содержимого регистра 3 на один разряд вправо.

035134

Сигналом на выходе 21 в первом режиме на первый и второй выходы коммутатора 7 проходят инверсные сигналы с выхода знакового разря- 5 да регистра 1 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9.

Во втором и третьем режимах на выходы коммутатора 7 поступают сигналы с входов 17 и 18 устройства.

10 Далее выполняется v циклов вычисления (и- число разрядов результатов) . В каждом L-м цикле ( t 0,1,2,..., и- 1) на выходах 23 и 24 устройства в первом режиме и

15 на выходах 23 и 25 во втором и третьем режимах формируетс я кof Q. цифры избыточного кода z . разряда ре зультата вычислений. Во всех режимах в каждом i -м цикле на .

20 ВХОДЫ: 15 и 16 устройства поступает код х,1 РХ,| цифры 1-го разряда кода операнда у Н входы 17 и 18 устройства в первом режиме подается код 11, во втором режиме - код ,

25 р I цифры Sv.i i-го разряда кода операнда и , в третьем режиме - код ,1 , р, цифры Si.i t -го разряда кода операнда X .

В каждом I -м цикле управление

30 работой блоков 4-6 суммирования осуществляется кодом цифры -го разряда избыточного кода, подключенного к управляющим входам. Разряд а , „„

кода цифры действует на первьп1 управэг ляющий вход, разряд р - на второй З правляюид1й вход.

Цикл вычисления заканчивается сигналом на входе 22 устройства, по которому код блока 5 с гммирования

jjQ переписывается в регистр 1 и сохраняется в нем в течение всего следующего, ( i +1)-го цикла.

В третьем режиме содержимое ре- гистров 2 и 3 в каждом цикле изменя- . ется.

В регистр 2 в конце ( -го цикла сигналом на входе 22 устройства переписывается код с выхода блока 6 суммирования, смещенный на два разряда влево. Блок 6 суммирования в (.-м цикле третьего режима управляется кодом Sx,i- Код регистра 3 в конце (-го цикла сигналом на входе 22 устройства сдвигается на один разряд вправо.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Вычислительное устройство | 1983 |

|

SU1173411A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Составитель А.Кпюев Редактор В.Петраш Техред и,Асталош

Заказ 8417/51 Тираж 709 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г, Ужгород, ул. Проектная,

Фаг. 2.

Корректор А.Обручар

| Устройство для умножения | 1977 |

|

SU662939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения последова-ТЕльНОгО КОдА HA дРОбНый КОэффициЕНТ | 1979 |

|

SU794634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-16—Подача