(Б) УСТРОЙСТВО для ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА

1

I

Изобретение относится к вычислительной технике.

Известно устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры, коммутаторы, блоки .сдвига, элементы.НЕ, блок анализа знака Г11;

Недостатком данного устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является уст ройство для вычисления модуля комп- лексного числа, которое содержит регистры, сумматоры и коммутаторы, при-,5 чем входы первого и второго регистров подключены к первому и второму входам устройства, прямые выходы разрядов первого регистра подключены к группе первых входов первого суммато-20 ра соответственно, выход первого коммутатора подключен к первому входу второго сумматора. прямые выходы разрядов первого регистра подключены к

первым группам информационных входов первого и второго коммутаторов, вторые группы информационных входов которых подключены к прямым выходам разрядов второго регистра, инверсные выходы которых подключены к группе вторых входов первого сумматора, выход которого подключен к управляющим входам первого и второго коммутаторов , выход второго коммутатора подключен к второму входу второго сумматора, выход которого подключен к выходу устройства 2 J

Недостатком известного устройства является его низкое быстродействие.

Цель изобретения - повышение быстт роде,йствия устройства..

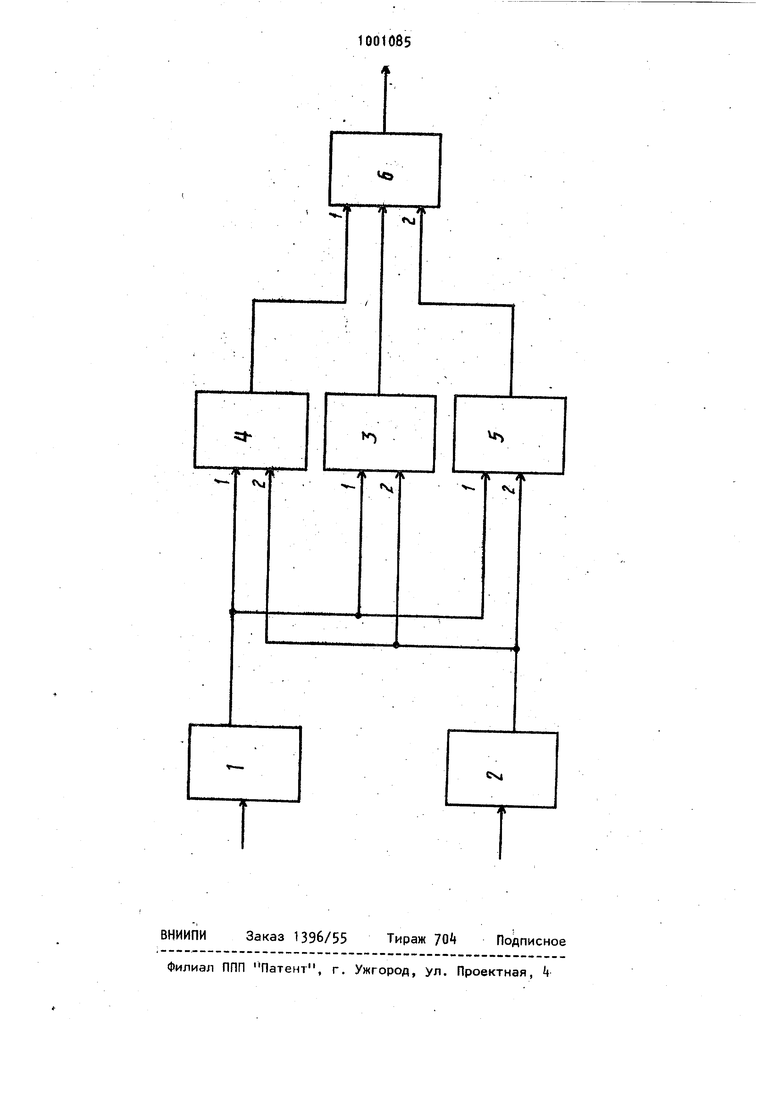

Поставленная цель достигается тем, что устройство для вычисления модуля комплексного числа, содержащее регист эы, сумматоры и коммутатор, причем входы разрядов первого и второго регистров подключены к информационным входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумматора, инверсные выходы разрядов второго регистра подключены к второй группе входов первого сумматора, прямой и инверсные выходы знакового разряда ко торого подключены к управляющему входу коммутатора, устройство содержит также третий сумматор, причем первая группа входов второго сумматора подключена к прямым выходам разрядов пер вого регистра,, (п-2) старшихразрядов которого подключены к первой группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (п-2) старших разрядов которого подключены к второй группе входов второго сумматора, выходы разрядов второго и третьего сумматоров подключены к первой и второй группе информационных входов коммутатора соответственно, выход которого подключен к выходу устройства. На чертеже представлена структурная схема устройства. Устройство содержит первый регистр 1, второй регистр 2, первый сумматор 3, второй сумматор , третий сумматор 5, коммутатор 6. Устройство работает следующим образом. В начальный момент времени в первый регистр 1 и второй регистр 2 заносятся соответственно п-разрядные мантиссы прямых кодов действительной и мнимой составляющих комплексного числа. С выхода первого регистра 1 прямой код действительной.составляющей поступает на первые входы первого 3 и второго сумматора, а п-2 старших разрядов этого кода - на первый вход третьего сумматора 5. С выхода второго регистра 2 инверс ный код мнимой составляющей поступает на второй вход первого сумматора 3, прямой код - на второй вход третьего сумматора 5 а п-2 старших разряда на второй вход второго ЭТОГО кода сумматора k. Сигнал с выхода знакового разряда сумматора 3 поступает на управляющий вход коммутатору 6, на первые информационные входы которого поступает с выхода второго сумматора k результат сложения кода действительной составляющей с мнимой, сдвинутой,на два разряда в сторону младших разрядов. На.вторые информационные вхОды коммутатора 6 поступает с выхода третьего сумматора 5 результат сложения кода мнимой-составляющей с действительной, сдвинутой на два разряда в сторону младших разрядов. При соответствующем управляющем сигнале, подаваемом на коммутатор, на его выходе вырабатывается результат сложения большей составляющей комплексного числа с меньшей составляющей, сдвинутой на два разряда в сторону младших раз-. рядов. Коммутатор 6 представляет собой набор из п элементов 2 И-ИЛИ, на входы каждого элемента подаются соответственно сигналы с выходов второго и третьего сумматоров 4 и 5 и. два управляющих, сигнала, являющихся прямым и инверсным сигналами знакового разряда. На выходе коммутатора 6 в зависимости от управляющих сигналов образуется результат, снимаемый с выхода второго или третьего сумматоров k или 5Устройство позволяет производить вычисление модуля комплексного числа при повышении быстродействия по сравнению с прототипом. Время выполнения вычислений в предлагаемом устройстве оказывается меньше по сравнению с прототипом на задержку сумматора (при несущественном изменении в затратах оборудования вместо одного коммутатора введен третий сумматор). Реализация устройства для вычисления модуля комплексного числа связана с развитием цифровой обработки сигналов в задачах спектрального анализа и является новой перспективной областью вычислительной техники. Устройство по сравнению с прототипом позволяет повысить быстродействие вычисления модуля комплексного числа. Задержка, вносимая базовым устройством ,+Тц, где 17 задержка празрядного сумматора; задержка коммутатора. Задержка, вносимая устройством ;; Cc.t K+Сс учитывая, что ,, . Выигрыш в быстродействии без существенных изменений затрат оборудования составляетТ - р Т(., относительный выигрыш - fTдГ . С Те

Формула изобретения Устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры и коммутатор, причем входыразрядов первого и второго ре- $ гистров подключены к информационным входам устройства, прямые выходы разрядов первбго регистра подключены к первой группе входов первого суммато. ра,инверсные выходы разрядов второго регистра подключены к второй группе входов, первого сумматора, прямой и инверсный выходы знакового разряда . которого подключены к управляющему входу коммутатора,отличающ е- е с J} тем, что, с целью повышения быстродействия устройства, в него введен третий сумматор, причем первая группа входов второго сумматора подключена к прямым выходам разрядов 20

первого регистра, (Vi-2) старших разрядов которого подключены к первой группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (-И-2) старших разрядов которого подключень) к второй группе входов второго сумматора, выходы разрядов второго и третьего сумматоров подключены к первой и второй группе информационных входов , коммутатора соответственно, выход которого подключен к выходу устройства.

Источники информации, . принятые во внимание при экспертизе 1. Авторское свидетельство СССР №623202, кл. G 06 F 7/38, 1976. 2. Авторское свидетельство СССР по заявке №2977566/18-2, кл. G 06F7/38, 1978 (прототип).

1001085

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 2016 |

|

RU2618188C1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1980 |

|

SU911516A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

5

Авторы

Даты

1983-02-28—Публикация

1981-10-12—Подача