(Л

ел

W

Изобретение относится к вычислительной Технике, в частности к оперативным запоми- Йающим устройствам, и может быть исполь- : овано при создании устройств со встроенной соррекцией ошибок.

Цель изобретения - повышение надеж- 1ости устройства.

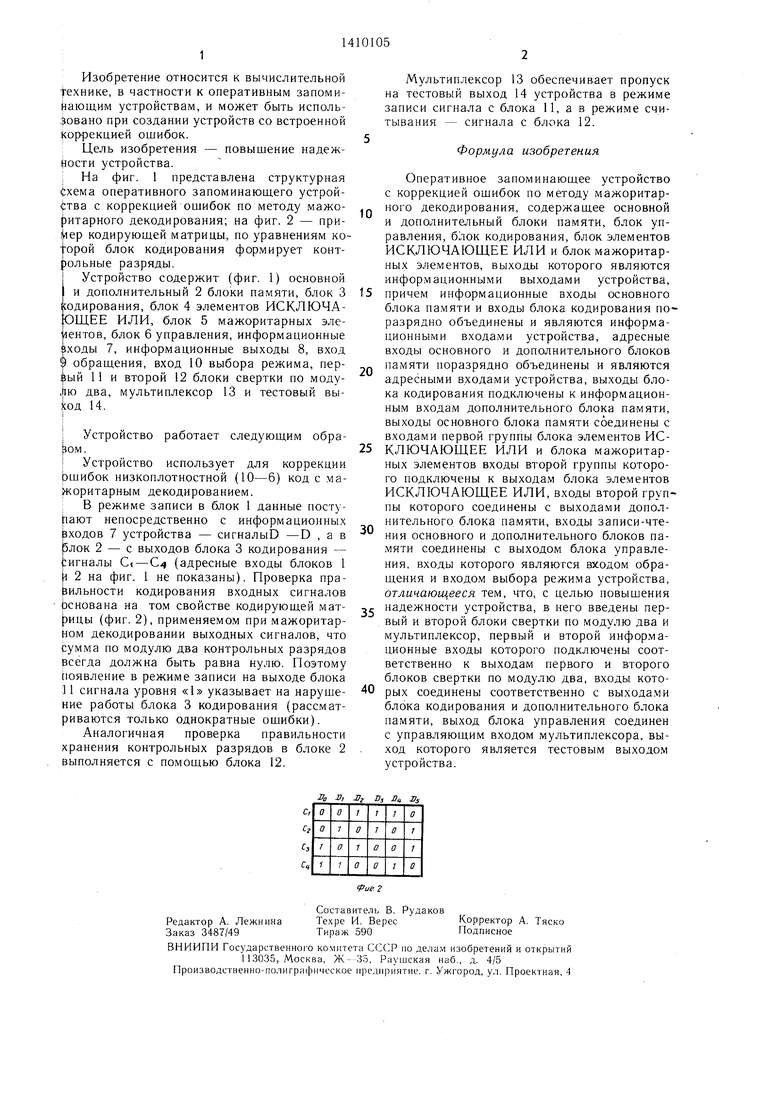

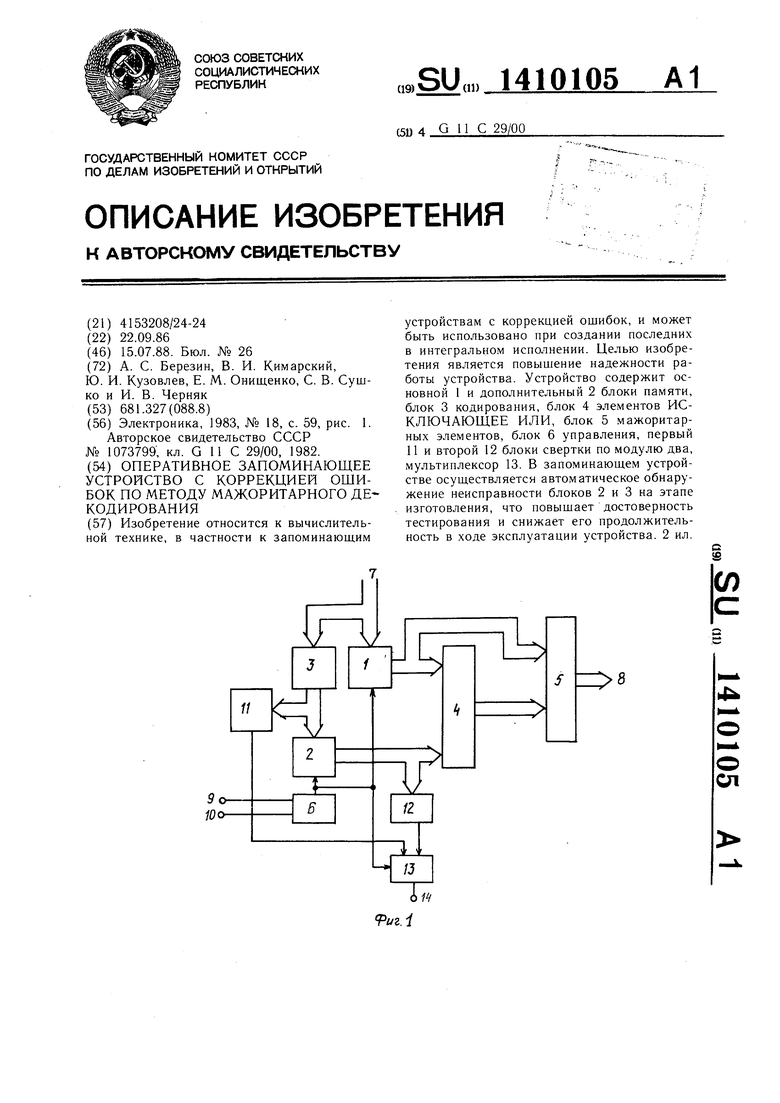

: На фиг. 1 представлена структурная ||;хема оперативного запоминаюшего устрой- фтва с коррекцией ошибок по методу мажо- |)итарного декодирования; на фиг. 2 - при- iiep кодирующей матрицы, по уравнениям ко- орой блок кодирования формирует конт- |)ольные разряды.

Устройство содержит (фиг. 1) основной и дополнительный 2 блоки памяти, блок 3 кодирования, блок 4 элементов ИСКЛЮЧА- ОЩЕЕ ИЛИ, блок 5 мажоритарных элементов, блок 6 управления, информационные кходы 7, информационные выходы 8, вход 9 обращения, вход 10 выбора режима, пер- 11 и второй 12 блоки свертки по моду- ,|iK) два, мультиплексор 13 и тестовый вы- .|сод 14.

I Устройство работает следуюшим обраfiOM.

IУстройство использует для коррекции Ьшибок низкоплотностной (10-6) код с ма- Н оритарным декодированием.

В режиме записи в блок 1 данные посту- чают непосредственно с информационных ЬХОДОБ 7 устройства - сигналыО -D , а в элок 2 - с выходов блока 3 кодирования - сигналы (адресные входы блоков 1 i 2 на фиг. 1 не показаны). Проверка пра- зильности кодирования входных сигналов Ьснована на том свойстве кодирующей мат- |зицы (фиг. 2), применяемом при мажоритарном декодировании выходных сигналов, что Сумма по модулю два контрольных разрядов всегда должна быть равна нулю. Поэтому юявление в режиме записи на выходе блока

I1сигнала уровня «1 указывает на нарушение работы блока 3 кодирования (рассматриваются только однократные ошибки).

Аналогичная проверка правильности хранения контрольных разрядов в блоке 2 выполняется с помощью блока 12.

5

0

5

0

5

0

Мультиплексор 13 обеспечивает пропуск на тестовый выход 14 устройства в режиме записи сигнала с блока 11, а в режиме считывания - сигнала с блока 12.

Формула изобретения

Оперативное запоминающее устройство с коррекцией ошибок по методу мажоритарного декодирования, содержаш.ее основной и дополните тьный блоки памяти, блок управления, блок кодирования, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и блок мажоритарных элементов, выходы которого являются информационными выходами устройства, причем информационн 5 е входы основного блока памяти и входы блока кодирования поразрядно объединены и являются информационными входами устройства, адресные входы основного и дополнительного блоков памяти поразрядно объединены и являются адресными входами устройства, выходы блока кодирования подключены к информационным входам дополнительного блока памяти, выходы основного блока памяти соединены с входами первой группы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и блока мажоритарных элементов входы второй группы которого подключены к выходам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы второй группы которого соединены с выходами дополнительного блока памяти, входы записи-чтения основного и дополнительного блоков памяти соединены с выходом блока управления, входы которого являются входом обращения и входом выбора режима устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены первый и второй блоки свертки по модулю два и мультиплексор, первый и второй информационные входы которого подключены соответственно к выходам первого и второго блоков свертки по модулю два, входы которых соединены соответственно с выхода.ми блока кодирования и дополнительного блока памяти, выход блока управления соединен с управляющим входом мультиплексора, выход которого является тестовым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1377917A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Динамическое запоминающее устройство с автономным контролем | 1984 |

|

SU1290418A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1392595A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1251188A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с коррекцией ошибок, и может быть использовано при создании последних в интегральном исполнении. Целью изобретения является повышение надежности работы устройства. Устройство содержит основной 1 и дополнительный 2 блоки памяти, блок 3 кодирования, блок 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 5 мажоритарных элементов, блок 6 управления, первый 11 и второй 12 блоки свертки по модулю два, мультиплексор 13. В запоминающем устройстве осуш.ествляется автоматическое обнаружение неисправности блоков 2 и 3 на этапе изготовления, что повышает достоверность тестирования и снижает его продолжительность в ходе эксплуатации устройства. 2 ил. с

| Электроника, 1983, № 18, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-15—Публикация

1986-09-22—Подача