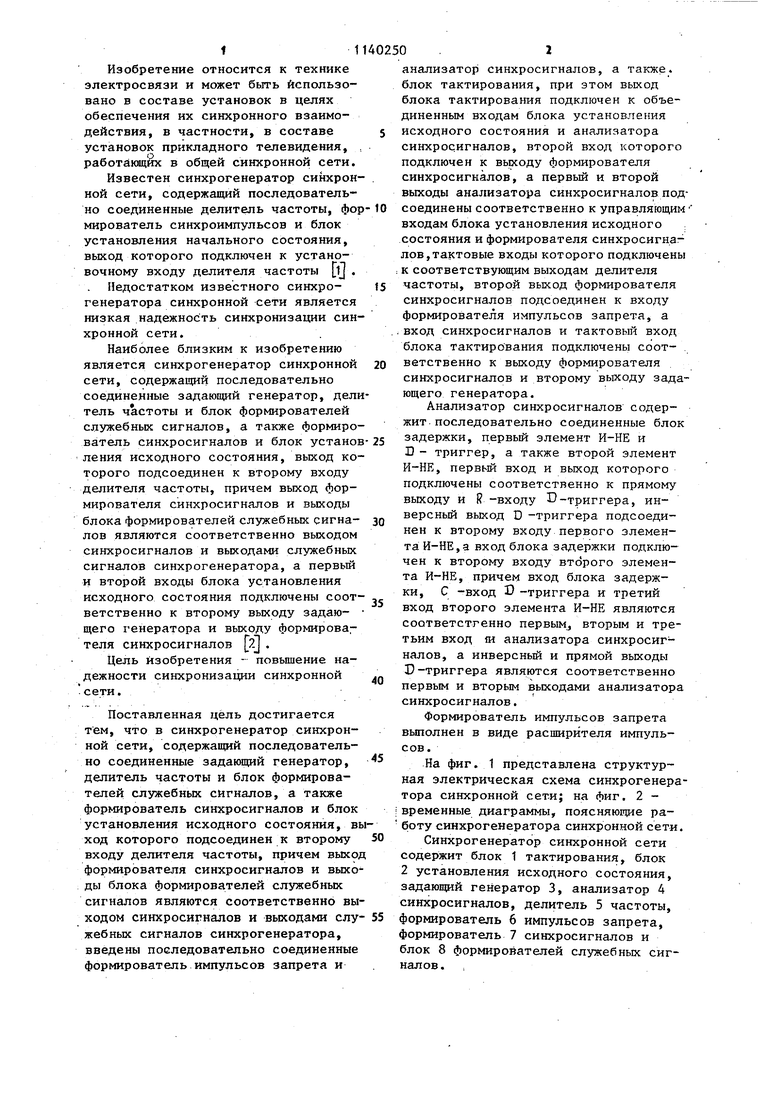

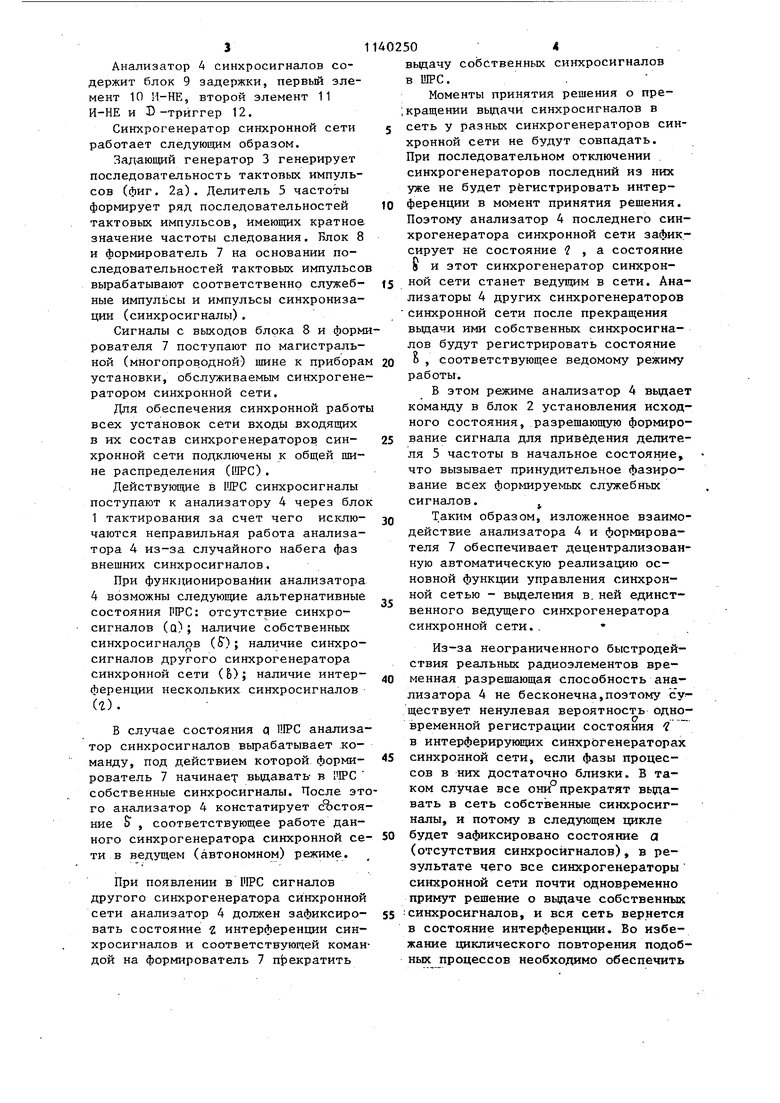

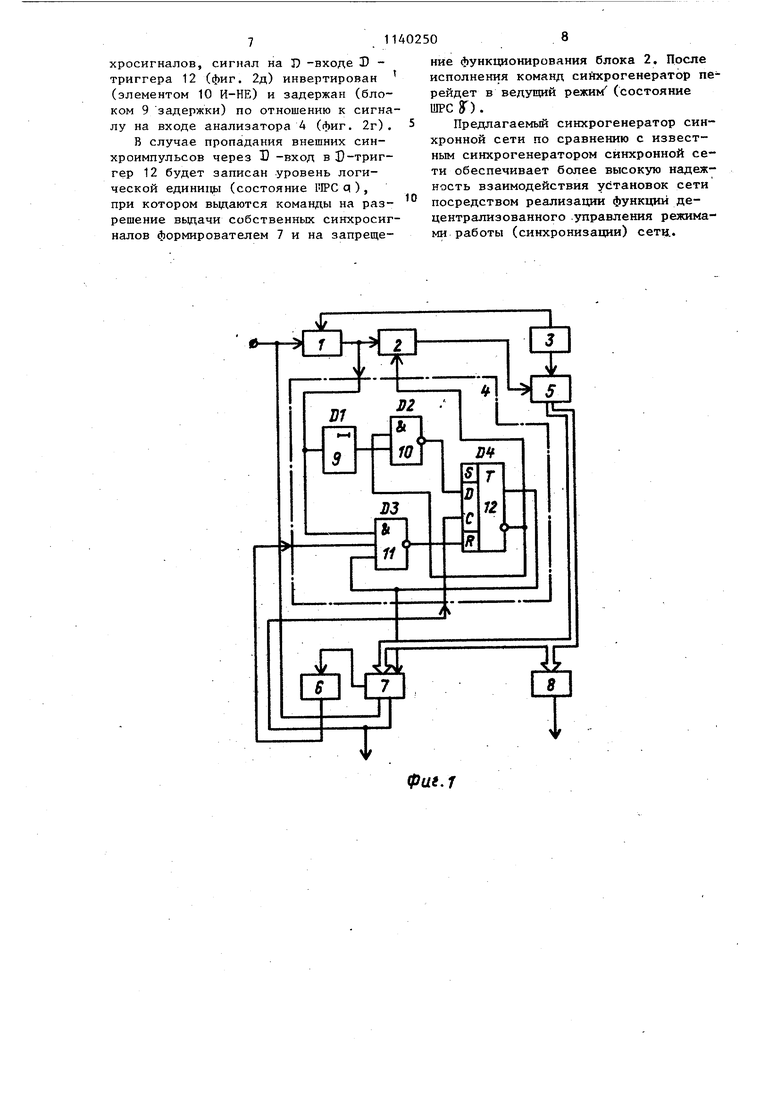

11 Изобретение относится к технике электросвязи и может быть использовано в составе установок в целях обеспечения их синхронного взаимодействия, в частности, в составе установок прикладного телевидения, работающих в общей синхронной сети. Известен синхрогенератор синхронной сети, содержащий последовательно соединенные делитель частоты, фор мирователь синхроимпульсов и блок установления начального состояния, выход которого подключен к установочному входу делителя частоты ij . Недостатком известного синхрогенератора синхронной сети является низкая надежность синхронизации синхронной сети. Наиболее близким к изобретению является синхрогенератор синхронной сети, содержащий последовательно соединенные задающий генератор, дели тель частоты и блок формирователей служебньк сигналов, а также формирователь синхросигналов и блок уставов ления исходного состояния, выход которого подсоединен к второму входу делителя частоты, причем выход формирователя синхросигналов и выходы блока формирователей служебных сигналов являются соответственно выходом синхросигналов и выходами служебных сигналов синхрогенератора, а первый и второй входы блока установления исходного состояния подключены соответственно к второму выходу задающего генератора и выходу формировав теля синхросигналов 2j . Цель Изобретения - повышение надежности синхронизации синхронной сети. Поставленная цель достигается ной сети, содержащий последовательно соединенные задающий генератор, делитель частоты и блок формирователей служебных сигналов, а также формирователь синхросигналов и блок установления исходного состояния, в ход которого подсоединен к второму входу делителя частоты, причем выхо формирователя синхросигналов и выхо ды блока формирователей служебных сигналов являются соответственно вы ходом синхросигналов и выходами слу жебных сигналов синхрогенератора, введены последовательно соединенные формирователь импульсов запрета и 0 анализатор синхросигналов, а также. блок тактирования, при этом выход блока тактирования подключен к объединенным входам блока установления исходного состояния и анализатора синхросигналов, второй вход которого подключен к вькоду формирователя синхросигналов, а первый и второй выходы анализатора синхросигналов подсоединены соответственно к управляющим входам блока установления исходного состояния и формирователя синхросигналов, тактовые входы которого подключены к соответствующим выходам делителя частоты, второй выход формирователя синхросигналов подсоединен к входу формирователя импульсов запрета, а вход синхросигналов и тактовый вход блока тактирования подключены соответственно к выходу формирователя синхросигналов и второму вькоду задающего генератора. Анализатор синхросигналов содержит последовательно соединенные блок задержки, первый элемент И-НЕ и D - триггер, а также второй элемент И-НЕ, первый вход и выход которого подключены соответственно к прямому выходу и R -входу С-триггера, инверсный выход D -триггера подсоединен к второму входу первого элемента И-НЕ,а вход блока задержки подключен к второму входу второго элемента И-НЕ, причем вход блока задержки, С -вход О -триггера и третий вход второго элемента И-НЕ являются соответстгенно первым, вторым и третьим вход ш анализатора синхросигналов, а инверсный и прямой выходы 35-триггера являются соответственно первым и вторым выходами анализатора синхросигналов. Формирователь импульсов запрета выполнен в виде расширителя импульсов. На фиг. 1 представлена структурная электрическая схема синхрогенератора синхронной сети; на фиг. 2 временные диаграммы, поясняющие работу синхрогенератора синхронной сети. Синхрогенератор синхронной сети содержит блок 1 тактирования, блок 2 установления исходного состояния, задающий генератор 3, анализатор 4 синхросигналов, делитель 5 частоты. формирователь 6 импульсов запрета. формирователь 7 синхросигналов и блок 8 формирователей служебных сигналов. Анализатор 4 синхросигналов содержит блок 9 задержки, первьй элемент 10 И-НЕ, второй элемент 11 И-НЕ и D -триггер 12. Сишсрогенератор синхронной сети работает следующим образом. Задающий генератор 3 генерирует последовательность тактовых импульсов (фиг. 2а). Делитель 5 частоты формирует ряд последовательностей тактовых импульсов, имеющих кратное значение частоты следования. Блок 8 и формирователь 7 на основании последовательностей тактовых импульсо вырабатывают соответственно служебные импульсы и импульсы синхронизации (синхросигналы). Сигналы с выходов блока 8 и форм рователя 7 поступают по магистральной (многопроводной) шине к прибора установки, обслуживаемым синхрогене ратором синхронной сети. Для обеспечения синхронной работ всех установок сети входы входящих в их состав синхрогенераторов синхронной сети подключены к общей шине распределения (1РС) . Действующие в UJPC синхросигналы поступают к анализатору 4 через бло 1 тактирования за счет чего исключаются неправильная работа анализатора 4 из-за случайного набега фаз внешних синхросигналов. При функционировании анализатора 4 возможны следующие альтернативные состояния 1ЧРС: отсутствие синхросигналов (Q); наличие собственных синхросигналов (S); наличие синхросигналов другого синхрогенератора синхронной сети (6); наличие интерференции нескольких синхросигналов в случае состояния q IlPC анализа тор синхросигналов вырабатывает .команду, под действием которой формирователь 7 начинает вьщавать- в IlPC собственные синхросигналы. После эт го анализатор 4 констатирует сЪстоя ние , соответствующее работе данного синхрогенератора синхронной се ти в ведущем (автономном) режиме. При появлении в ИРС сигналов другого синхрогенератора синхронной сети анализатор 4 должен зафиксировать состояние 1 интерференции синхросигналов и соответствующей коман дой на формирователь 7 прекратить выдачу собственных синхросигналов в ШРС. Моменты принятия решения о прекращении выдачи синхросигналов в сеть у разных синхрогенераторов синхронной сети не будут совпадать. При последовательном отключении синхрогенераторов последний из них уже не будет регистрировать интерференции в момент принятия решения. Поэтому анализатор 4 последнего син- хрогенератора синхронной сети зафиксирует не состояние 1 , а состояние 8 и этот синхрогенератор синхронной сети станет ведущим в сети. Анализаторы 4 других синхрогенераторов синхронной сети после прекращения вьщачи ими собственных синхросигналов будут регистрировать состояние S , соответствующее ведомому режиму работы. В этом режиме анализатор 4 выдает команду в блок 2 установления исходного состояния, разрешающую формирование сигнапа для приведения делителя 5 частоты в начальное состояние, что вызывает принудительное фазирование всех формируемых служебных сигналов. Таким образом, изложенное взаимодействие анализатора 4 и формирователя 7 обеспечивает децентрализованную автоматическую реализацию основной функции управления синхронной сетью - вьщеления в. ней единственного ведущего синхрогенератора синхронной сети.. Из-за неограниченного быстродействия реальных радиоэлементов временная разрешающая способность анализатора 4 не бесконечна,поэтому ществует ненулевая вероятность одновременной регистрации состояния в интерферирукнцих синхрогенераторах синхронной сети, если фазы процессов в них достаточно близки. В таком случае все они°прекратят вьщавать в сеть собственные синхросигналы, и потому в следующем цикле будет зафиксировано состояние а (отсутствия синхросигналов), в результате чего все синхрогенераторы синхронной сети почти одновременно примут решение о вьщаче собственных синхросигналов, и вся сеть вернется в состояние интерференции. Во избежание циклического повторения подобных процессов необходимо обеспечить

различие условий регистрации чужих синхросигналов при их мапьйс фазовых отличиях от собственных синхросигналов .

Причиной такого различия является естественньй набег фаз в несвязаниых между собой задающих генераторах 3, Пока разность фаз не превьшает периода тактовой частоты, состояние сети неотличимо от синхронного. Но когда набег фаз превысит длительность периода тактовой частотЫj нельзя допускать одновременной регистрации состояния 1 во всех взаимодействующих синхрогенераторах синхронной сети, иначе проиесс перебора состояний не прекратится.

Для этого необходимо заблокировать действие анализатора 4 на несколько тактов либо до начала переда- 20

чи собственного синхросигнала, либо сразу же после его окончания.

Для блокировки анализа интерференции в синхрогенератор синхронной сети введен формирователь 6 импуль- 25 сов запрета, выход которого соединен с третьим входом анализатора 4. Так как интервал блокировки анализа установлен после окончания синхроимпульса, то при формировании им- 30 пульсов запрета используется расширение синхросигналов, для чего вход формирователя 6 подключен к делителю 5 частоты через формирователь 7,.

Для обеспечения возможности иден- 35 тичного подключения всех синхрогенераторов синхронной сети к L4PC формирователи 7 (выходы которых при этом объединены) должны быть реализованы по схеме с открытым выходом, кото- 40 рый через резистор подсоединен- к источнику питания.

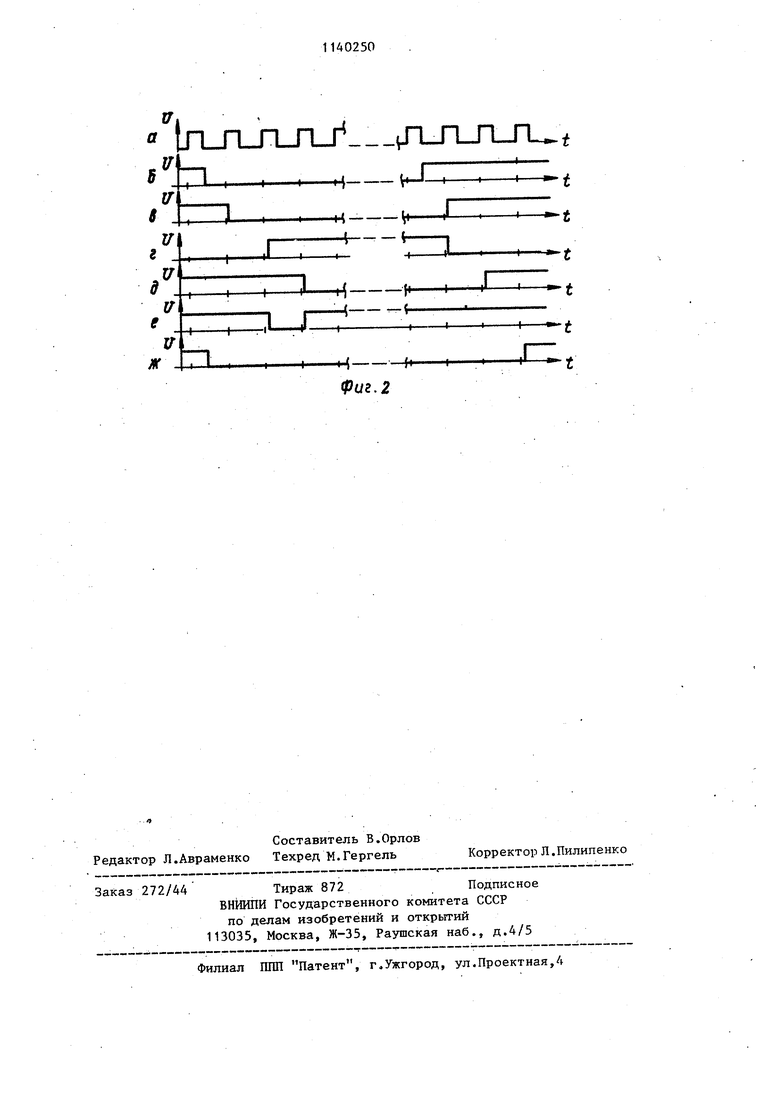

Анализатор 4 содержит D.-триггер 12, состояние которого определяет ведущий (лог.1) или ведомый (.0) режим работы синхрогенератора синхронной сети. На С -вход Б -триггера 12 поступают синхросигна-. лы с формирователя 7. На фиг. 26 показаны начальный и конечный участки 50 этого синхросигнала. Фронты синхросигнала должны соответствовать середине интервала между моментами тактирования в блоке 1 тактирования, поскольку при этом достигается ну- 55 левое математическое ожидание погрешности синхронизации. На выходе блока 1 тактирования сигнал синхронизации

оказьшается привязанным к моментам тактирования и приобретает вид, например, показанный на фиг, 2г,

В ведущем режиме (состояние ШРС 5)

элемент 10 И-НЕ закрыт подачей уровня логического нуля на второй вход, так что в момент воздействия по С -входу 3)-триггер 12 перезаписывает с II входа уровень логической единицы. Изменение состояния D -триггера 12

может произойти только по R-входу при срабатывании элемента 11 И-НЕ, на третий вход которого подан разрешающий сигнал с прямого выхода Б -триггера 12. На второй вход элемента 11 И-НЕ подан импульс запрета с формирователя 6, показанный на фиг. 2ж. Его перекрытие во времени с собственным синхросигналом (фиг.26)

тер взаимодействия собственных сицхросигналов с внешними Не позволяет определить наличие последних во время поддержания уровня логического Нуля формирователем 7.

Таким образом, изменение состояния -D -триггера 12 возможно только при поступлении зфовня логической единицы на первый вход элемента И-НЕ 11 вне интервала действия импульсов запрета (фиг.2ж), т.е. при появлении в lUPC интерферирующего синхросигнала другого синхрогенератора синхроннойсети (состояние ШРС 2 ) .В таком случае в Б -триггер 12 будет установлено состояние логического нуля, при котором анализатор 4 вьщает команду запрета вьдачй собственных синхросигналов на формирователь 7 и команду разрешения на блок 2 установления исходного состояния, открывающую следование импульсов установления начального состояния (фиг. 2е) на делитель частоты 5.

После испэлнения команд синхрогенератор синхронной сети перейдет в ведомый режим. D -триггер 12 в момент окончания собственного синхросигнала (фиг. 26) будет фиксировать уровень логического нуля по D -входу, свидетельствующий о наличии синхросигналов другого синхрогенератора синхронной сети (состояние Ь). Для обеспечения устойчивого поддержания ведомого режима при случайных отклонениях частот тактовых импульсов и при наличии искажений формы распространяемых по сети синдопустимо, так как нелинейный харакхросигналов, сигнал на Т) -входе D триггера 12 (фиг. 2д) инвертирован (элементом 10 И-НЕ) и задержан (блоком 9 задержки) по отношению к сигналу на входе анализатора 4 (фиг. 2г). В случае пропадания внешних синхроимпульсов через D -вход в D-триггер 12 будет записан уровень логической едини1 ;ы (состояние UIPC q ) , при котором выдаются команды на разрешение выдачи собственных синхросигналов формирователем 7 и на запрещение функционирования блока 2, После исполнения команд синхрогенератор перейдет в ведущий (состояние ШРС У) .

Предлагаемьй синхрогенератор синхронной сети по сравнению с известным синхрогенератором синхронной сети обеспечивает более высокую надежность взаимодействия установок сети посредством реализации функций децентрализованного управления режимами работы (синхронизации) сети..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления режимом работы синхрогенератора | 1985 |

|

SU1322504A1 |

| Синхрогенератор | 1987 |

|

SU1555908A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Синхрогенератор | 1985 |

|

SU1252971A1 |

| Ведомый телевизионный синхрогенератор | 1987 |

|

SU1598208A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

1. СИНХРОГЕНЕРАТОР СИНХРОННОЙ СЕТИ, содержащий последовательно соединенные задающий генератор, делитель частоты и блок формирователей служебных сигналов, а также формирователь синхросигналов и блок установления исходного состояния, выход которого подсоединен к второму входу дeлитeJIя частоты, причем выход формирователя синхросигналов и выходы блока формирователей служебных сигналов являются соответственно выходом синхросигналов и выходами служебных сигналов синхрогенератора, о т л и ч а о щ и и с я тем, что-, с целью повышения надежности синхронизации синхронной сети, введены последовательно соединенные формирователь импульсов запрета и анализатор синхросигналов, а также блок тактирования, при этом выход блока тактирования подключен к объединенным входам блока установления исходного состояния и анализатора синхросигналов, второй вход которого подключен к выходу формирователя синхросигналов, а первьй и второй выходы анализатора синхросигналов подсо единены соответственно к управляющим входам блока установления исходного состояния и формирователя синхросигналов, тактовые входы которого подключены к соответствующим выкодам делителя частоты, второй выход формирователя синхросигналов подсоединен к входу формирователя импульсов запрета, а вход синхросигналов и тактовый вход блока тактирования подключены соответственно к выходу формирователя синхросигналов и второму выходу задающего генератора. 2. Синхрогенератор по п.1, отличающийся тем, что анализатор синхросигналов содержит последовательно соединенные блок за(Л держки, первый элемент И-НБ и D триггер, а также второй элемент И-НЕ, первый вход и выход которого подключены соответственно к прямому вькоду и R -входу ID -триггера,-NHH- . версный выход D -триггера подсоединен к второму входу первого элемецта И-НЕ, а вход блока задержки подключен к второму входу второго элемента И-НЕ, причем вход блока дадержки, С -вход D -триггера и третий вход второго элемента И-НЕ являются соответственно первым, вторым и третьим входами анализатора синхросигналов, а инверсный и прямой выходы ; D -триггера являются соответственно первым и вторим выходами анализатора синхросигналов. 3, Синхрогенератор по п.1, о т личающийся тем, что формирователь импульсов запрета выполнен в виде расширителя импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-02-15—Публикация

1983-06-29—Подача