(54) УСТЮЙСТВО СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Приемник синхросигнала | 1981 |

|

SU1092745A1 |

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Устройство цикловой синхронизации | 1980 |

|

SU1341727A2 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

1

Изобретение относится к связи и может быть использовано в системах передачи дискретных сообщений для обеспечения тактовой и цикловой синхронизации.

Известен приемник синхросигнала, который содержит опознаватель синхросигнала, накопители по входу и выходу из синхронизма, кодовый разделитель, генераторное оборудование, выделитель тактовой частоты, два элемента И и злемент НЕТ 1.

Недостатками данного устройства являются низкие помехоустойчивость и быстродействие.

Наиболее близким к предлагаемому по технической сущности и достигаемому зффекту является устройство синхронизации приемной станции, содержащее последовательно соединенные формирователь тактовых импульсов, регистрирующий блок, выделитель синхросигнала, блок защиты, блок установки распределителя и распределитель, первый вход которого подключен к другому входу выделителя синхросигнала, второй выход - к другому входу блока установки распределителя, а к другому,

входу распределителя подключен выход формирователя тактовых импульсов, причем сигнальный вход регистрирующего блока является входом устройства 2.

Недостатками данного устройства являются низкие помехоустойчивость и быстродействие.

Цель изобретения - повьпление помехоустойчивости.

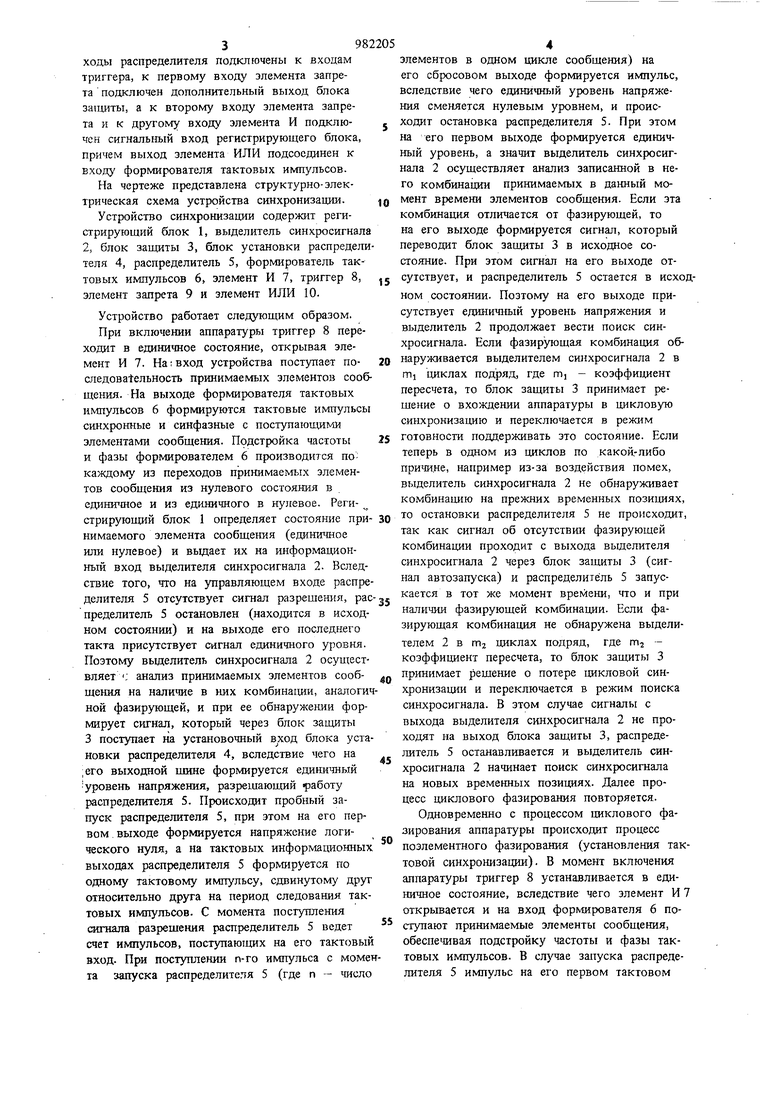

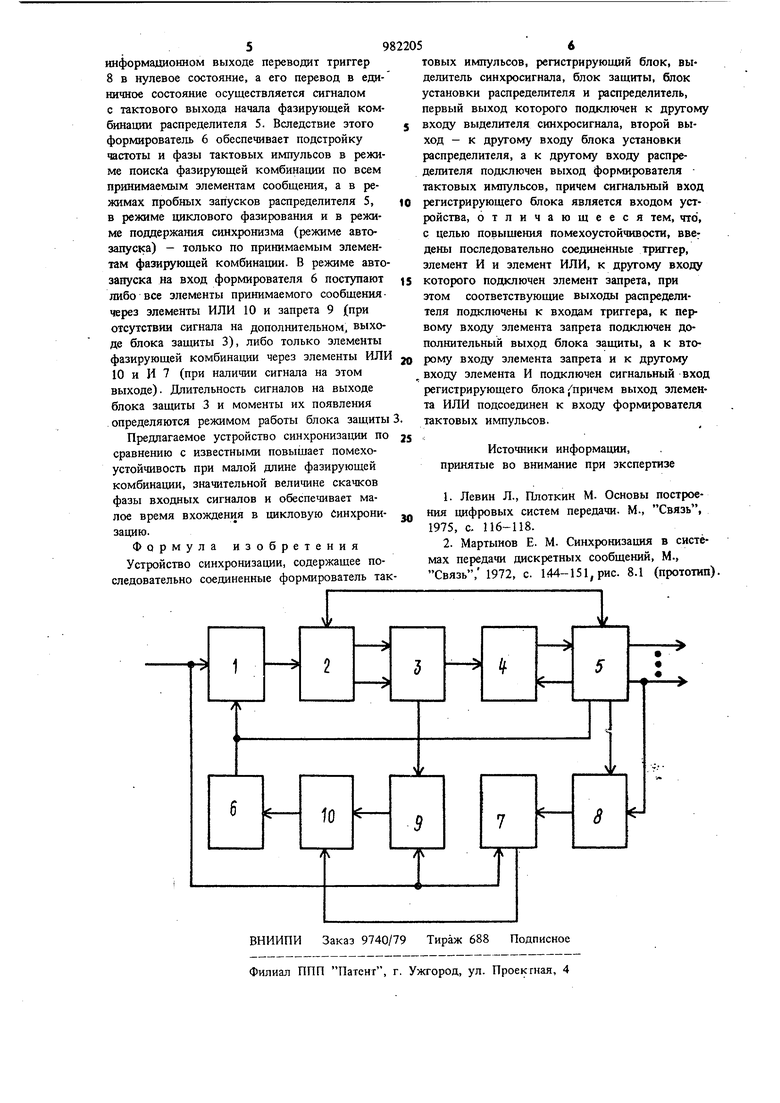

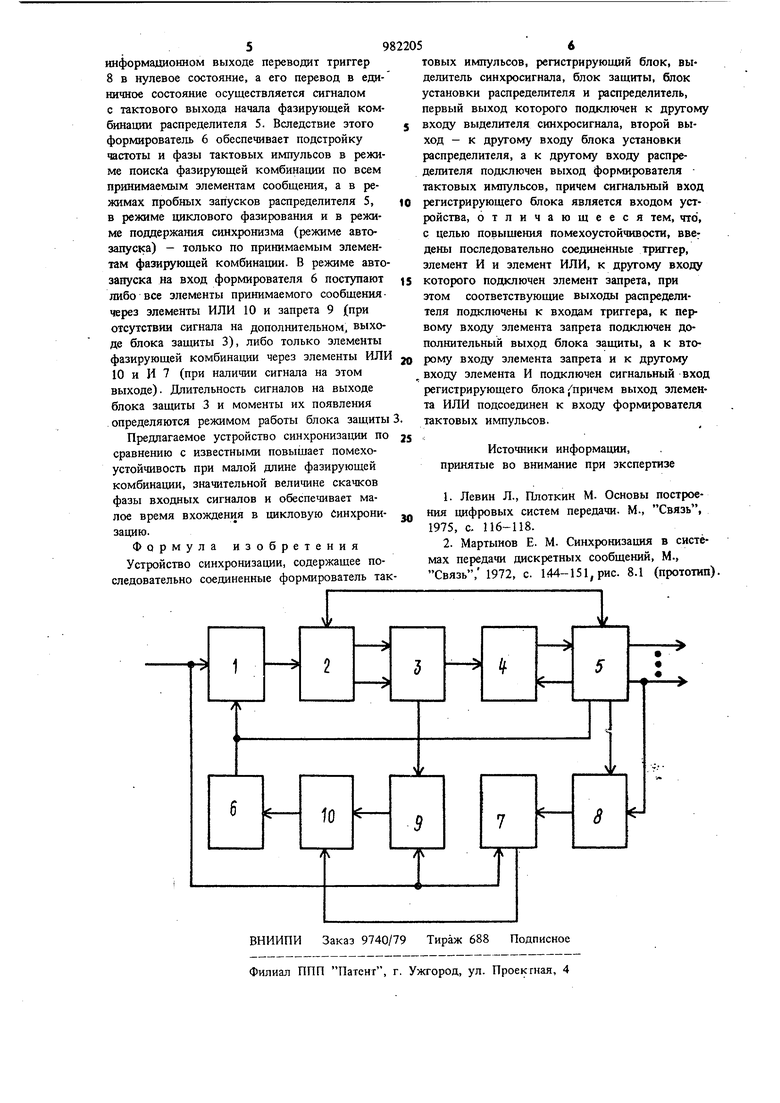

Для зтого в устройство синхронизации, содержащее последовательно соединенные форми10рователь тактовых импульсов, регистрирующий блок, выделитель синхросигнала, блок защиты, блок установки распределителя и распредели- . тель, первый выход которого подключен к другому входу выделителя синхросигнала, вто15рой выход - к другому входу блока установки распределителя, а к другому входу распределителя подключен выход формирователя тактовых импульсов, причем сигнальный вход регистрирующего блока является вхо20дом устройства, введены последовательно соединенные триггер, элемент И и элемент ИЛИ, к другому входу которого подключен элемент запрета, при этом соответствующие вы398ходы распределителя подключены к входам триггера, к первому входу элемента запрета подключен дополнительный выход блока защиты, а к второму входу элемента залрета и к другому входу элемента И подключей сигнальный вход регистрирующего блока, причем выход элемента ИЛИ подсоединен к входу формирователя тактовых импульсов. На чертеже представлена структурно-электрическая схема устройства синхронизации. Устройство синхронизации содержит регистрирующий блок 1, выделитель синхросигнала 2, блок защиты 3, блок установки распредели теля 4, распределитель 5, формирователь тактовых импульсов 6, элемент И 7, триггер 8, элемент запрета 9 и элемент ИЛИ 10. Устройство работает следующим образом. При включении аппаратуры триггер 8 переходит в единичное состояние, открывая элемент И 7. На; вход устройства поступает последова1ельность принимаемых элементов сооб щения. На выходе формирователя тактовых импульсов 6 формируются тактовые импульсы синхронные и синфазные с поступающими элементами сообщения. Подстройка частоть и фазы формирователем 6 производится покаждому из переходов принимаемых элементов сообщения из нулевого состояния в едишгшое и из единичного в нулевое. Реги- стрирующий блок 1 определяет состояние принимаемого элемента сообщения (единичное шш нулевое) и вьщает их на информационный вход выделителя синхросигнала 2. Вследствие того, что на управляющем входе распре делителя 5 отсутствует сигнал разрешения, pac пределитель 5 остановлен (находится в исходном состоянии) и на выходе его последнего такта присутствует сигнал единичного уровня. Поэтому вьщелитель синхросигнала 2 осуществляет ; анализ принимаемых элементов сообщения на наличие в них комбинагщи, аналогич ной фазирующей, и при ее обнаружении формирует сигнал, который через блок защиты 3 поступает на установочный блока уста новки распределителя 4, вследствие чего на ;его выходной шине формируется единичный уровень напряжения, разрешающий работу распределителя 5. Происходит пробный запуск распределителя 5, при этом на его первом выходе формируется напряжение логического нуля, а на тактовых информационных выходах распределителя 5 формируется по одному тактовому импульсу, сдвинутому друг относительно друга на период следования тактовых импульсов. С момента поступления сигнала разрешения распределитель 5 ведет счет импульсов, поступаютцих на его тактовый вход. При поступлении п-го импульса с момен та запуска распределителя 5 (где п - число элементов в одном цикле сообщения) на его сбросовом выходе формируется импульс, вследствие чего единичный уровень напряжения сменяется нулевым уровнем, и происходит остановка распределителя 5. При этом на его первом выходе формируется единичный уровень, а значит выделитель синхросигнала 2 осуществляет анализ записанной в него комбинации принимаемых в данный момент времени элементов сообщения. Если эта комбинация отличается от фазирующей, то на его выходе формируется сигнал, который переводит блок защиты 3 в исходное состояние. При этом сигнал на его выходе отсутствует, и распределитель 5 остается в исходном состоянии. Поэтому на его выходе присутствует единичный уровень напряжения и выделитель 2 продолжает вести поиск синхросигнала. Если фазирующая комбинация обнаруживается вьщелителем синхросигнала 2 в mi циклах подряд, где Ш - коэффициент пересчета, то блок защиты 3 принимает рещение о вхождении аппаратуры в цикловую синхронизацию и переключается в режим готовности поддерживать это состояние. Если теперь в одном из циклов по какой-либо причине, например из-за воздействия помех, вьщелитель синхросигнала 2 не обнаруживает комбинацию на прежних временных позициях, то остановки распределителя 5 не происходит, так как сигнал об отсутствии фазирующей комбинации проходит с выхода вьщелителя синхросигнала 2 через блок защиты 3 (сигнал автозапуска) и распределитель 5 запускается в тот же момент времени, что и при наличии фазирующей комбинации. Если фазирующая комбинация не обнаружена выделителем 2 в т2 циклах подряд, где т - коэффициент пересчета, то блок защиты 3 принимает рещение о потере цикловой синхронизации и переключается в режим поиска синхросигнала. В этом случае сигналы с выхода выделителя синхросигнала 2 не проходят на выход блока защиты 3, распределитель 5 останавливается и выделитель синхросигнала 2 начинает поиск синхросигнала на новых временных позициях. Далее процесс циклового фазирования повторяется. Одновременно с процессом циклового фазирования аппаратуры происходит процесс поэлементного фазирования (установления тактовой синхронизации). В момент включения аппаратуры триггер 8 устанавливается в единичное состояние, вследствие чего элемент И 7 открывается и на вход формирователя 6 поступают принимаемые элементы сообщения, обеспечивая подстройку частоты и фазы тактовых импульсов. В случае запуска распределителя 5 импульс на его первом тактовом 59 информаххионном выходе переводит триггер 8 в нулевое состояние, а его перевод в единичное состояние осуществляется сигналом с тактового выхода начала фазирующей комбинации распределителя 5. Вследствие этого формирователь 6 обеспечивает подстройку частоты и фазы тактовых импульсов в режиме поиска фазирующей комбинации по всем принимаемым элементам сообщения, а в режимах пробных запусков распределителя 5, в режиме циклового фазирования и в режиме поддержания синхронизма (режиме автозапуска) - только по принимаемым элементам фазирующей комбинации. В режиме авто запуска на вход формирователя 6 поступают либо все элементы принимаемого сообщениячерез элементы ИЛИ 10 и запрета 9 (при отсутствии сигнала на дополнительном, выходе блока защиты 3), либо только элементы фазирующей комбинации через элементы ИЛИ 10 и И 7 (при наличии сигнала на этом выходе). Длительность сигналов на выходе блока защиты 3 и моменты их появления определяются режимом работы блока защиты Предлагаемое устройство синхронизации по сравнению с известными повыщает помехоустойчивость при малой длине фазирующей комбинации, значительной величине скачков фазы входных сигналов и обеспечивает малое время вхождения в цикловую Синхронизацию. Формула изобретения Устройство синхронизации, содержащее последовательно соединенные формирователь так товых импульсов, регистрирующий блок, выделитель синхросигнала, блок защиты, блок установки распределителя и распределитель, первый выход которого подключен к другому входу выделителя синхросигнала, второй выход - к другому входу блока установки распределителя, а к другому входу распределителя подключен выход формирователя тактовых импульсов, причем сигнальный вход регистрирующего блока является входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, вне: дены последовательно соединенные триггер, элемент И и элемент ИЛИ, к другому входу которого подключен элемент запрета, при этом соответствующие выходы распределителя подключены к входам триггера, к первому входу элемента запрета подключен дополнительный выход блока защиты, а к второму входу элемента запрета и к другому входу элемента И подключен сигнальный вход регистрирующего блока /причем выход элемента ИЛИ подсоединен к входу формирователя тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1.Левин Л., Плоткин М. Основы построения цифровых систем передачи. М., Связь, 1975, с, 116-118. 2.Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений, М., Связь, 1972, с. 144-151, рис. 8.1 (прототип).

Авторы

Даты

1982-12-15—Публикация

1980-07-25—Подача