Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах с микропрограммным управлением.

Целью изобретения является повышение быстродействия.

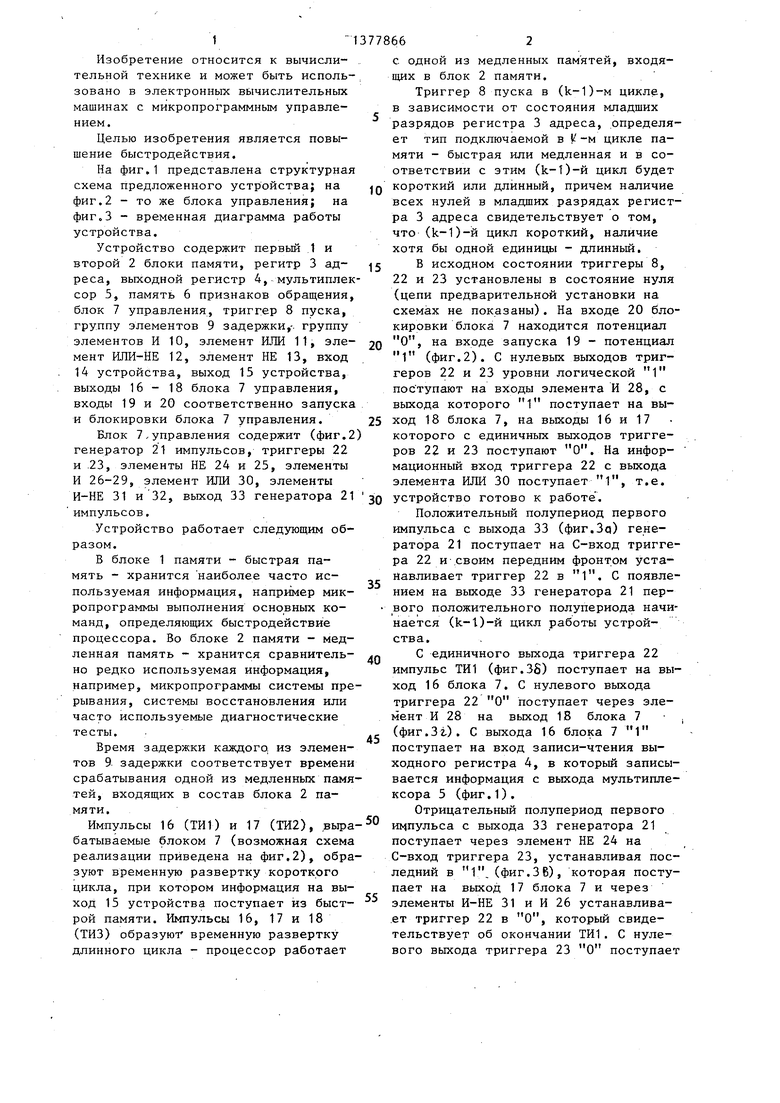

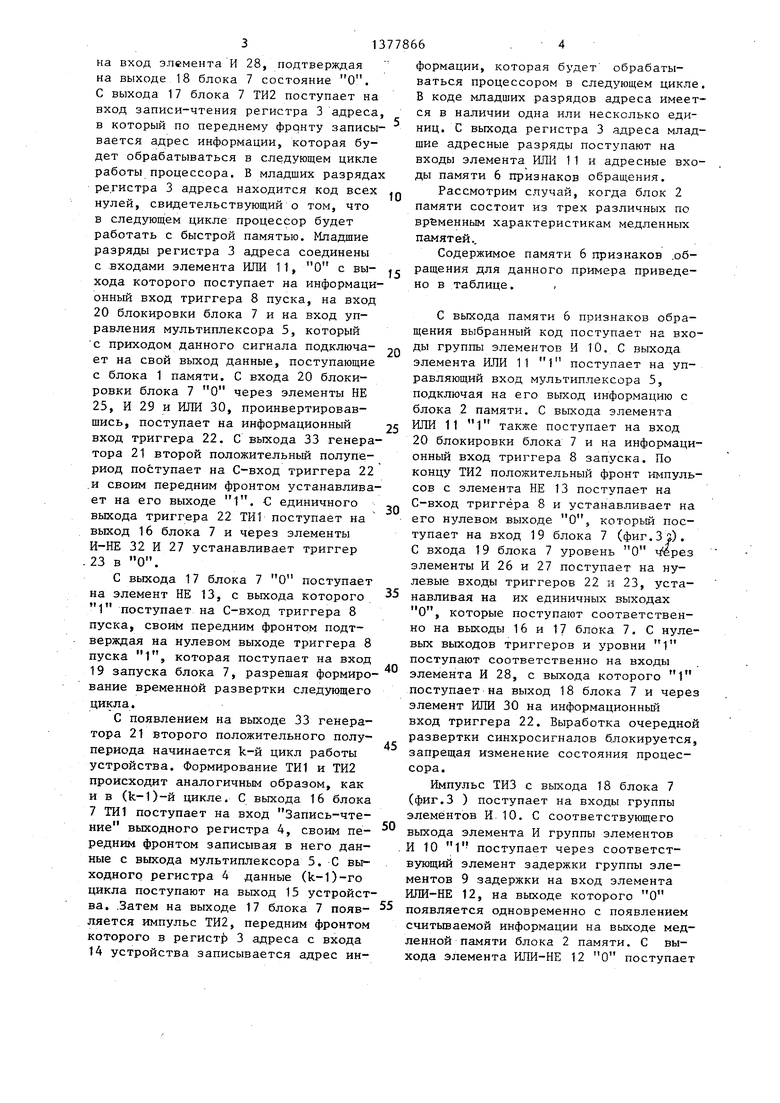

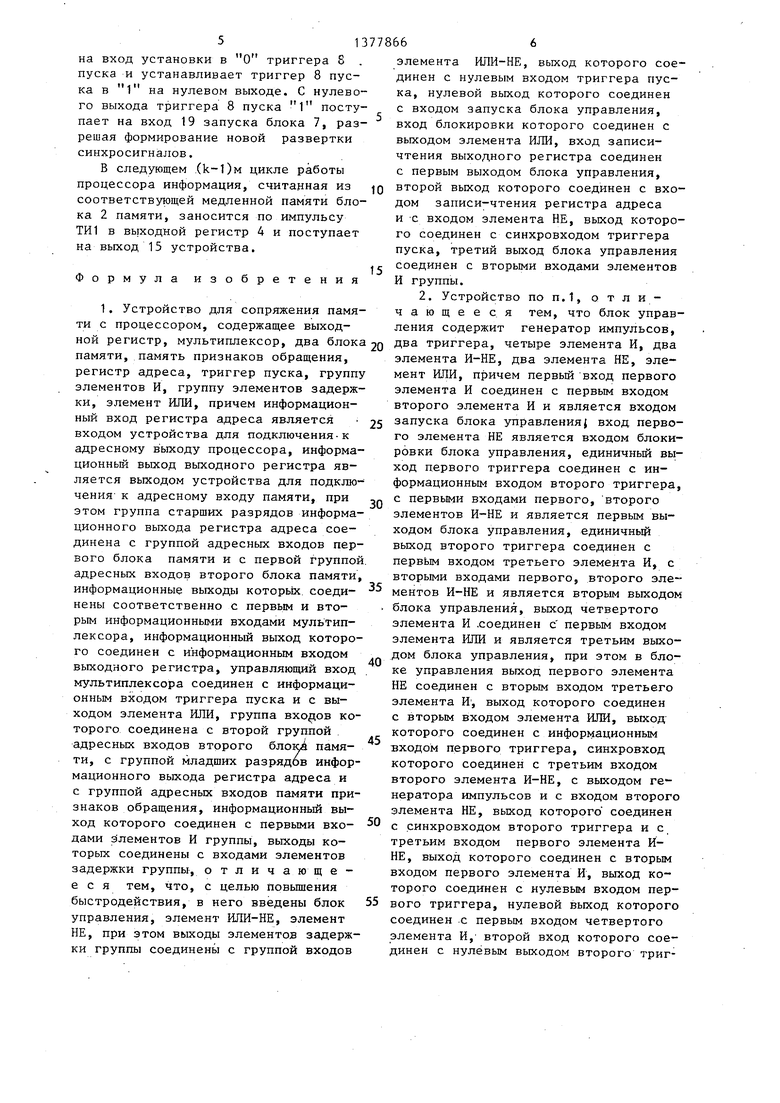

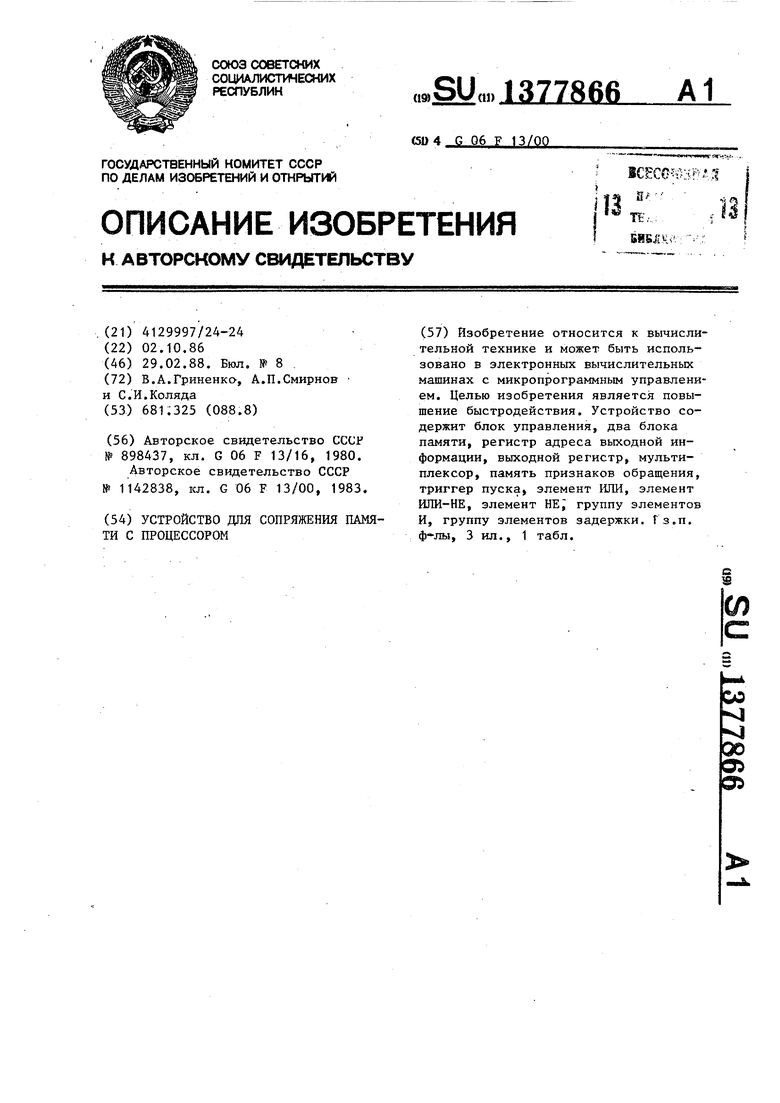

На фиг.1 представлена структурная схема предложенного устройства; на фиг.2 - то же блока управления; на фиг.З - временная диаграмма работы устройства.

Устройство содержит первый 1 и второй 2 блоки памяти, регитр 3 адреса, выходной регистр 4, мультиплексор 5, память 6 признаков обращения, блок 7 управления, триггер 8 пуска, группу элементов 9 задержки,-, группу элементов И 10, элемент ИЛИ 11, элемент ИЛИ-НЕ 12, элемент НЕ 13, вход 14 устройства, выход 15 устройства, выходы 16 - 18 блока 7 управления, входы 19 и 20 соответственно запуска и блокировки блока 7 управления.

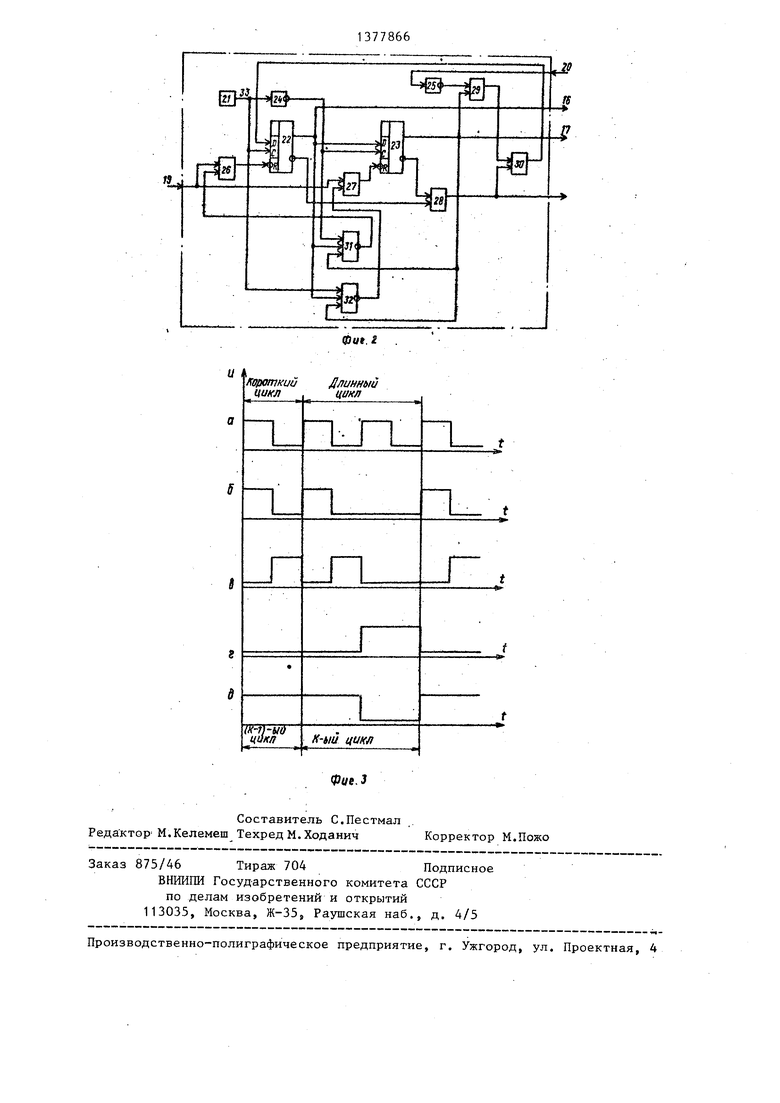

Блок 7 ,у правления содержит (фиг.2) генератор 21 импульсов, триггеры 22 и 23, элементы НЕ 24 и 25, элементы И 26-29, элемент ИЛИ 30, элементы И-НЕ 31 и 32, выход 33 генератора 21 импульсов.

Устройство работает следующим образом.

В блоке 1 памяти - быстрая память - хранится наиболее часто используемая информация, например микропрограммы выполнения основных команд, определяющих быстродействие процессора. Во блоке 2 памяти - медленная память - хранится сравнительно редко используемая информация, например, микропрограммы системы прерывания, системы восстановления или часто используемые диагностические тесты.

Время задержки каждого, из элементов 9 задержки соответствует времени срабатывания одной из медленных памятей, входящих в состав блока 2 памяти.

10

15

20

25

30

35

40

45

с одной из медленных памятей, вход щих в блок 2 памяти.

Триггер 8 пуска в (k-l)-M цикле в зависимости от состояния младших разрядов регистра 3 адреса, опреде ет тип подключаемой в К-м цикле п мяти - быстрая или медленная и в с ответствии с этим (К-1)-й цикл буд короткий или длинный, причем налич всех нулей в младших разрядах реги ра 3 адреса свидетельствует о том, что (k-1)-й цикл короткий, наличие хотя бы одной единицы - длинный.

В исходном состоянии триггеры 8 22 и 23 установлены в состояние ну (цепи предварительной установки на схемах не показаны). На входе 20 б кировки блока 7 находится потенциа О, на входе запуска 19 - потенци 1 (фиг.2). С нулевых выходов три геров 22 и 23 уровни логической 1 пос тупают на входы элемента И 28, выхода которого 1 поступает на в ход 18 блока 7, на выходы 16 и 17 которого с единичных выходов тригг ров 22 и 23 поступают О. На инфо мационный вход триггера 22 с выход элемента ИЛИ 30 поступает 1, т.е устройство готово к работе .

Положительный полупериод первог импульса с выхода 33 (фиг.За) гене ратора 21 поступает на С-вход триг ра 22 и своим передним фронтом уст навливает триггер 22 в 1. С появ нием на вькоде 33 генератора 21 пе вого положительного полупериода на нается (и-1)-й цикл работы устройства.

С единичного выхода триггера 22 импульс ТИ1 (фиг.38) поступает на ход 16 блока 7. С нулевого выхода триггера 22 О поступает через эл мент И 28 на выход 18 блока 7 (фиг.31). С выхода 16 блока 7 1 поступает на вход записи-чтения вы ходного регистра 4, в который запи вается информация с выхода мультип ксора 5 (фиг.1).

Отрицательный полупериод первог

Импульсы 16 (ТИ1) и 17 (ТИ2), выра- инпульса с выхода 33 генератора 21

батываемые блоком 7 (возможная схема реализации приведена на фиг.2), образуют временную развертку короткого цикла, при котором информация на выход 15 устройства поступает из быстрой памяти. Импульсы 16, 17 и 18 (ТИЗ) образуют временную развертку длинного цикла - процессор работает

55

поступает через элемент НЕ 24 на С-вход триггера 23, устанавливая п ледний в 1. (фиг.36), которая пос пает на выход 17 блока 7 и через элементы И-НЕ 31 и И 26 устанавлив ет триггер 22 в О, который свиде тельствует об окончании ТИ1. С нул вого выхода триггера 23 О поступ

0

5

0

5

0

5

0

5

с одной из медленных памятей, входящих в блок 2 памяти.

Триггер 8 пуска в (k-l)-M цикле, в зависимости от состояния младших разрядов регистра 3 адреса, определяет тип подключаемой в К-м цикле памяти - быстрая или медленная и в соответствии с этим (К-1)-й цикл будет короткий или длинный, причем наличие всех нулей в младших разрядах регистра 3 адреса свидетельствует о том, что (k-1)-й цикл короткий, наличие хотя бы одной единицы - длинный.

В исходном состоянии триггеры 8, 22 и 23 установлены в состояние нуля (цепи предварительной установки на схемах не показаны). На входе 20 блокировки блока 7 находится потенциал О, на входе запуска 19 - потенциал 1 (фиг.2). С нулевых выходов триггеров 22 и 23 уровни логической 1 пос тупают на входы элемента И 28, с выхода которого 1 поступает на выход 18 блока 7, на выходы 16 и 17 которого с единичных выходов триггеров 22 и 23 поступают О. На инфор- мационный вход триггера 22 с выхода элемента ИЛИ 30 поступает 1, т.е. устройство готово к работе .

Положительный полупериод первого импульса с выхода 33 (фиг.За) генератора 21 поступает на С-вход триггера 22 и своим передним фронтом устанавливает триггер 22 в 1. С появлением на вькоде 33 генератора 21 первого положительного полупериода начинается (и-1)-й цикл работы устройства.

С единичного выхода триггера 22 импульс ТИ1 (фиг.38) поступает на выход 16 блока 7. С нулевого выхода триггера 22 О поступает через элемент И 28 на выход 18 блока 7 . (фиг.31). С выхода 16 блока 7 1 поступает на вход записи-чтения выходного регистра 4, в который записывается информация с выхода мультиплексора 5 (фиг.1).

Отрицательный полупериод первого

поступает через элемент НЕ 24 на С-вход триггера 23, устанавливая последний в 1. (фиг.36), которая поступает на выход 17 блока 7 и через элементы И-НЕ 31 и И 26 устанавливает триггер 22 в О, который свидетельствует об окончании ТИ1. С нулевого выхода триггера 23 О поступает

10

15

31377866

на вход элемента И 28, подтверждая на выходе 18 блока 7 состояние О. С выхода 17 блока 7 ТИ2 поступает на вход записи-чтения регистра 3 адреса, в который по переднему франту записывается адрес информации, которая будет обрабатываться в следующем цикле работы процессора. В младших разрядах регистра 3 адреса находится код всех нулей, свидетельствующий о том, что в следующем цикле процессор будет работать с быстрой памятью. Младшие разряды регистра 3 адреса соединены с входами элемента ИЛИ 11, О с выхода которого поступает на информационный вход триггера 8 пуска, на вход 20 блокировки блока 7 и на вход управления мультиплексора 5, который

с приходом данного сигнала подключает на свой выход данные, поступающие с блока 1 памяти. С входа 20 блокировки блока 7 О через элементы НЕ 25, И 29 и РШИ 30, проинвертировав- шись, поступает на информационный вход триггера 22. С выхода 33 генератора 21 второй положительный полуде- риод поступает на С-вход триггера 22

и своим передним фронтом устанавливает на его выходе 1. С единичного выхода триггера 22 ТИ1 поступает на выход 16 блока 7 и через элементы И-НЕ 32 И 27 устанавливает триггер

23 в О.

С выхода 17 блока 7 О поступает на элемент НЕ 13, с выхода которого 1 поступает на С-вход триггера 8 пуска, своим передним фронтом подтверждая на нулевом выходе триггера 8 пуска 1, которая поступает на вход 19 запуска блока 7, разрешая формирование временной развертки следующего цикла.

С появлением на выходе 33 генератора 21 второго положительного полупериода начинается k-й цикл работы устройства. Формирование ТИ1 и ТИ2 происходит аналогичным образом, как и в (k-1)-и цикле. С выхода 16 блока 7 ТИ1 поступает на вход Запись-чте20

25

30

35

40

45

50

ва ся ни ши вх ды

па вр па

ра но

ще ды эл ра по бл ИЛ он ко со Сегту С эл ле на О но

вы по эл по эл вх ра за со

эл вы И ву ме ИЛ по сч ле хо

вне выходного регистра 4, своим передним фронтом записывая в него данные с выхода мультиплексора 5, С выходного регистра 4 данные (k-l)-ro цикла поступают на выход 15 устройства. .Затем на выходе 17 блока 7 появ- ляется импульс ТИ2, передним фронтом которого в регистр 3 адреса с входа 14 устройства записывается адрес ин0

5

0

5

0

5

0

5

0

5

формации, которая будет обрабатываться процессором в следующем цикле, В коде младших разрядов адреса имеется в наличии одна или несколько единиц. С выхода регистра 3 адреса младшие адресные разряды поступают на входы элемента ИЛИ 11 и адресные входы памяти 6 признаков обращения.

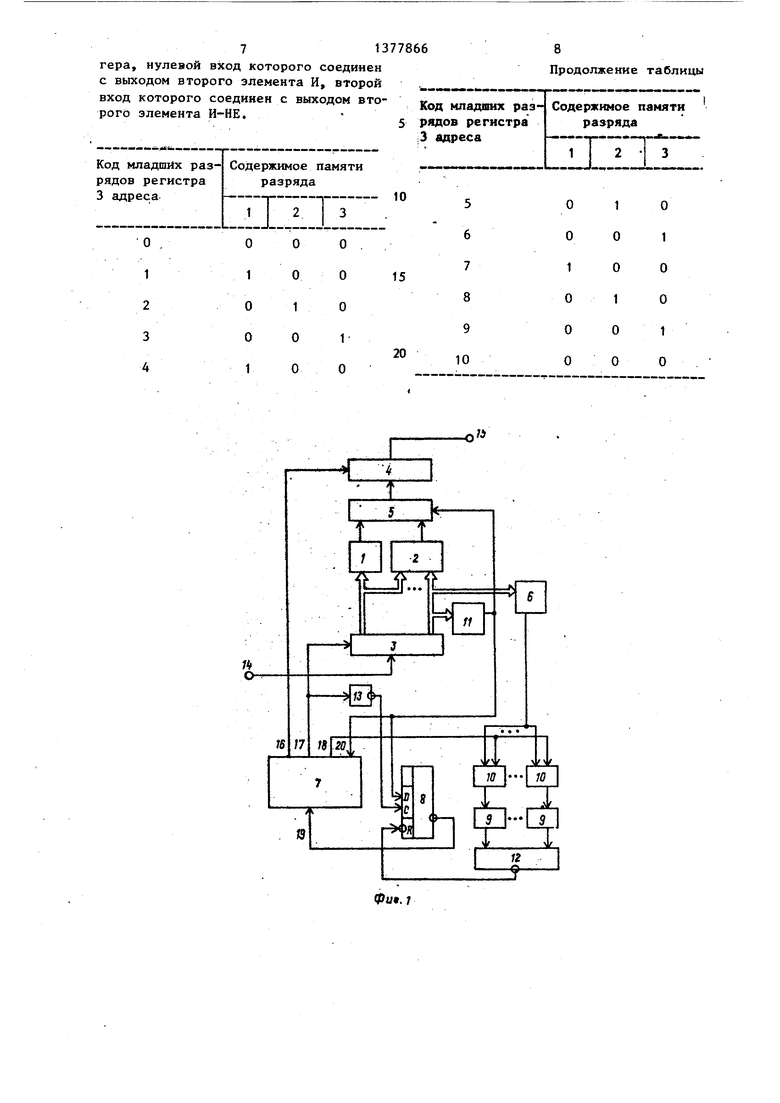

Рассмотрим случай, когда блок 2 памяти состоит из трех различных по временным характеристикам медленных памятей..

Содержимое памяти 6 признаков .обращения для данного примера приведено в таблице.

С выхода памяти 6 признаков обращения выбранный код поступает на входы группы элементов И 10. С выхода элемента ИЛИ 11 1 поступает на управляющий вход мультиплексора 5, подключая на его выход информацию с блока ,2 памяти. С выхода элемента ИЛИ 11 1 также поступает на вход 20 блокировки блока 7 и на информационный вход триггера 8 запуска. По концу ТИ2 положительный фронт импульсов с элемента НЕ 13 поступает на Свход триггера 8 и устанавливает на его нулевом выходе О, который поступает на вход 19 блока 7 (фиг. 32), С входа 19 блока 7 уровень О элементы И 26 и 27 поступает на нулевые входы триггеров 22 и 23, устанавливая на их единичных выходах О, которые поступают соответственно на выходы 16 и 17 блока 7. С нулеit.. It

вых выходов триггеров и уровни 1 поступают соответственно на входы элемента И 28, с выхода которого 1 поступает на выход 18 блока 7 и через элемент РШИ 30 на информационный вход триггера 22. Выработка очередной развертки синхросигналов блокируется, запрещая изменение состояния процессора.

Импульс ТИЗ с выхода 18 блока 7 (фиг.З ) поступает на входы группы элементов И 10. С соответствующего выхода элемента И группы элементов И 10 1 поступает через соответствующий элемент задержки группы элементов 9 задержки на вход элемента ИЛИ-НЕ 12, на выходе которого О появляется одновременно с появлением считываемой информации на выходе медленной памяти блока 2 памяти. С выхода элемента ИЛИ-НЕ 12 О поступает

на вход установки в О триггера 8 пуска и устанавливает триггер 8 пуска в 1 на нулевом выходе. С нулевого выхода триггера 8 пуска 1 поступает на вход 19 запуска блока 7, разрешая формирование новой развертки синхросигналов.

В следующем (k-1)M цикле работы процессора информация, считанная из соответствующей медленной памяти блока 2 памяти, заносится по импульсу ТИ1 в выходной регистр 4 и поступает на выход 15 устройства.

Формула изобретения

1. Устройство для сопряжения памяти с процессором, содержащее выходной регистр, мультиплексор, два блока памяти, память признаков обращения, регистр адреса, триггер пуска, группу элементов И, группу элементов задержки, элемент ИЛИ, причем информационный вход регистра адреса является входом устройства для подключенияк адресному выходу процессора, информационный выход выходного регистра является выходом устройства для подключения- к адресному входу памяти, при этом группа старших разрядов информационного выхода регистра адреса соединена с группой адресных входов первого блока памяти и с первой группой адресных входов второго блока памяти, информационные выходы которь1Х соединены соответственно с первым и вторым информационными входами мультиплексора, информационный выход которого соединен с информационным входом выходного регистра, управляющий вход мультиплексора соединен с информационным входом триггера пуска и с выходом элемента ИЛИ, группа входов которого соединена с второй группой адресных входов второго блока памяти, с группой младших разрядов информационного выхода регистра адреса и с группой адресных входов памяти признаков обращения, информационный выход которого соединен с первыми входами элементов И группы, выходы которых соединены с входами элементов задержки группы, отличающееся тем, что, с целью повьщ1ения быстродействия, в него введены блок управления, элемент ИЛИ-НЕ, элемент НЕ, при этом выходы элементов задержки группы соединены с группой входов

о 5 5

0

5

0

5

0

элемента ИЛИ-НЕ, выход которого соединен с нулевым входом триггера пуска, нулевой выход которого соединен с входом запуска блока управления, вход блокировки которого соединен с выходом элемента ИЛИ, вход записи- чтения выходного регистра соединен с первым выходом блока управления, второй выход которого соединен с входом записи-чтения регистра адреса и С входом элемента НЕ, выход которого соединен с синхровходом триггера пуска, третий выход блока управления соединен с вторыми входами элементов И группы.

2. Устройство по П.1, отличающееся тем, что блок управления содержит генератор импульсов, два триггера, четыре элемента И, два элемента И-НЕ, два элемента НЕ, элемент ИЛИ, причем первый вход первого элемента И соединен с первым входом второго элемента И и является входом запуска блока управленияj вход первого элемента НЕ является входом блокировки блока управления, единичный выход первого триггера соединен с информационным входом второго триггера, с первыми входами первого, второго элементов И-НЕ и является первым выходом блока управления, единичный выход второго триггера соединен с первЬгм входом третьего элемента И, с вторыми входами первого, второго элементов И-НЕ и является вторым выходом блока управления, выход четвертого элемента И .соединен с первым входом элемента ИЛИ и является третьим выходом блока управления, при этом в блоке управления выход первого элемента НЕ соединен с вторым входом третьего элемента И , выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с информационным входом первого триггера, синхровход которого соединен с третьим входом второго элемента И-НЕ, с выходом генератора импульсов и с входом второго элемента НЕ, выход которого соединен с синхровходом второго триггера и с третьим входом первого элемента И- НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с нулевым входом первого триггера, нулевой выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с нулевым выходом второго триг71377866

гера, нулевой вход которого соединен с выходом второго элемента И, второй

8

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для ввода информации | 1989 |

|

SU1644120A2 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах с микропрограммным управлением. Целью изобретения является повышение быстродействия. Устройство содержит блок управления, два блока памяти, регистр адреса выходной информации, выходной регистр, мультиплексор, память признаков обращения, триггер пуска, элемент ИЛИ, элемент ИЛИ-НЕ, элемент НЕ группу элементов И, группу элементов задержки. Гз.п. , 3 ил., 1 табл.

| Устройство для сопряжения процессора с памятью | 1980 |

|

SU898437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-10-02—Подача