Изобретение относится к вычислительной технике и может быть использовано в устройствах измерения и ре- гулирования.

Цель изобретения - повышение точности .

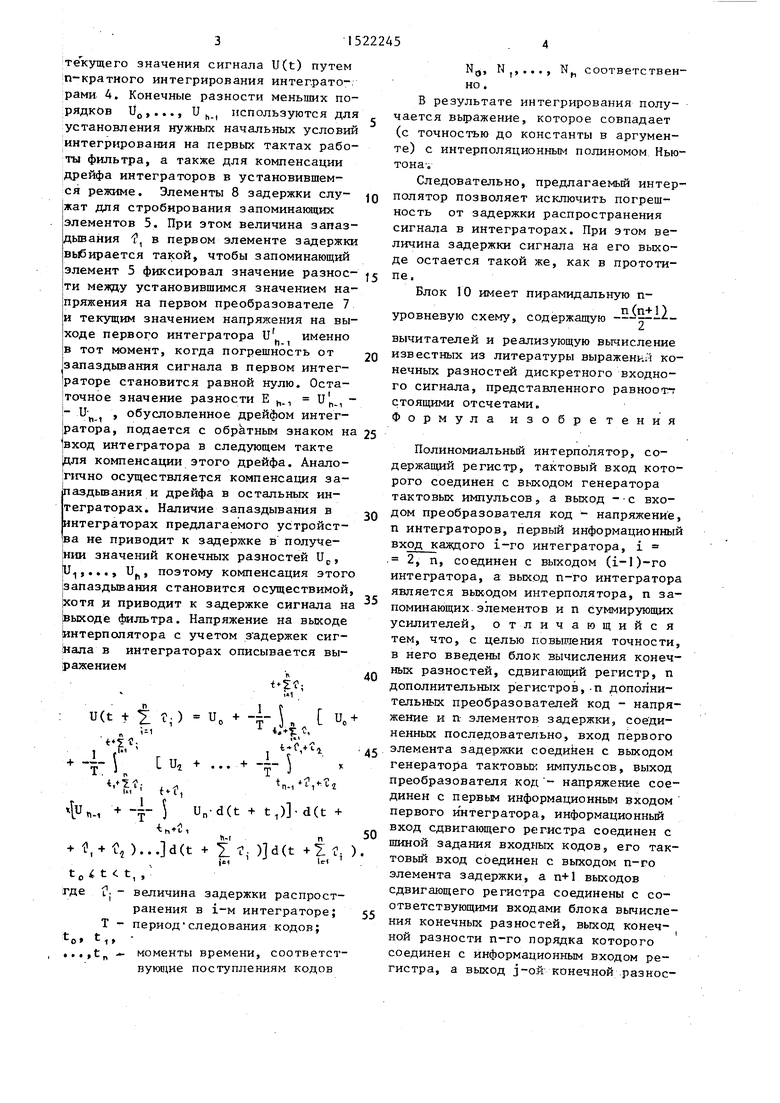

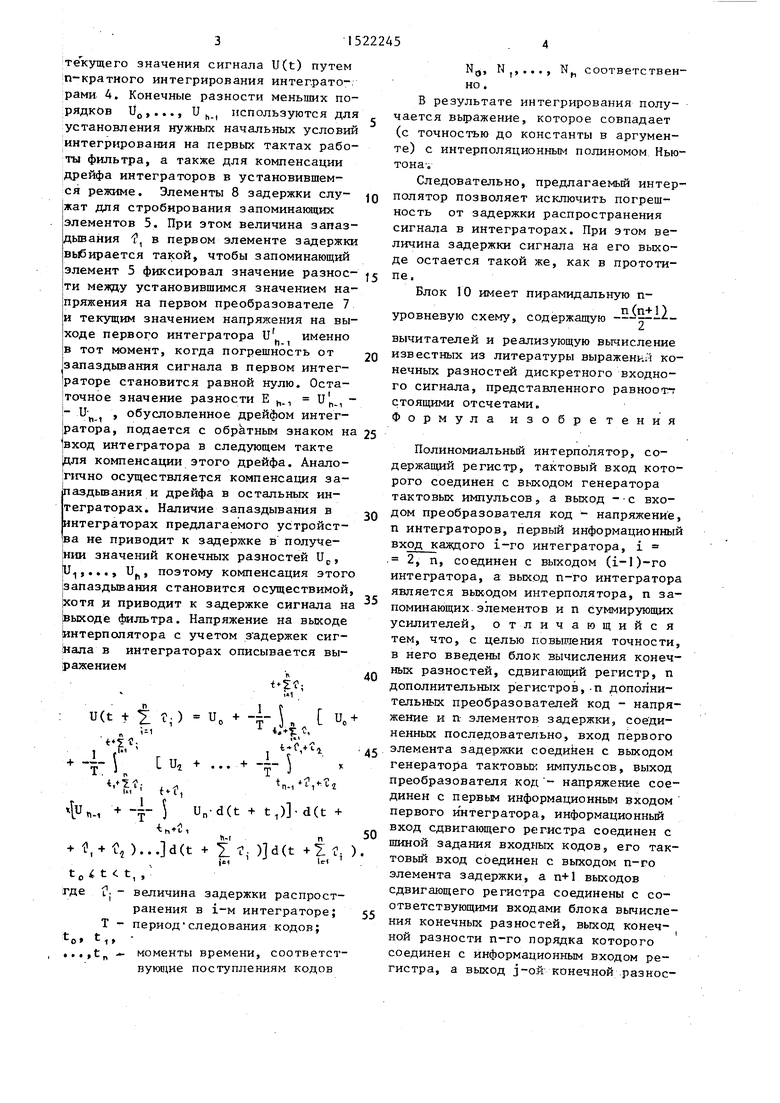

На чертеже представлена схема предлагаемого интерп.олятора.

Полиномиальный интерполятор содержит генератор 1 тактовых импульсов, регистр 2, преобразователь 3 код - напряжение, интеграторы , запоминающие элементы 5 , -5„, суммирующие усилители 6,-6р, дополнительные преобразователи 7т-7„ код - напряжение, элементы 8 ,-8 задержки, дополнительные регистры 9,-9„, блок 10 вычисления конечных разностей и сдвигающий регистр 11.

Устройство работает следующим образом.

Последовательньй многоразрадньш сдвигающий регистр П на калддом такте записывает очередное значение кода сигнала N и хранит его вместе с предыдущими п кодами N...N. Из этих (п+1) значений кода сигнала блок 10 конечньгх разностей п-го порядка формирует на своих (п+1) выходах коды :. конечных разностей:- от нулевого до п-го порядка Л 5, - Л .

Регистры 2 и 9 служат для синхронизации работы преобразователей 3 и 7 код - напряжение. Эти регистры уп- равляются тактовыми импульсами от генератора 1 тактовых импульсов, задержанными на нужную величину элементами 8 задержки. Преобразователи 3 и 7 код - напряжение преобразуют коды конечных разностей в аналоговую форму

О1

к

ю

«и О1

и„, и.

и,

с « 1 S h

п-го порядка и

о Конечная разность

„ служит для получения

текущего значения сигнала U(t) путем |п-кратиого интегрирования интег.рато-. рами 4, Конечные разности меньших порядков и ,..., и ,,, используются для установления нужных начальных условий интегрирования на первых тактах работы фильтра, а также для компенсации дрейфа интеграторов в установившемся режиме. Элементы 8 задержки слу- жат для стробирования запоминающих элементов 5. При этом величина запаз- дьшания , в первом элементе задержки выбирается такой, чтобы запоминающий элемент 5 фиксировал значение разнос- ти меаду установившимся значением напряжения на первом преобразователе 7 и текущим значением напряжения на выходе первого интегратора U именно в тот момент, когда погрешность от запаздывания сигнала в первом интеграторе становится равной нулю. Оста- 1точное значение разности Е ц., U , - |- и- , обусловленное дрейфом интегратора, подается с обратным знаком на вход интегратора в следующем такте цля компенсации этого дрейфа. Анало- 1гично осуществляется компенсация за- паздьшания и дрейфа в остальных интеграторах. Наличие запаздывания в интеграторах предлагаемого устройства не приводит к задержке в получе- |шш значений конечных разностей Up, 1,..., и, поэтому компенсация этого Запаздывания становится осуществимой |хотя и приводит к задержке сигнала на ыходе фильтра. Напряжение на выходе Интерполятора с учетом з адержек сиг- 1нала в интеграторах описывается выражением

Un-, 4- „-dCt + t,)-d(t +

h+

+ ,н- )...d(t + Z T. )d(t +1:, ).

jii

t,

it,,

величина задержки распространения в i-M интеграторе; Т - период следования кодов;

. .,tn моменты времени, соответствующие поступлениям кодов

N3, N,,..., N соответственно .

В результате интегрирования получается выражение, которое совпадает (с точностью до константы в аргументе) с интерполяционным полиномом Ньютона-.

Следовательно, предлагаемый интерполятор позволяет исключить погрешность от задержки распространения сигнала в интеграторах. При этом величина задержки сигнала на его выходе остается такой же, как в прототипе,

Блок 10 имеет пирамидальную пуровневую схему, содержащую

п(п+|2

вычитателей и реализующую вычисление известных из литературы выражений конечных разностей дискретного входного сигнала, представленного равноотт стоящими отсчетами. Формула изобретения

Полиномиальный интерполятор, содержащий регистр, тактовый вход которого соединен с выходом генератора тактовых импульсов, а выход --с входом преобразователя код - напряжение, п интеграторов, первый информационный вход каждого 1-го интегратора, i . 2, п, соединен с выходом (i-I)-ro интегратора, а выход п-го интегратора является выходом интерполятора, п запоминающих элементов и п суммирующих усилителей, отличающийся тем, что, с целью повышения точности, в него введены блок вычисления конечных разностей, сдвигающий регистр, п дополнительных регистров,-п дополнительных преобразователей код - напряжение и п элементов задержки, соединенных последовательно, вход первого элемента задержки соедийен с выходом генератора тактовык импульсов, выход преобразователя код - напряжение соединен с первым информационным входом первого интегратора, информационный вход сдвигающего регистра соединен с шиной задания входньпс кодов, его тактовый вход соединен с выходом п-го элемента задержки, а п+1 выходов сдвигающего регистра соединены с соответствующими входами блока вычисления конечных разностей, выход конечной разности п-го порядка которого соединен с информационным входом регистра, а выход j-ой конечной разности, j О, h-l, соединен с информаци- онным входом (n-j)-ro дополнительного регистра, выход которого через соответствующий дополнительный преобразователь код - напряжение соединен с первым входом (n-j)-ro суммирующего усилителя, второй вход которого соединен с выходом (n-j)-ro интегратора.

а выход - с информационным входом (n-j)-ro запоминающего элемента, выход которого соединен с вторым информационным входом (n-j)-ro интегратора, выход (n-j)-ro элемента задержки соединен с тактовыми входами (n-j)-x дополнительного регистра и запоминающего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1983 |

|

SU1142848A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Интерполятор | 1986 |

|

SU1334167A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Панорамный измеритель частоты | 1984 |

|

SU1267273A1 |

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах измерения и регулирования. Цель изобретения - повышение точности. Полиноминальный интерполятор содержит генератор тактовых импульсов, регистр, преобразователь код напряжение, интеграторы, запоминающие элементы, суммирующие усилители, дополнительные преобразователи код-напряжение, элементы задержки, дополнительные регистры, блок вычисления конечных разностей, сдвигающий регистр. Интерполятор позволяет исключить погрешность от задержки распространения сигнала в интеграторах. 1 ил.

| Нелинейный интерполятор | 1979 |

|

SU851425A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Интерполирующий фильтр | 1977 |

|

SU663074A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1988-04-18—Подача