О)

ел

Изобретение относится к вычислительной технике и может быть использовано для построения устройств арифметической и логической обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей путем формирования функций конъюнкции, дизъюнкции, отрицания равнозначности константы нуля и константы единицы.

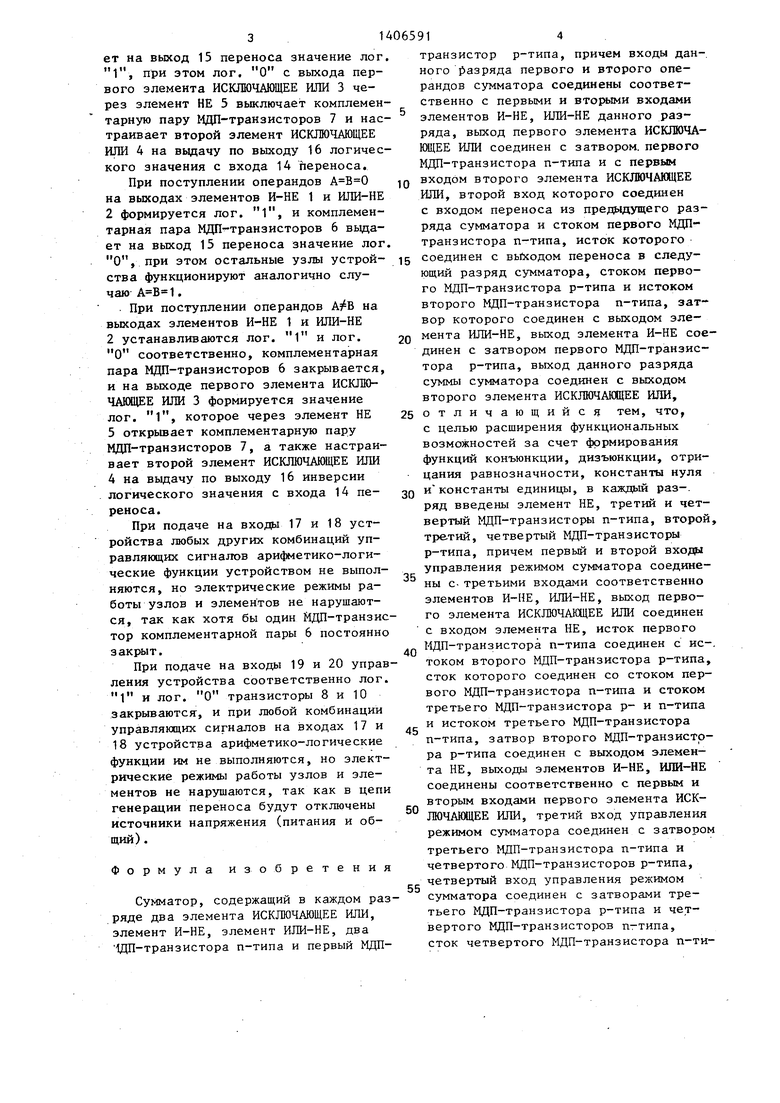

На чертеже представлена функциональная схема сумматора.

Сумматор содержит в каждом разряд элементы И-НЕ 1, ИЛИ-НЕ 2, первый 3 и второй 4 элементы ИСКЛОЧАЩЕЕ ИЛИ, элемент НЕ 5, комплементарную пару МДП-транзисторов 6 (генерации переноса) ,-комплементарную пару МДП-транзисторов 7 (передачи переноса), два МДП -транзистора 8, 9 р-типа, два МДП-транзистора 10, 11 п-типа, входы 12, 13 первого и второго операндов, вход 14 и выход 15 переноса, выход 16 суммы, первый 17, второй 18, третий 19 и четвертый 20 входы управления режимом, шины 21, 22 питания и нулевого потенциала.

Набор функций, выполняемых устройством, и соответствующие коды управляющих сигналов представлены в таблице, где буквами А, В и С обозначены входы первого 12, второго 13 операндов и вход 14 переноса соответ

Устройство работает следующим образом.

При подаче на входы 19 и 20 управления лог. 1 МДП-транзисторы В и 9 закрываются, МДП-транзисторы 10 и 11 открьшаются, на входе 14 переноса устанавливается значение лог

О

так что второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 передает на вькод 16 состояние ,выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 без изменений.

При подаче на входы 17 и 18 управления лог. О на выходе элемента И- НЕ 1 устанавливается лог. 1. Первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3 инвертирует значение выхода элемента ШШ-НЕ 2, выдавая на выход 16 функцию дизъюнкции входньк операндов.

При подаче на входы 17 и 18 управления лог. 1 и лог. О соответственно на выходе первого элемента ИСК- ЛЮЧАЩЕЕ ИЛИ 3 формируется функция отрицания равнозначности

F (АЛВ)Л (AVB) V (АЛЕ) Л (AvB) (АЛ В) ч/ (АЛВ),

которая передается на выход 16 без изменений. .

При подаче на входы 17 и 18 управления соответственно лог.

О

де 15 , ны й35

30

40

О,

25 и лог. 1 выходы элементов И-НЕ

1и ИЛИ-НЕ 2 устанавливаются в состояние лог. 1 и лог. О соответственно, так что первый элемент ИСКЛЮЧАЩЕЕ ИЛИ 3 выдает на выход 16 значение константы лог. 1.

При подаче на входы 17 и 18 управления лог. 1 на выходе элемента ИЛИ-НЕ 2 устанавливается лог. О, и первьш элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3 передает на выход 16 функцию отрицания конъюнкции входных операндов с выхода элемента И-НЕ 1.

При подаче на входы 19 и 20 управления лог. О МДП-транзисторы 10 .и 11 закрываются, а МДП- транзисторы

8 и 9 открываются и устанавливают на входе 14 переноса значение лог. 1, так что второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 передает на выход 16 устройства инверсию сигнала с выхода первого элемента ИСКЛЮЧАЩЕЕ ИЛИ 3.

При подаче на входы 19 и 20 управления соответственно лог. О и лог. 1 МДП-транзисторы 8 и 10 открываются, МДП-транзисторы 9 и 11 закрываются, и при наличии на входах 17 и 18 управления лог. 1 и лог. О соответственно устройство функциони- -рует как сумматор с шиной последовательного распространения переноса.

При поступлении операндов на вькодах элементов И-НЕ 1 и ИЛИ-НЕ

2формируется лог. О, и комплементарная, пара МДП-транзисторов 6 выда45

50

55

3

ет на выход 15 переноса значение ло 1, при этом лог. О с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 через элемент НЕ 5 выключает комплеметарную пару 1 1ДП-транзисторов 7 и натраивает второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 на вьщачу по выходу 16 логичекого значения с входа 14 переноса.

При поступлении операндов на выходах элементов И-НЕ 1 и ШШ-Н 2 формируется лог. 1, и комплементарная пара МДП транзисторов 6 выдает на выход 15 переноса значение ло О, при этом остальные узлы устрой ства функционируют аналогично случаю .

При поступлении операндов на выходах элементов И-НЕ 1 и ИЛИ-НЕ

2устанавливаются лог. 1 и лог. О соответственно, комплементарная пара МДП-транзисторов 6 закрывается

и на выходе первого элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ 3 формируется значение лог. 1, которое через элемент НЕ 5 открьшает комплементарную пару МДП-транзисторов 7, а также настраивает второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 на выдачу по выходу 16 инверсии логического значения с входа 14 пе- реноса.

При подаче на входы 17 и 18 устройства любых других комбинаций управляющих сигналов арифметико-логические функции устройством не выполняются, но электрические режимы работы узлов и элементов не нарушаются, так как хотя бы один МДП-транзи тор комплементарной пары 6 постоянн

3акря 1т.

При подаче на входы 19 и 20 упраления устройства соответственно лог 1 и лог. закрываются

управляющих сигналов на входах 17 и 18 устройства арифметико-логические функции им не выполняются, но электрические режимы работы узлов и элементов не нарушаются, так как в цеп генерации переноса будут отключены источники напряжения (питания и общий) .

О транзисторы 8 и 10 и при любой комбинации

Формула изобретения

Сумматор, содержащий в каждом раз- ,ряде два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элемент ИЛИ-НЕ, два 1ДП-транзистора п-типа и первый МДП5

0

5 о

0

5

5

0

5

транзистор р-типа, причем входы дан-, ного азряда первого и второго операндов сумматора соединены соответственно с первыми и вторыми входами элементов И-НЕ, ШШ-НЕ данного разряда, выход первого элемента ИСКЛЮЧА- ЩЕЕ ИЛИ соединен с затвором, первого МДП-транзистора п-типа и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом переноса из предыдущего разряда сумматора и стоком первого МДП- транзистора п-типа, исток которого соединен с вьб:одом переноса в следующий разряд сумматора, стоком первого МДП-транзистора р-типа и истоком второго МДП-транзистора п-типа, затвор которого соединен с выходом элемента ИЛИ-НЕ, выход элемента И-НЕ соединен с затвором первого МДП-транзистора р-типа, выход данного разряда суммы сумматора соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования функций конъюнкции, дизъюнкции, отрицания равнозначности, константы нуля и константы единицы, в каждагй раз-, ряд введены элемент НЕ, третий и четвертый МДП-транзисторы п-типа, второй, третий, четвертый МДП-транзисторы ртипа, причем первый и второй входы управления режимом сумматора соединены с. третьими входами соответственно элементов И-НЕ, ИЛИ-НЕ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом элемента НЕ, исток первого 1-ЩП-транзистора п-типа соединен с ис-. током второго МДП-транзистора р-типа, сток которого соединен со стоком первого МДП-транзистора п-типа и стоком третьего МДП-транзистора р- и п-типа и истоком третьего МДП-транзистора птипа, затвор второго МДП-транзистора р-типа соединен с выходом элемента НЕ, выходы элементов И-НЕ, ИЛИ-НЕ соединены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход управления режимом сумматора соединен с затвором третьего МДП-транзистора п-типа и четвертого МДП-транзисторов р-типа, четвертый вход управления режимом - сумматора соединен с затворами третьего МДП-транзистора р-типа и четвертого МДП-транзисторов п-типа, сток четвертого МДП-транзистора п-ти514065916

па соединен с шиной нулевого потен-тора соединена с истоком четвертого

циала сумматора, а его исток - соМДП-транзистора р-типа, сток которостоками второго и третьего МДП-тран-го соединен с истоками первого и трезисторов п-типа, шина питания сумма-тьего МДП-транзнеторов р-типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР | 1994 |

|

RU2049346C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Узел формирования переноса | 1987 |

|

SU1434426A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Логический элемент на КМДП-транзисторах | 1985 |

|

SU1262721A1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| Логический элемент на МДП-транзисторах | 1987 |

|

SU1480116A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

Изобретение относится к вычис- 1лительной технике, в частности к устройствам для арифметической и ло/J гической обработки цифровой информации. Цель изобретения - расширение функциональных возможностей сумматора за счет формирования функций конъюнкции, отрщания конъюнкции, дизъюнкции, отрицания дизъюнкции, равнозначности, отрицания равнозначности, констант О и единицы. Сумматор содержит в каждом разряде элементы И-НЕ 1, ИЛИ-НЕ 2, ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4, элемент НЕ 5, ВДП-транзис- торы р-типа 8, 9, комплементарные пары МДП-транзисторов 6, 7, МДП-тран- зисторы п-типа 10, 11. 1 ил., 1 табл. (Л

| Патент США № 4417314, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| СПОСОБ ПРОГНОЗИРОВАНИЯ РЕСУРСОСПОСОБНОСТИ СТАЛЕЙ КОРПУСОВ РЕАКТОРОВ ВВЭР-1000 | 2013 |

|

RU2534045C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-24—Подача