и восьмой групп подключены соответственно к выходам элементов И первой группы и к выходам элементов И третьей группы, выходы элементов И пятой группы соединены с входами элементов И одиннадцатой группы и входами второй группы входов элементов И девятой группы, выходы элементов И седьмой, девятой и одиннадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов третьего формирователя сигналов четности, одни из входов элементов И шестой группы и входы первой груггпы входов элементов И десятой группы соединены с одними из числовых выходов накопителя, выходы элементов И шестой группы подключены к входам элементов И двенадцатой группы и входам второй группы входов элементов И десятой группы, входы третьей группы входов элементов И девятой и десятой групп соединены соответственно с выходами формирователей контрольных сигналов по модулю три первой и второй групп, выходы элементов И восьмой, десятой и двенадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности, входы третьей группы входов элементов И второй группы являются инверсными информационными входами устройства, входы третьей группы входов элемента И четвертой группы подключены к другим числовым выходам накопителя.

3.Устройство по п. 1, отличающееся тем, что в него введены группы элементов ИЛИ и группы с пятой по десятую элементов И, причем одни из входов элементов И пятой группы и элементов ИЛИ первой группы подключены к числовым входам накопителя, а выходы - соответственно к одним из входов элементов И девятой группы и входам элементов И седьмой группы и к другим входам элементов И девятой группы, выходы элементов И седьмой и девятой групп соединены соответственно с входами третьей

и четвертой групп входов третьего формирователя сигналов четности, одни из входов элементов И шестой группы и элементов ИЛИ второй группы подключены к числовым выходам накопителя,- а выходы - соответственно к одним из входов элементов И десятой группы и входам элементов И восьмой группы и к другим входам элементов И десятой группы, выходы элементов И восьмой и десятой групп соединены соответственно с входами третьей и четвертой групп входов четвертого формирователя сигналов четности.

4.Устройство по п. 1, отличающееся тем, что в него введены группы элементов ИЛИ и группы элементов И с пятой по двенадцатую, причем одни из входов элементов ИЛИ первой группы и элементов И пятой группы подключены к числовым входам накопителя, одни из числовых выходов которого соединены с одними из входов элементов ИЛИ второй группы и элементов И шестой группы, входы элементов И седьмой и восьмой групп подключены соответственно к выходам элементов И первой группы и к выходам элементов И третьей группы, выходы элементов И пятой группы соединены с входами первой группы входов элементов И одиннадцатой и девятой групп, входы второй группы входов элементов И девятой группы подключены к выходам элементов ИЛИ первой группы, выходы эле.ментов И седьмой, девятой и одиннадцатой групп соединены соответственно с входами третьей, четвертой и пятой групп входов третьего формирователя сигналов четности, выходы элементов И шестой группы подключены к входам первой группы входов элементов И десятой и двенадцатой групп, входы второй группы входов элементов И десятой группы соединены с выходами элементов ИЛИ второй группы, входы второй группы входов элементов И двенадцатой группы и входы третьей группы входов элементов И четвертой группы подключены к другим числовым выходам накопителя, входы третьей группы входов эле.ментов И второй группы и входы второй группы входов элементов И одиннадцатой группы являются инверсными информационными входами устройства, выходы элементов И восьмой, десятой и двенадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности, входы третьей группы входов элементов И девятой и десятой групп соединены соответственно с числовыми входами и выходами накопителя.

5. Устройство по п. 1, отличающееся тем, что в него введены группы элементов И с пятой по двенадцатую и группы элементов ИЛИ, причем одни из входов элементов ИЛИ первой группы и элементов И пятой группы соединены с числовыми входами накопителя, одни из числовых выходов которого подключены к одним из входов элементов ИЛИ второй группы и элементов И шестой группы, одни из входов элементов И седьмой и восьмой групп соединены соответственно с выходами элементов И первой группы и с выхода.ми элементов И третьей группы, выходы элементов И пятой группы подключены к другим входам элементов И седьмой группы, к входам элементов И одиннадцатой группы и к одним из входов элементов И девятой группы, другие входы которых соединены с выходами элементов ИЛИ первой группы, выходы элементов И седьмой, девятой и одиннадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов третьего формирователя сигналов четности, выходы элементов И шестой группы соединены с входами элементов И двенадцатой группы, другими входами

элементов И восьмой группы и одними из входов элементов И десятой группы, другие входы которых подключены к выходам элементов ИЛИ второй группы, выходы элементов И восьмой, десятой и двенадцатой групп соединены соответственно с входами третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности.

6.Устройство по п. 1, отличающееся тем, что адресные входы накопителя соединены с другими входами формирователей сигналов четности первой и второй групп и формирователей контрольных сигналов по модулю три первой и второй групп, а другие входы элементов И первой и третьей групп являются инверсными адресными входами устройства.

7.Устройство по пп. 1, 2 и 6, отличающееся тем, что адресные входы накопителя соединены с другими входами элементов И пятой, шестой групп и входами четвертой

группы входов элементов И девятой и десятой групп, а входы четвертой группы входов элементов И второй и четвертой групп являются инверсными адресными входами устройства.

8.Устройство по пп. 1, 3, 5 и 6, отличающееся тем, что адресные входы накопителя подключены к другим входам элементов ИЛИ первой и второй групп и другим входам элементов И пятой и шестой групп.

9.Устройство по пп. 1, 4 и 6, отличающееся тем, что адресные входы накопителя соединены с другими входами элементов ИЛИ первой и второй групп, с другими входами элементов И пятой и шестой групп и входами четвертой группы входов элементов И девятой и десятой групп, а входы четвертой группы входов элементов И второй и четвертой групп и входы третьей группы входов элементов И одиннадцатой и двенадцатой групп являются инверсными адресными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Вычислительное устройство для сокращения избыточности измерительных данных | 1974 |

|

SU506862A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1156146A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее группы формирователей сигналов четности, группы формирователей контрольных сигналов по модулю три, блок сравнения, формирователи сигналов четности и накопитель, числовые входы которого соединены с одними из входов формирователей контрольных сигналов по модулю три первой группы и одними из входов формирователей сигналов четности первой группы, выходы которых подключен к входам первого формирователя сигналов четности, выход которого соединен с первым контрольным входом накопителя, один из числовых выходов которого подключены к одним из входов формирователей контрольных сигналов по модулю три второй группы и одним из входов формирователей сигналов четности второй группы, выходы которых соединены с входами второго формирователя сигналов четности, причем одни из входов блока сравнения подключены соответственно к первому контрольному выходу накопителя и к выходу второго формирователя сигналов четности, выход блока сравнения является контрольным выходом устройства, информационными входами и выходами которого являются числовые входы и выходы накопителя, отличающееся тем, что, с целью повышения точности контроля устройства, в него введены группы элементов ИЛИ-НЕ, группы элементов И с первой по четвертую, третий и четвертый формирователи сигналов четности, причем одни из входов элементов ИЛИ-НЕ первой и второй групп соединены соответственно с выходами формирователей контрольных сигналов по модулю три первой и второй групп, одни из входов элементов И первой группы являются инверсными информационными входами устройства, другие входы элементов ИЛИ-НЕ первой группы и входы первой группы входов элементов И второй группы соединены с выходами формирователей сигналов четности первой группы, а выходы - соответственно с входами первой и второй групп входов третьего формирователя сигналов четности, выход кото(Л рого подключен к второму контрольному входу накопителя, входы второй группы входов элементов И второй группы соединены с выходами элементов И первой группы, входы первой группы входов элементов И четвертой группы и другие входы элементов ИЛИНЕ второй группы соединены с выходами формирователей сигналов четности второй группы, а выходы - соответственно с вхо дами первой и второй групп входов четвертого формирователя сигналов четности, вхосо со ды второй группы входов элементов И четвертой группы подключены к выходам элементов И третьей группы,- одни из входов которых соединены с другими числовыми выходами накопителя, другие входы блока сравнения соединены соответственно с вторым контрольным выходом накопителя и с выходами четвертого формирователя сигналов четности. 2. Устройство по п. 1, отличающееся тем, что в него введены группы элементов И с пятой по двенадцатую, причем одни из входов элементов И пятой группы и входы первой группы входов элементов И девятой группы соединены с числовыми входами накопителя, входы элементов И седьмой

1

Изобретение относится к вычислительной технике, в частности к устройствам хранения, приема и передачи данных, выполненным на интегральных микросхемах.

Известно устройство с обнаружением ошибок, содержашее модульный накопитель и блоки обнаружения ошибок, в которых используется модифицированный код Хэмминга 1.

Недостатком этого устройства является невозможность обнаруживать трехразрядные ошибки.

Наиболее близким к изобретению является запоминаюшее устройство с обнаружением ошибок, содержащее накопитель, выходы и входы которого соединены с входами и выходами регистра числа, блок контроля по четности и формирователи контрольного кода по модулю три 2.

Недостатками известного устройства являются низкая точность контроля устройства вследствие невозможности обнаруживать двукратные, четырехкратные ошибки и ошибки в адресных цепях, а также увеличение аппаратурных затрат и снижение быстродействия при применении модулей памяти с разрядностью, большей четырех разрядов.

Целью изобретения является повышениеточности контроля устройства, а также обеспечение возможности применения модулей памяти с более высокой разрядностью.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением ошибок, содержашее группы формирователей сигналов четности, группы формирователей контрольных сигналов по модулю три, блок сравнения, формирователи сигналов четности и накопитель, числовые входы которого соединены с одними из входов формирователей контрольных сигналов по модулю три первой группы и одними из входов формирователей сигналов четности первой группы, выходы которых подключены к входам первого формирователя сигналов четности, выход которого соединен с первым контрольным входом накопителя, одни из числовых выходов которого подключены к одним из входов формирователей контрольных сигналов по модулю три второй группы и одним из входов формирователей сигналов четности второй группы, выходы которых соединены с входами второго формирователя сигналов четности, причем одни из входов блока сравнения подключены соответственно к первому контрольному выходу накопителя и к выходу второго формирователя сигналов четности, выход блока сравнения является контрольным выходом устройства, информационными входами и выходами которого являются числовые входы и выходы накопителя, введены группы элементов ИЛИ-НЕ, группы элементов И с первой по четвертую, третий и четвертый формирователи сигналов четности, причем одни из входов элементов ИЛИ-НЕ первой и второй групп соединены соответственно с выходами формирователей контрольных сигналов по модулю три первой и второй групп, одни из входов элементов И первой группы являются инверсными информационными входами устройства, другие входы элементов ИЛИНЕ первой группы и входы первой группы входов элементов И второй группы соединены с выходами формирователей сигналов четности первой группы, а выходы - соответственно с входами первой и второй групп входов третьего формирователя сигналов четности, выход которого подключен к второму контрольному входу накопителя, входы второй группы входов элементов И второй группы соединены с выходами элементов И первой группы, входы первой группы входов элементов И четвертой группы и другие входы элементов ИЛИ-НЕ второй группы сое, „ динены .с выходами формирователей сигналов четности второй группы, а выходы - соответственно с, входами первой и второй групп входов четвертого формирователя сигналов четности, входы второй группы входов элементов И четвертой группы подключены к выходам элементов И третьей группы, одни из входов которых соединены с другими числовыми выходами накопителя, другие входы блока сравнения соединены соответственно с вторым контрольным выходом накопителя и с выходами четвертого формирователя сигналов четности. В устройство введены группы элементов И с пятой по двенадцатую, причем одни из входов элементов И пятой группы и входы первой группы входов элементов И девятой группы соединены с числовыми входами накопителя, входы элементов И седьмой и восьмой групп подключены соответственно к выходам элементов И первой группы и к выходам элементов И третьей группы, выходы элементов И пятой группы соединены с входами элементов И одиннадцатой группы и входами второй группы входов элементов И девятой группы, выходы элементов И седьмой, девятой и одиннадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов . третьего формирователя сигналов четности, одни из входов элементов И шестой группы и входы первой группы входов элементов И десятой группы соединены с одними из числовых выходов накопителя, выходы элементов И шестой группы подключены к входам элементов И двенадцатой группы и входам второй группы входов элементов И десятой группы, входы третьей группы входов элементов И девятой и десятой групп соединены соответственно с выходами формирователей контрольных сигналов по модулю три первой и второй групп, выходы элементов И восьмой, десятой и двенадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности, входы третьей группы входов элементов И второй группы являются инверсными информационными входами устройства, входы третьей группы входов элементов И четвертой группы подключены к другим числовым выходам накопителя. В устройство введены группы элементов ИЛИ и группы элементов И с пятой по десятую, причем одни из входов элементов И пятой группы и элементов ИЛИ первой группы подключены к числовым входам накопителя, а выходы - соответственно к одним из входов элементов И девятой группы и входам элементов И седьмой группы и к другим входам элементов И девятой группы, выходы элементов И седьмой и девятой групп соединены соответственно с входами третьей и четвертой групп входов третьего формирователя сигналов четности, одни из входов элементов И шестой группы и элементов ИЛИ второй группы подключены к числовым выходам накопителя, а выходы - соответственно к одним из входов элементов И десятой группы и входам элементов И восьмой группы и к другим входам элементов И десятой группы, выходы элементов И восьмой и десятой групп соединены соответственно с входами третьей и четвертой групп входов четвертого формирователя сигналов четности. Кроме того, в устройство введены группы элементов ИЛИ и группы элементов И с пятой по двенадцатую, причем одни из входов элементов ИЛИ первой группы и элементов И пятой группы подключены к числовым входам накопителя, одни из числовых выходов которого соединены с одними из входов элементов ИЛИ второй группы и элементов И шестой группы, входы элементов И седьмой и восьмой групп подключены соответственно к выходам элементов И первой группы и к выходам элементов И третьей группы, выходы элементов и пятой группы соединены с входами первой группы входов элементов И одиннадцатой и девятой групп, входы второй группы входов элементов И девятой группы подключены к выходам элементов ИЛИ первой группы, выходы элементов И седьмой, девятой и одиннадцатой групп соединены соответственно с входами третьей, четвертой и пятой групп входов третьего формирователя сигналов четности, выходы элементов И шестой группы подключены к входам первой группы входов элементов И десятой и двенадцатой групп, входы второй группы входов элементов И десятой группы соединены с выходами элементов ИЛИ второй группы, входы второй группы входов элементов И

двенадцатой группы и входы третьей группы входов элементов И четвертой группы подключены к другим числовым выходам накопителя, входы третьей группы входов элементов И второй группы и входы второй группы входов элементов И одиннадцатой группы являются инверсными входами устройства, выходы элементов И восьмой, десятой и двенадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности, входы третьей группы входов элементов И девятой и десятой групп соединены соответственно с числовыми входами и выходами накопителя.

При этом в устройство введены группы элементов И с пятой по двенадцатую и группы элементов ИЛИ, причем одни из входов элементов ИЛИ первой группы и элементов И пятой группы соединены с числовыми входами накопителя, одни из числовых выходов которого подключены к одним из входов элементов ИЛИ второй группы и элементов И шестой группы, одни из входов элементов И седьмой и восьмой групп соединены соответственно с выходами элементов И первой группы и с выходами элементов И третьей группы, выходы элементов И пятой группы подключены к другим входам элементов И седьмой группы, к входам элементов И одиннадцатой группы и к одним из входов элементов И девятой группы, другие входы которых соединены с выходами элементов ИЛИ первой группы, выходы элементов И седьмой, девятой и одиннадцатой групп подключены соответственно к входам третьей, четвертой и пятой групп входов третьего формирователя сигналов четности выходы элементов И шестой группы соединены с входами элементов И двенадцатой группы, другими входами элементов И восьмой группы и одними из входов элементов И десятой группы, другие входы которых подключены к выходам элементов ИЛИ второй группы, выходы элементов И восьмой десятой и двенадцатой групп соединены соответственно с входами третьей, четвертой и пятой групп входов четвертого формирователя сигналов четности.

Адресные входы накопителя соединены с другими входами формирователей сигналов четности первой и второй групп и. формирователей контрольных сигналов по модулю три первой и второй групп, а другие входы элементов И первой и третьей групп являются инверсными адресными входами устройства.

Адресные входы накопителя соединены с другими входами элементов И пятой, шестой групп и входами четвертой группы входов элементов И девятой и десятой групп, а входы четвертой группы входов элементов И второй и четвертой групп являются инверсными адресными входами устройства.

Кроме того, адресные входы накопителя подключены к другим входам элементов ИЛИ первой и второй групп и другим входам элементов И пятой и шестой групп.

Адресные входы накопителя соединены с другими входами элементов ИЛИ первой и второй групп, с другими входами элементов И пятой и шестой групп и входами четвертой группы входов элементов И девятой и десятой групп, а входы четвертой группы вхо0дов элементов И второй и четвертой групп и входы третьей группы входов элементов И одиннадцатой и двенадцатой групп являются инверсными адресными входами устройства.

5

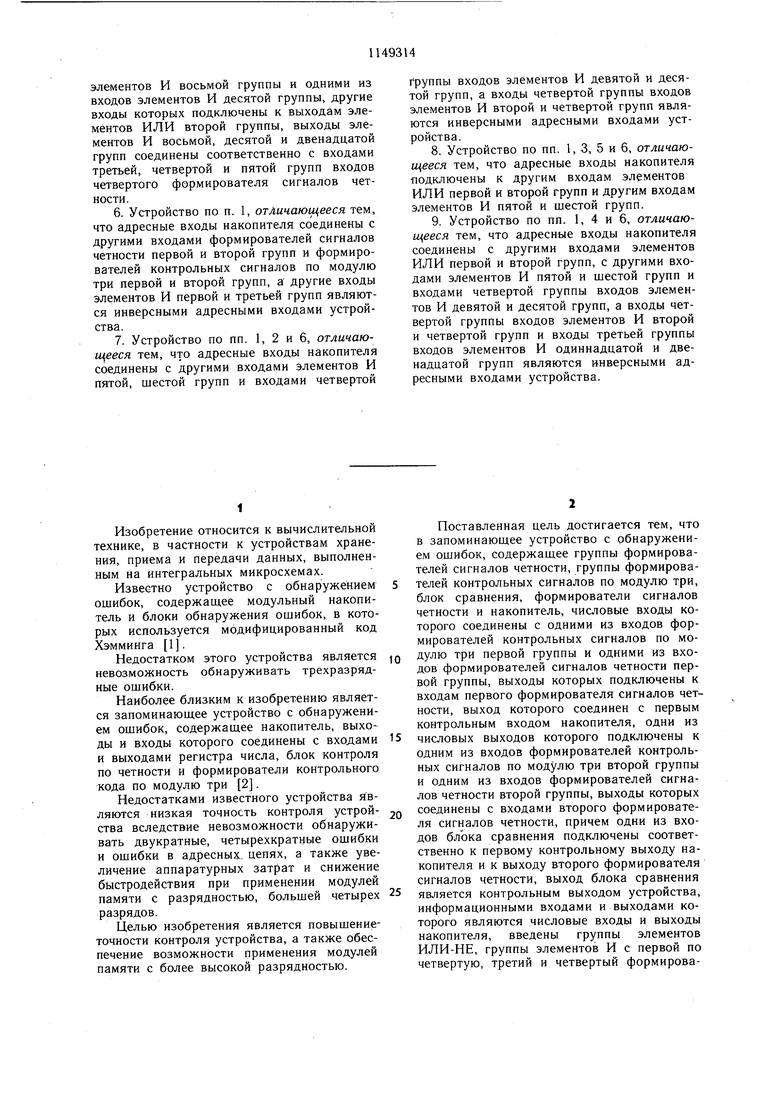

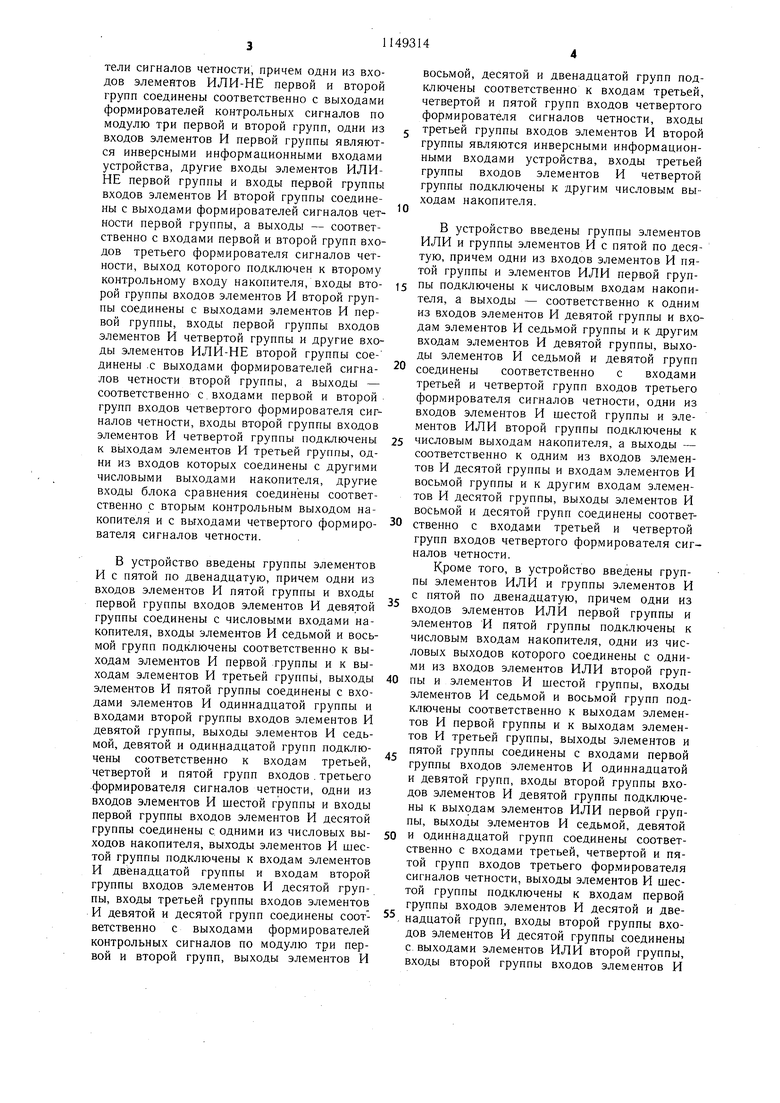

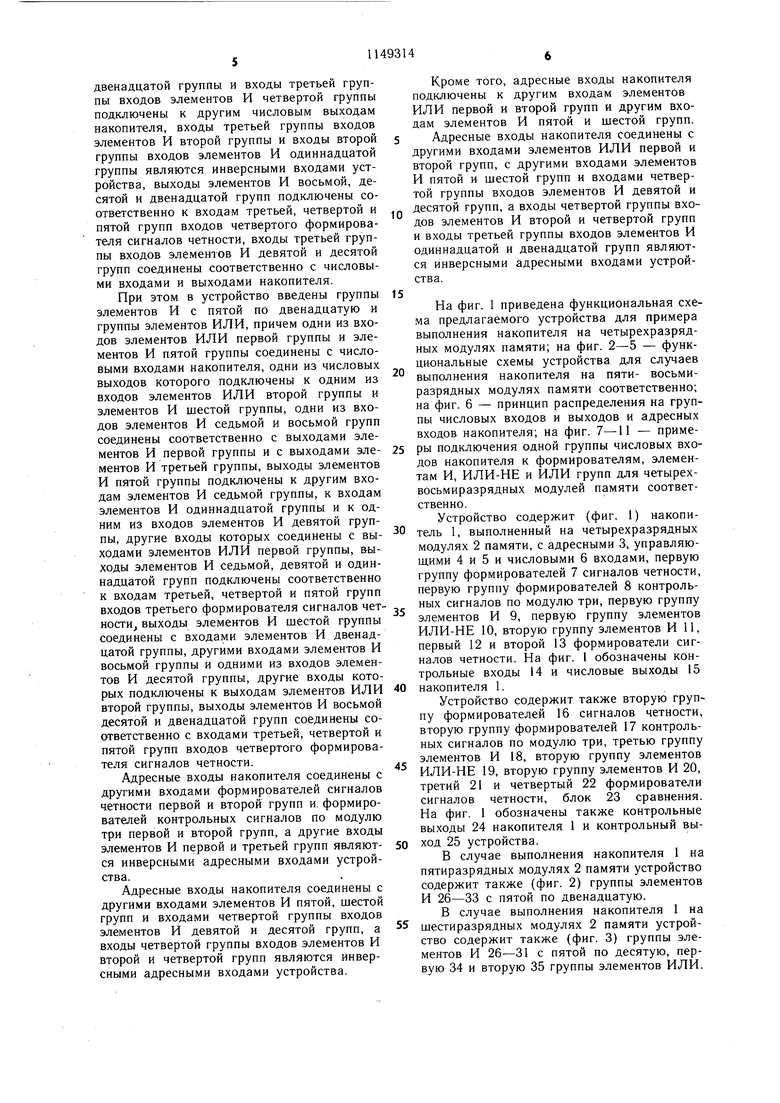

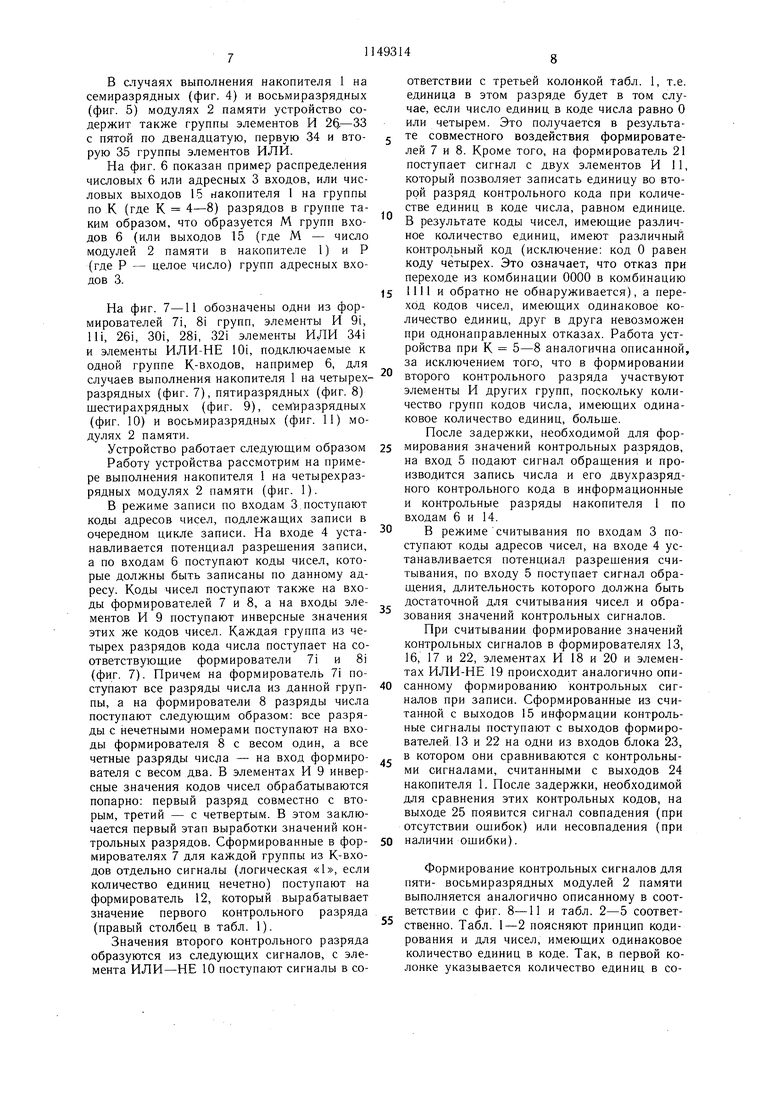

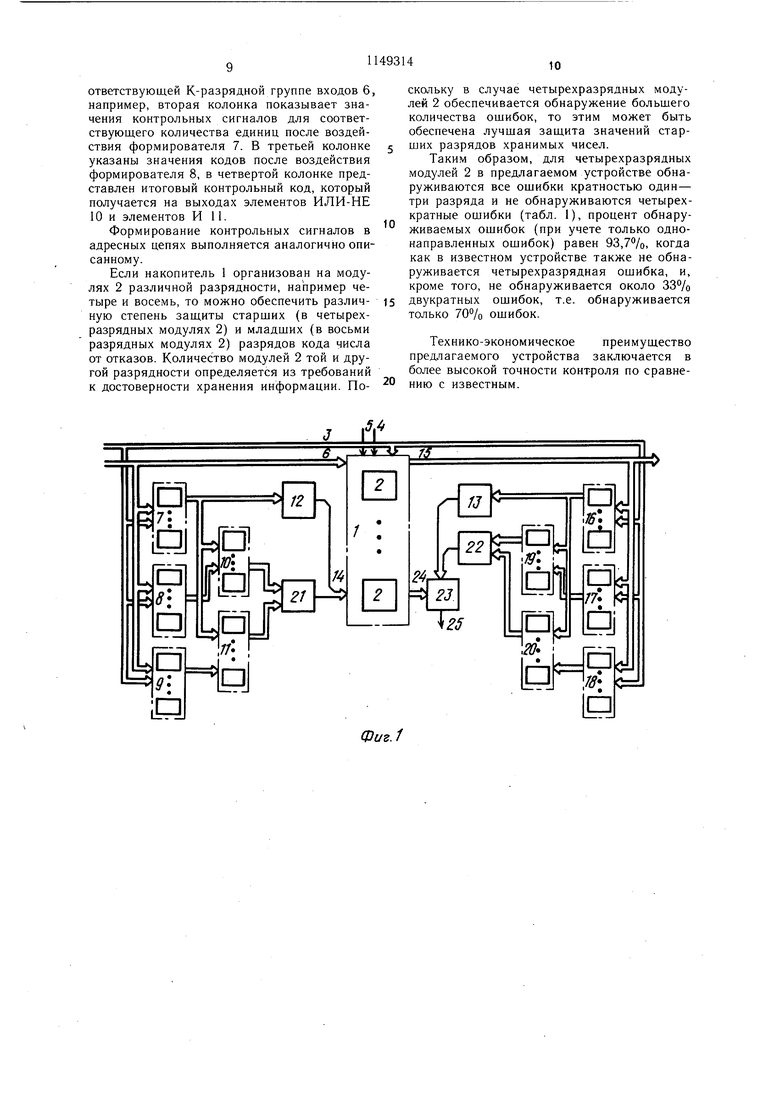

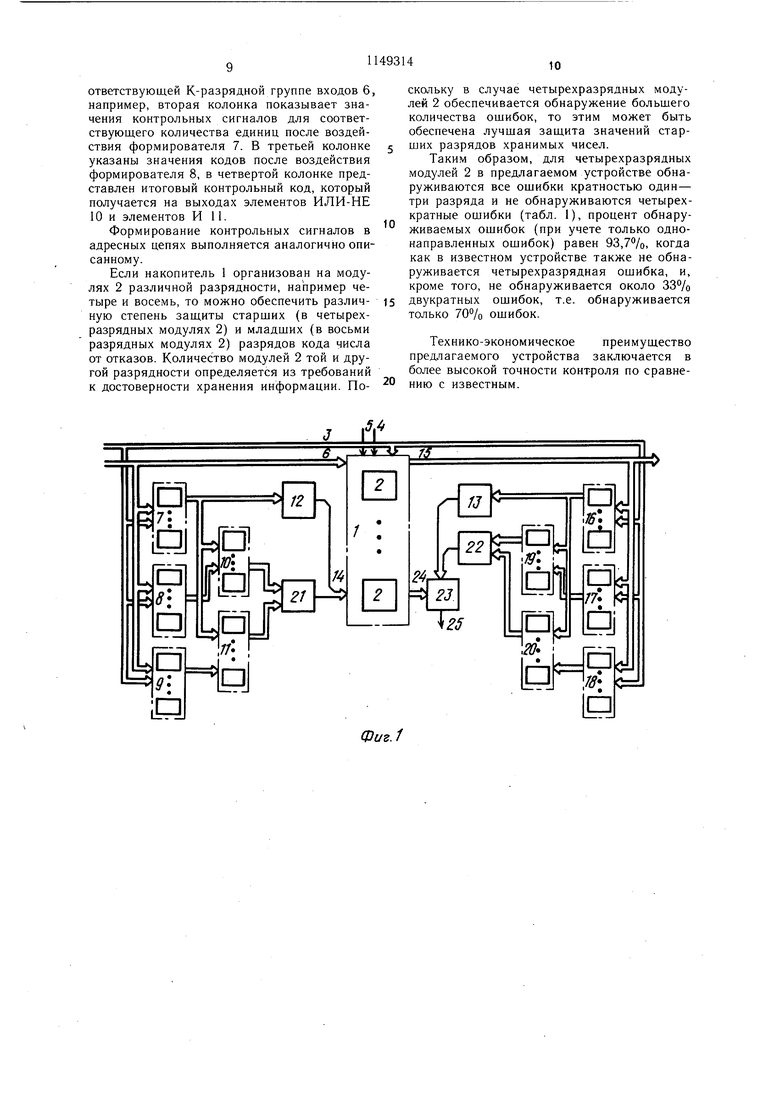

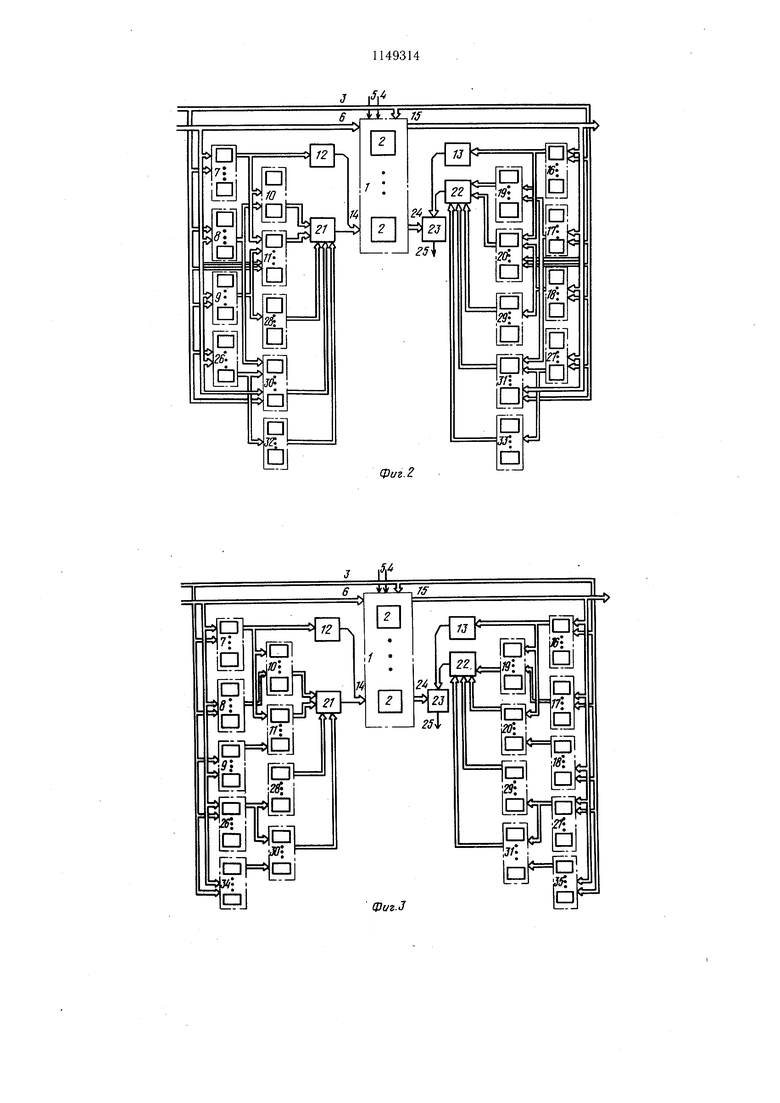

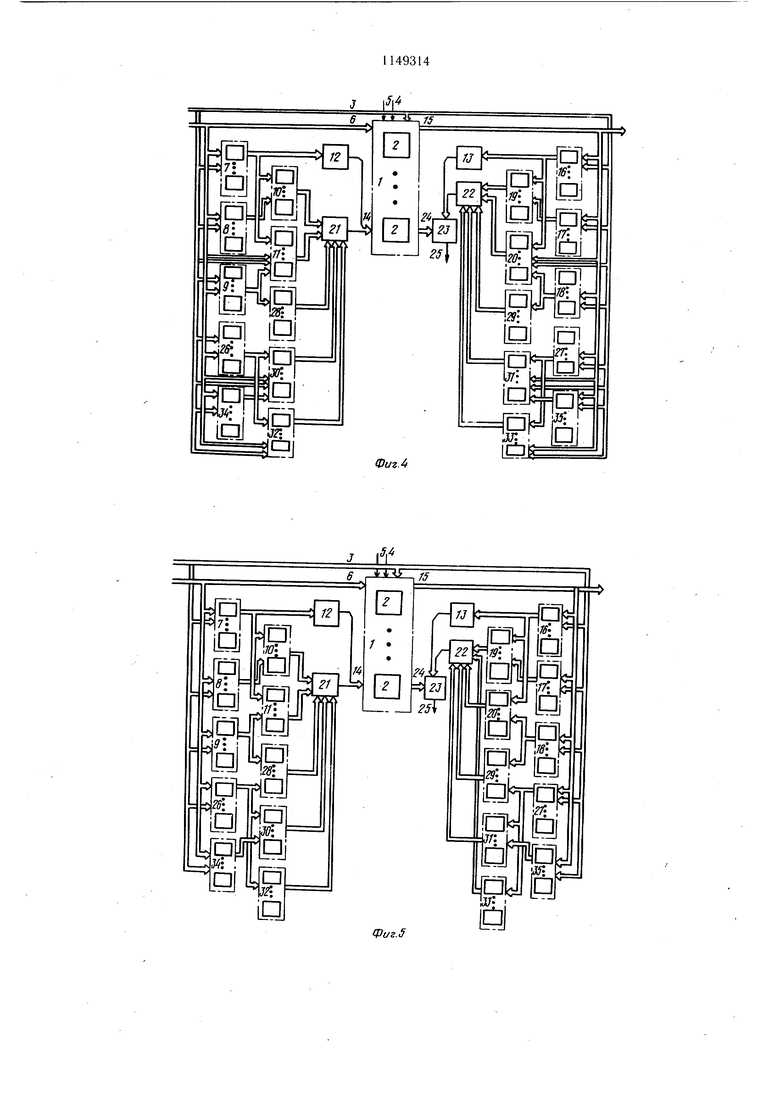

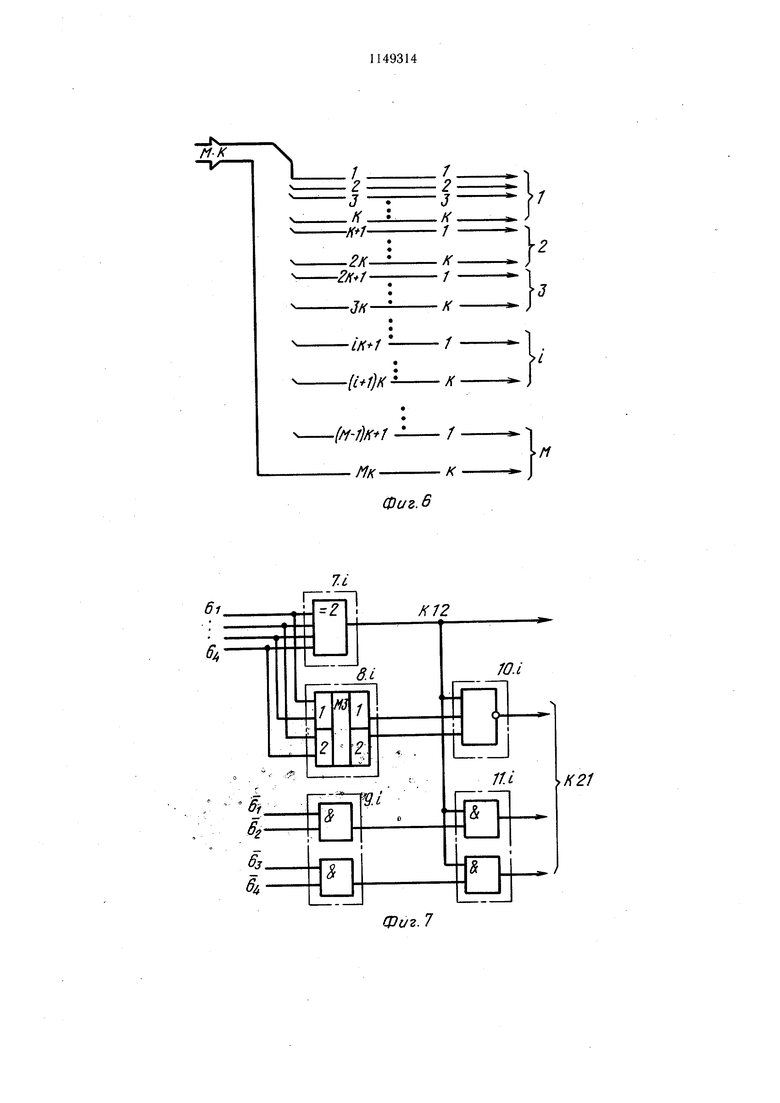

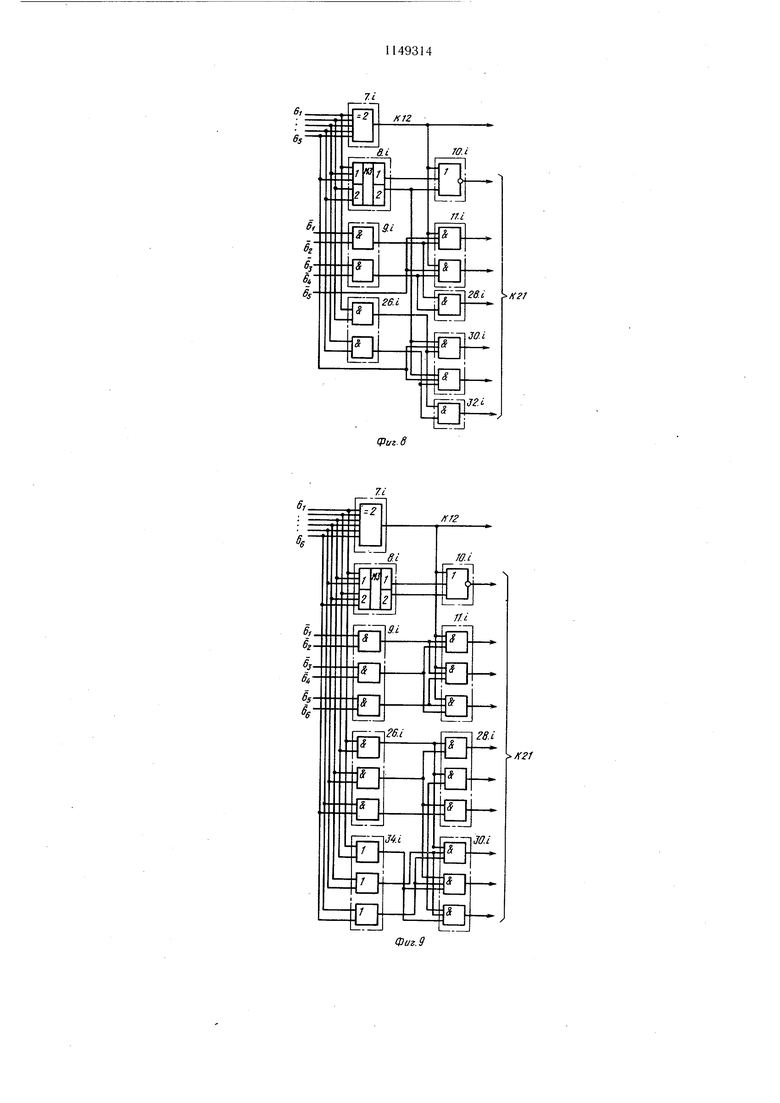

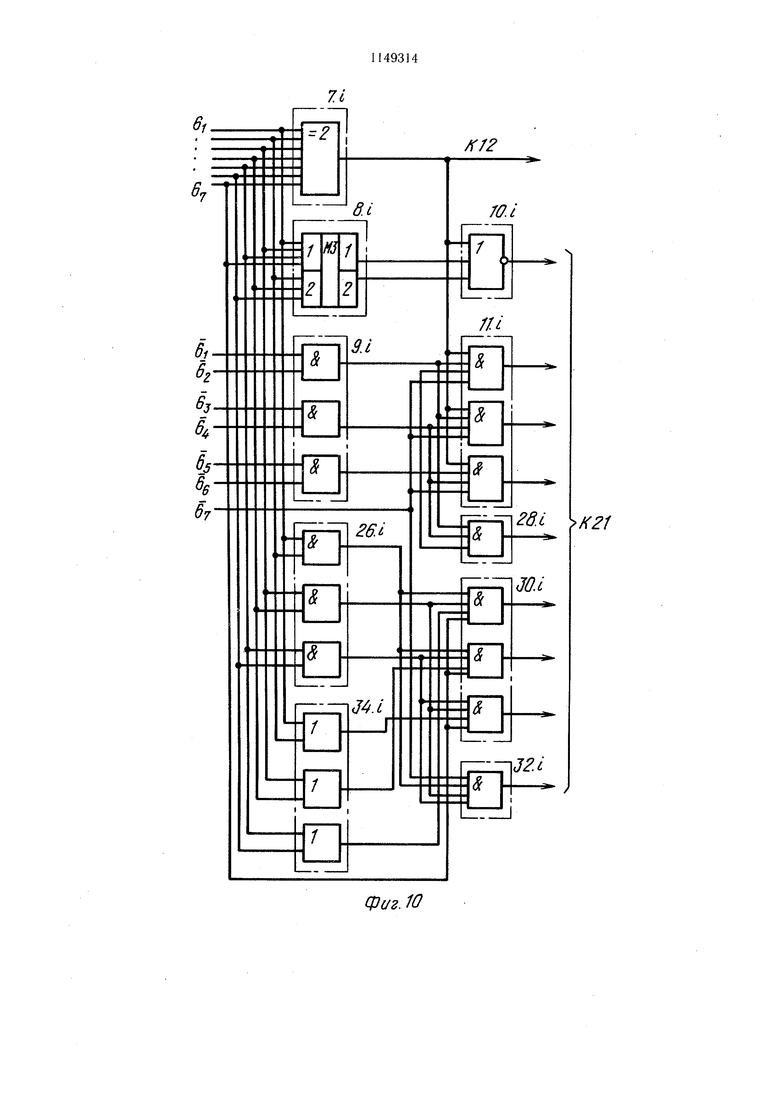

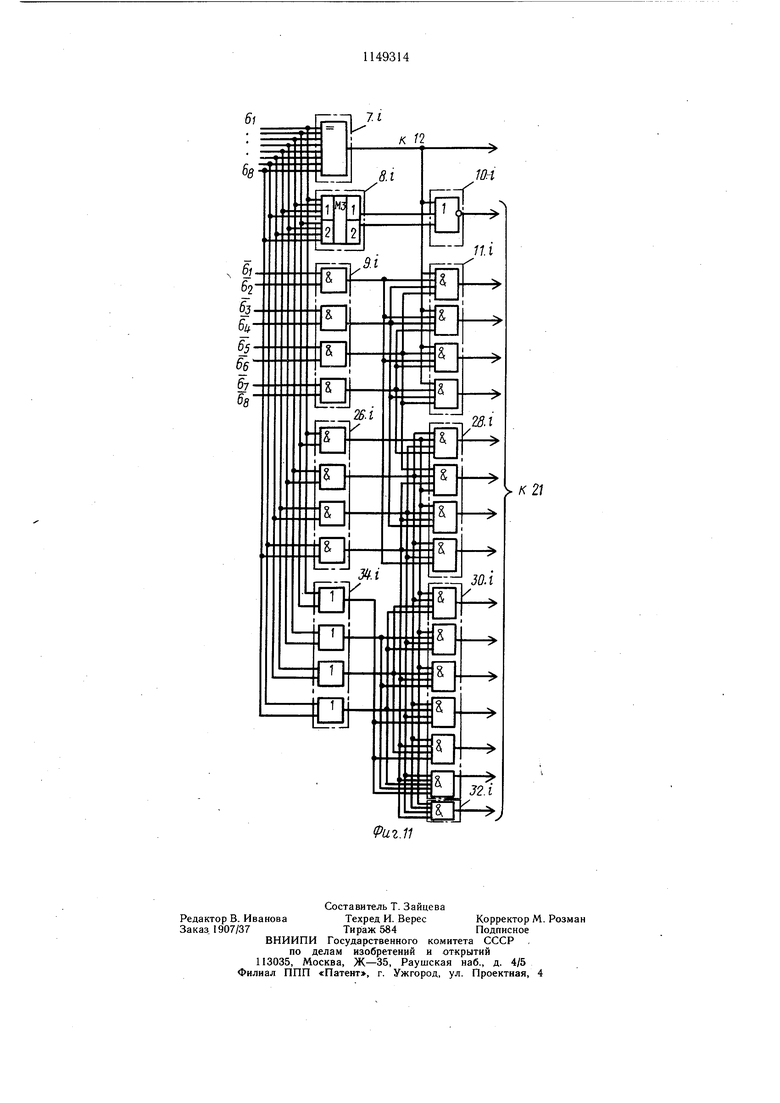

На фиг. 1 приведена функциональная схема предлагаемого устройства для примера выполнения накопителя на четырехразрядных модулях памяти; на фиг. 2-5 - функциональные схемы устройства для случаев

0 выполнения накопителя на пяти- восьмиразрядных модулях памяти соответственно; на фиг. 6 - принцип распределения на группы числовых входов и выходов и адресных входов накопителя; на фиг. 7-11 - примеры подключения одной группы числовых вхо5дов накопителя к формирователям, элементам И, ИЛИ-НЕ и ИЛИ групп для четырехвосьмиразрядных модулей памяти соответственно.

Устройство содержит (фиг. 1) накопи0тель 1, выполненный на четырехразрядных модулях 2 памяти, с адресными 3, управляющими 4 и 5 и числовыми 6 входами, первую группу формирователей 7 сигналов четности, первую группу формирователей 8 контрольных сигналов по модулю три, первую группу

5 элементов И 9, первую группу элементов ИЛИ-НЕ 10, вторую группу элементов И 11, первый 12 и второй 13 формирователи сигналов четности. На фиг. I обозначены контрольные входы 14 и числовые выходы 15 накопителя 1.

0

Устройство содержит также вторую группу формирователей 16 сигналов четности, вторую группу формирователей 17 контрольных сигналов по модулю три, третью группу элементов И 18, вторую группу элементов

5 ИЛИ-НЕ 19, вторую группу элементов И 20, третий 21 и четвертый 22 формирователи сигналов четности, блок 23 сравнения. На фиг. 1 обозначены также контрольные выходы 24 накопителя 1 и контрольный выход 25 устройства.

0

В случае выполнения накопителя 1 на пятиразрядных модулях 2 памяти устройство содержит также (фиг. 2) группы элементов И 26-33 с пятой по двенадцатую.

В случае выполнения накопителя 1 на

5 шестиразрядных модулях 2 памяти устройство содержит также (фиг. 3) группы элементов И 26-31 с пятой по десятую, первую 34 и вторую 35 группы элементов ИЛИ.

В случаях выполнения накопителя 1 на семиразрядных (фиг. 4) и восьмиразрядных (фиг. 5) модулях 2 памяти устройство содержит также группы элементов И с пятой по двенадцатую, первую 34 и вторую 35 группы элементов ИЛИ.

На фиг. 6 показан пример распределения числовых 6 или адресных 3 входов, или числовых выходов 15 накопителя 1 на группы по К (где К 4-8) разрядов в группе таким образом, что образуется М групп входов 6 (или выходов 15 (где М - число модулей 2 памяти в накопителе 1) и Р (где Р - целое число) групп адресных входов 3.

На фиг. 7-11 обозначены одни из формирователей 7i, 8i групп, элементы И 91, Hi, 26i, 30i, 28i, 32i элементы ИЛИ 34i и элементы ИЛИ-НЕ lOi, подключаемые к одной группе К-входов, например 6, для случаев выполнения накопителя 1 на четырехразрядных (фиг. 7), пятиразрядных (фиг. 8) шестирахрядных (фиг. 9), семиразрядных (фиг. 10) и восьмиразрядных (фиг. И) модулях 2 памяти.

Устройство работает следующим образом

Работу устройства рассмотрим на примере выполнения накопителя 1 на четырехразрядных модулях 2 памяти (фиг. 1).

В режиме записи по Входам 3,поступают коды адресов чисел, подлежащих записи в очередном цикле записи. На входе 4 устанавливается потенциал разрещения записи, а по входам 6 поступают коды чисел, которые должны быть записаны по данному адресу. Коды чисел поступают также на входы формирователей 7 и 8, а на входы элементов И 9 поступают инверсные значения этих же кодов чисел. Каждая группа из четырех разрядов кода числа поступает на соответствующие формирователи 7i и 8i (фиг. 7). Причем на формирователь 7i поступают все разряды числа из данной группы, а на формирователи 8 разряды числа поступают следующим образом: все разряды с нечетными номерами поступают на входы формирователя 8 с весом один, а все четные разряды числа - на вход формирователя с весом два. В элементах И 9 инверсные значения кодов чисел обрабатываются попарно: первый разряд совместно с вторым, третий - с четвертым. В этом заключается первый этап выработки значений контрольных разрядов. Сформированные в формирователях 7 для каждой группы из К-входов отдельно сигналы (логическая «1, если количество единиц нечетно) поступают на формирователь 12, который вырабатывает значение первого контрольного разряда (правый столбец в табл. 1).

Значения второго контрольного разряда образуются из следующих сигналов, с элемента ИЛИ-НЕ 10 поступают сигналы в соответствии с третьей колонкой табл. 1, т.е. единица в этом разряде будет в том случае, если число единиц в коде числа равно О или четырем. Это получается в результате совместного воздействия формирователей 7 и 8. Кроме того, на формирователь 21 поступает сигнал с двух элементов И 11 который позволяет записать единицу во второй разряд контрольного кода при количестве единиц в коде числа, равном единице. В результате коды чисел, имеющие различное количество единиц, имеют различный контрольный код (исключение: код О равен коду четырех. Это означает, что отказ при переходе из комбинации 0000 в комбинацию 1111 и обратно не обнаруживается), а переход кодов чисел, имеющих одинаковое количество единиц, друг в друга невозможен при однонаправленных отказах. Работа устройства при К 5-8 аналогична описанной за исключением того, что в формировании второго контрольного разряда участвуют элементы И других групп, поскольку количество групп кодов числа, имеющих одинаковое количество единиц, больше.

После задержки, необходимой для формирования значений контрольных разрядов, на вход 5 подают сигнал обращения и производится запись числа и его двухразрядного контрольного кода в информационные и контрольные разряды накопителя 1 по входам 6 и 14.

В режимесчитывания по входам 3 поступают коды адресов чисел, на входе 4 устанавливается потенциал разрещения считывания, по входу 5 поступает сигнал обращения, длительность которого должна быть достаточной для считывания чисел и образования значений контрольных сигналов.

При считывании формирование значений контрольных сигналов в формирователях 13, 16, 17 и 22, элементах И 18 и 20 и элементах ИЛИ-НЕ 19 происходит аналогично описанному формированию контрольных сигналов при записи. Сформированные из считанной с выходов 15 информации контрольные сигналы поступают с выходов формирователей 13 и 22 на одни из входов блока 23, в котором они сравниваются с контрольными сигналами, считанными с выходов 24 накопителя 1. После задержки, необходимой для сравнения этих контрольных кодов, на выходе 25 появится сигнал совпадения (при отсутствии ощибок) или несовпадения (при наличии ощибки).

Формирование контрольных сигналов для пяти- восьмиразрядных модулей 2 памяти выполняется аналогично описанному в соответствии с фиг. 8-11 и табл. 2-5 соответственно. Табл. 1-2 поясняют принцип кодирования и для чисел, имеющих одинаковое количество единиц в коде. Так, в первой колонке указывается количество единиц в соответствую щей К-разрядной группе входов 6, например, вторая колонка показывает значения контрольных сигналов для соответствующего количества единиц после воздействия формирователя 7. В третьей колонке указаны значения кодов после воздействия формирователя 8, в четвертой колонке представлен итоговый контрольный код, который получается на выходах элементов ИЛИ-НЕ 10 и элементов И 11.

Формирование контрольных сигналов в адресных цепях выполняется аналогично описанному.

Если накопитель 1 организован на модулях 2 различной разрядности, например четыре и восемь, то можно обеспечить различную степень защиты старщих (в четырехразрядных модулях 2) и младщих (в восьми разрядных модулях 2) разрядов кода числа от отказов. Количество модулей 2 той и другой разрядности определяется из требований к достоверности хранения информации. Поскольку в случае четырехразрядных модулей 2 обеспечивается обнаружение больщего количества ошибок, то этим может быть обеспечена лучщая защита значений старших разрядов хранимых чисел.

Таким образом, для четырехразрядных модулей 2 в предлагаемом устройстве обнаруживаются все ошибки кратностью один- три разряда и не обнаруживаются четырехкратные ошибки (табл. 1), процент обнаруживаемых ошибок (при учете только однонаправленных ошибок) равен 93,7%, когда как в известном устройстве также не обнаруживается четырехразрядная ошибка, и, кроме того, не обнаруживается около 33% двукратных ошибок, т.е. обнаруживается только 70% ошибок.

Технико-экономическое преимущество предлагаемого устройства заключается в более высокой точности контроля по сравнению с известным.

Фиг.1

леи

ПР

п

J.

PJ

LJ IXT:

фуг.

Фиг.

ттяг

Г5

пы

и

19 L

Lofi °1ЙР

Р№

JJ

Ld

Cpuz.S

ФигЛ

кгг

К21

Фиг. 10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «Электронная промышленность, 1979, № 5, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Путинцев Н | |||

| Д | |||

| Аппаратурный контроль управляющих цифровых машин | |||

| М., «Советское радио, 1966, с | |||

| Прибор для нанесения на чертеж точек при вычерчивании углов и треугольников | 1922 |

|

SU392A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-24—Подача