группы и к выходам элементов ИЛИ второй группы.

3. Устройство по пп. 1 и 2, отличающееся тем, что входы второй группы элементов ИЛИ-НЕ первой группы, входы третьей группы элементов И пятой группы и входы четвертой группы элементов И третьей группы соединены с числовыми входами накопителя, а входы второй группы элементов ИЛИ-НЕ второй группы, входы третьей группы элементов И шестой группы и входы четвертой группы элементов И четвертой группы подключены к числовым выходам накопителя.

4.Устройство по пп. 1 и 2, отличающееся тем, что адресные входы накопителя соединены с другими входами формирователей сигналов четности первой и второй групп, элементов ИЛИ первой и второй групп и элементов И первой и второй групп.

5.Устройство по пп. 1 3 и 4, Отличающееся тем, что адресные входы накопителя соединены с входами пятой группы элементов И третьей и четвертой групп, входами четвертой группы элементов И пятой и шестой групп и входами третьей группы элементов ИЛИ-НЕ первой и второй групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU894797A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU888203A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, числовые входы которого соединены с одними из входов формирователей сигналов четности первой группы, выходы которых подключены к входам первого формирователя сигналов четности, выход которого соединен с первым контрольным входом накопителя, числовые выходы которого подключены к одним из входов формирователей сигналов четности второй группы, выходы которых соединены с входами второго формирователя сигналов четности, и блок сравнения одни из входов которого подключены соответственно к одному из контрольных выходов накопителя и к выходу второго формирователя сигналов четности, а выход блока сравнения является контрольным выходом устройства, информационными входами и выходами которого являются числовые входы и выходы накопителя, отличающееся тем, что, с целью повышения точности контроля устройства, в него введены третий и четвертый формирователи сигналов четности, группы элементов НЕ, группы элементов ИЛИ-НЕ, группы элементов ИЛИ и группы элементов И с первой по шестую, причем одни из входов элементов ИЛИ первой группы и элементов И первой группы соединены с числовыми входами накопителя, одни из входов элементов ИЛИ второй группы и элементов И второй группы подключены к числовым выходам накопителя, входы элементов НЕ первой группы и входы первой группы элементов И третьей группы соединены с выходами формирователей сигналов четности первой группы, выходы элементов ИЛИ первой группы подключены к входам первой группы элементов ИЛИ-НЕ первой группы и входам второй группы элементов И третьей группы, выходы элементов И первой группы соединены с входами первой группы элементов И пятой группы, выходы элементов НЕ первой группы, элементов ИЛИ-НЕ первой группы и элементов И третьей и пятой групп подключены к входам третьего формирователя сигналов четности, вы§ ход которого соединен с вторым контрольным входом накопителя, выходы формирователей сигналов четности второй группы соединены с входами элементов НЕ второй группы и входами первой группы элементов И четвертой группы, входы второй группы которых и входы первой группы элементов ИЛИ-НЕ второй группы подключены к выходам элементов ИЛИ второй группы, выходы элементов И второй группы соеди нены с входами первой группы элементов И шестой группы, другие входы блока сравнеСО СГ) ния подключены соответственно к второму контрольному выходу накопителя и к выходу четвертого формирователя сигналов четности, входы которого соединены с выходами элементов НЕ второй группы, элементов ИЛИ-НЕ второй группы, элементов И четвертой и шестой групп. 2. Устройство по п. 1, отличающееся тем, что входы третьей группы элементов И третьей и четвертой групп соединены соответственно с выходами элементов И первой группы и с выходами элементов И второй группы, а входы второй группы элементов И пятой и шестой групп подключены соответственно к выходам элементов ИЛИ первой

1

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминаюших устройств, выполняемых на интегральных микросхемах.

Известно устройство, содержашее модульный накопитель и средства обнаружения ошибок на основе модификации кода Хэмминга I.

Недостатками этого устройства являются невозможность обнаруживать трехразрядные ошибки и аппаратурная сложность.

Наиболее близким к изобретению является запоминающее устройство, содержащее накопитель, адресные входы и выходы которого подключены к выходам и входам ключей, другие входы которых соединены с выходами дешифраторов, формирователи сигналов четности, усилители считывания, выходы которых подключены к входам регистра информации, и блок сравнения 2.

Недостатком известного устройства является низкая точность контроля, поскольку в нем обнаруживаются не все ошибки четной кратности в четырехразрядных модулях памяти, отсутствуют контроль адресных цепей, а также не обеспечивается контроль при применении пяти - восьми разрядных модулей памяти.

Цель изобретения - повышение точности контроля за счет обнаружения наиболее вероятных ошибок, а также обеспечение возможности обнаружения адресных ошибок и использования модулей памяти с количеством разрядов от пяти до восьми.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, числовые входы которого соединены с одними из входов формирователей сигналов четности первой группы.

выходы которых подключены к входам первого формирователя сигналов четности, выход которого соединен с первым контрольным входом накопителя, числовые выходы которого подключены к одним из входов формирователей сигналов четности второй группы, выходы которых соединены с входами второго формирователя сигналов четности, и блок сравнения, одни из входов которого подключены соответственнно к

одному из контрольных выходов накопителя и к выходу второго формирователя сигналов четности, а выход блока сравнения является контрольным выходом устройства, информационными входами и выходами ко, торого являются числовые входы и выходы накопителя, введены третий и четвертый формирователи сигналов, четности, группы элементов НЕ, группы элементов ИЛИ-НЕ, группы элементов ИЛИ и группы элементов И с первой по шестую, причем одни из

0 входов элементов ИЛИ первой группы и элементов И первой группы соединены с числовыми входами накопителя, одни из входов элементов, ИЛИ второй группы и элементов И второй группы подключены к

числовым выходам накопителя, входы элементов НЕ первой группы и входы первой группы элементов И третьей группы соединены с выходами формирователей сигналов четности первой группы, выходы элементов ИЛИ первой группы подключены к

0 входам первой группы элементов ИЛИ-НЕ первЬй группы и входам второй группы элементов И третьей группы, выходы элементов И первой группы соединены с входами первой группы элементов И пятой группы, выходы элементов НЕ первой группы, элементов ИЛИ-НЕ первой группы и элементов И третьей и пятой групп подключены к

входам третьего формирователя сигналов, четности, выход которого соединен с вторым контрольным входом накопителя, выходы формирователей сигналов четности и второй группы соединены с входами элементов НЕ второй группы и входами первой группы элементов И четвертой группы, входы второй группы которых и входы первой группы элементов ИЛИ-НЕ второй группы подключены к выходам элементов ИЛИ второй группы, выходы элементов И второй группы соединены с входами первой группы элементов И шестой группы, другие входы блока сравнения подключены соответствеино к второму контрольному выходу накопителя и к выходу четвертого формирователя сигналов четности, входы которого соединены с выходами элементов НЕ второй группы, элементов ИЛИ-НЕ второй группы, элементов И четвертой и шестой

групп.

При этом входы третьей группы элементов И третьей и четвертой групп соединены соответственно с выходами элементов И первой группы и с выходами элементов И второй группы, а входы второй группы элементов И пятой и шестой групп подключены соответственно к выходам элементов ИЛИ первой группы и к выходам элементов ИЛИ второй группы.

Кроме того, входы второй группы элементов ИЛИ-НЕ первой группы, входы третьей группы элементов И пятой группы и входы четвертой группы элементов И третьей группы соединены с числовыми входами накопителя, а входы второй группы элементов ИЛИ-НЕ второй группы, входы третьей группы элементов И шестой группы и входы четвертой группы элементов И четвертой труппы подключены к числовым выходам накопителя.

Адресные входы накопителя соединены с другими входами формирователей сигналов четности первой и второй групп, элементов ИЛИ первой и второй групп и элементов И первой и второй групп.

Адресные входы накопителя соединены с входами пятой группы элементов И третьей и четвертой групп, входами четвертой группы элементов И пятой и шестой групп и входами третьей группы элементов ИЛИНЕ первой и второй групп.

На фиг. приведена функциональная схема предложенного устройства для основного варианта его выполнения; на фиг. 2 -8 функциональные схемы устройства для других вариантов его выполнения.

В основном варианте выполнения предложенное устройство (фиг. 1) содержит накопитель 1, выполненный на четырехразрядных модулях 2 памяти, с. адресными 3, управляюш.ими 4, 5 и числовыми 6 входами, первую группу формирователей 7 сигналов четности, первую группу элементов ИЛИ 8, первую группу элементов И 9, первый формирователь 10 сигналов четности, первую груплу элементов НЕ 11, группы элементов И 12-16 с второй по шестую. Накопитель 1 имеет числовые выходы 17.

Устройство содержит также вторую группу формирователей 18 сигналов четности, вторую группу элементов ИЛИ 19, блок 20 сравнения, второй формирователь 21 сигналов четности, вторую группу элементов НЕ 22, первую 23 и вторую 24 группы элементов ИЛИ-НЕ, третий 25 и четвертый 26 формирователи .сигналов четности. При этом обозначены первые контрольные входы 27 и выход 28 накопителя 1, контрольный выход 29 устройства и второй контрольный вход 30 накопителя 1.

Во втором варианте выполнения устройства (фиг. 2) накопитель 1 может быть выполнен на шести- или восьмиразрядных модулях 2 памяти, а в третьем варианте (фиг. 3) - на пяти- или семиразрядных модулях 2 памяти. Накопитель 1 состоит из М модулей 2 памяти, каждый из блоков 7-9,11 - 16,18,19, 22-24 состоит из аналогичного количества соответствуюших элементов. Это означает, что каждая К-разрядная группа входов 3, 6 и выходов 17 (где К 1,2 3, 4) поступает на входы соответствующего из формирователей 7 и 18, элементов ИЛИ 8 и 19, элементов И 9, 12-16 и элементов ИЛИ-НЕ 23 и 24.

На фиг. 4-8 показаны связи между одним из формирователей 7, одними из элементов И 9, 13 и 15, элементов ИЛИ 8, элементов НЕ 11 и элементов ИЛИ-НЕ 23 для примеров подключения одной группы входов (или входов 3i-3g), состояш.ей из четырех - восьми разрядов соответственно. Аналогично выполнены соединения между формирователем 18; элементами ИЛИ 19, элементами И 12, 14 и 16, элементами НЕ 22 и элементами ИЛИ-НЕ 24 для подключения группы выходов 12.

Устройство работает следуюш,им образом.

Работу устройства рассмотрим для примера четырехразрядных модулей 2 (фиг. 1).

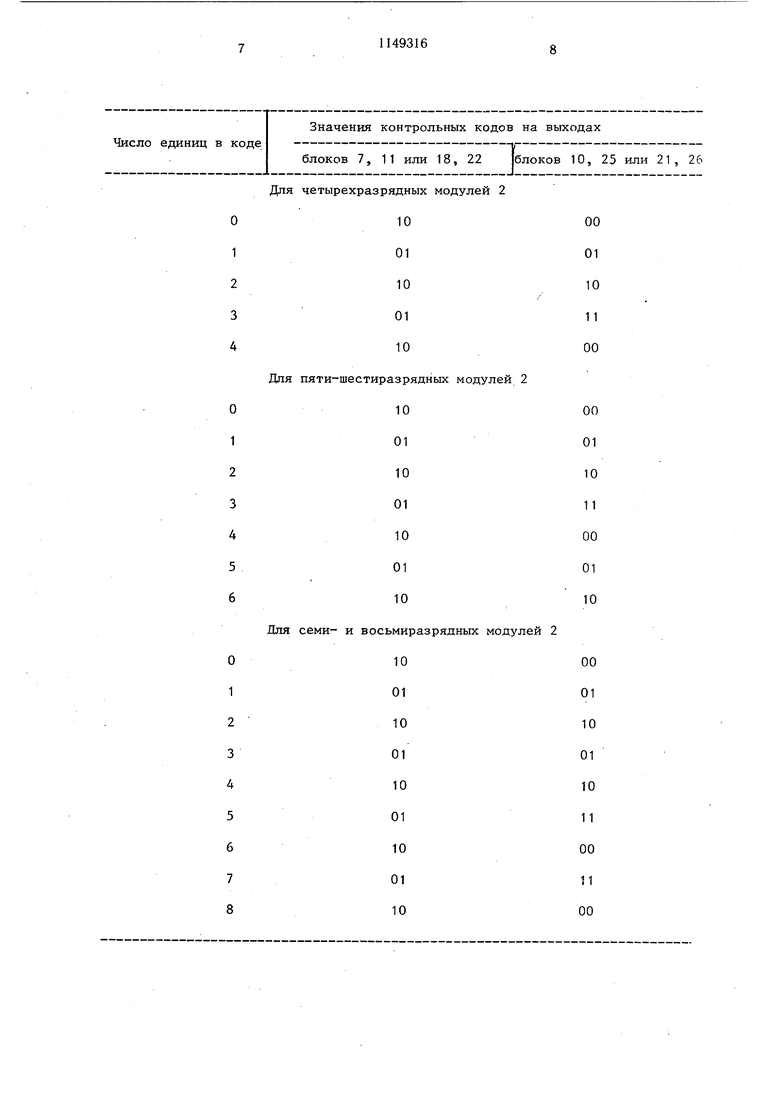

В режиме записи по входам 3 поступают коды адресов чисел, подлежащих записи в очередном цикле записи. На входе 4 устанавливается потенциал разрешения записи, а по входам 6 поступают коды чисел, которые должны быть записаны по данному адресу. Каждая К-разрядная группа входов 3, 6 и выходов 17 обрабатывается независимо от других групп входов 3, 6 и выходов 17, а затем значения контрольных разрядов от каждой группы поступают в формирователи 10 и 25 (при записи), которые определяют значения контрольных разрядов для всех М групп входов 3 и б, которые и записываются в контрольные разряды накопителя 1. Процесс выработки значений контрольных разрядов подразделяется на три этапа. На первом этапе работают один из формирователей 7, два из элементов ИЛИ 8 и два из элементов И 9 для каждой из групп входов (например, 6), в результате вырабатывается признак четности, а также попарные конъюнкции и дизъюнкции, т. е. определяются нулевые и единичные пары разрядов. На втором этапе работает один из элементов НЕ 11, элемент ИЛИ-НЕ 23, элементы И 13 и 15, что позволяет определить полностью нулевой код, полностью единичный код и код, содержащий три единицы в четырехразрядной группе входов 6. После второго этапа контрольный код для каждой четырехразрядной группы входов 6 в отдельности готов, а итоговый код для всего слова, состоящего из М групп входов 6, получается на третьем этапе в формирователях 10 и 25, на выходах которых образуются значения двух контрольных разрядов, которые после подачи сигнала обращения к входу 5 записываются в контрольные разряды накопителя 1 по входам 27 и 30, а по входам 6 записываются значения информационных разрядов. Один разряд (правый в таблице) - это сигнал общей четности всего слова, к которому добавлено значение второго контрольного разряда, вырабатываемое с использованием сигнала четности, конъюнкции и дизъюнкции отдельных разрядов. В результате коды чисел, имеющие различное количество единиц, имеют различный контрольный код (исключение: код числа «О равен коду числа «четыре, т. е. отказ в виде перехода комбинации 0000 в комбинацию 1111 и обратно не обнаруживается), а переход кодов, имеющих одинаковое количество единиц, друг в друга невозможен при однонаправленных отказах. Формирование контрольных разрядов при К от пяти до восьми аналогично описанному, однако в формировании второго контрольного разряда участвует больщее количество логических элементов. Аналогично формируются значения контрольных разрядов для адресных входов 3. В режиме считывания по входам 3 поступают коды адресов, по входу 4 - сигнал разрещения считывания, по входу 5 - сигнал обращения. Формирование значений контрольного кода из значений считанной информации осуществляется аналогично описанному в режиме записи с участием формирователей 18, 21 и 26, элементов ИЛИ 19, элементов И 12, 14 и 16 и элементов ИЛИ-НЕ 24. В блоке 20 происходит сравнение значений контрольных разрядов, поступающих с выходов формирователей 21 и 26, со значениями одноименных разрядов, считанных из накопителя 1 по выходам 28. При отсутствии ошибки в считанной информации на выходе 29 появляется сигнал совпадения, при наличии ощибки - сигнал несовпадения. В таблице приведены значения контрольных кодов соответственно для четырех - восьмиразрядных модулей 2 памяти. Цифра Б первой колонке указывает количество единиц в рассматриваемой К разрядной группе входов 3, 6 или выходов 17. Таким образом, коды, имеющие одинаковое количество единиц в К разрядной группе, собраны в одну строку и им присваивается один и тот же контрольный код. Вторая колонка указывает на значения контрольного кода (два разряда) после вычисления четности, т. е. на выходах формирователей 7 и элементов НЕ 11 (при записи) или на выходах формирователей 18 и элементов НЕ 22 (при считывании). В третьей колонке приведены значения контрольных кодов на выходах формирователей 10 и 25 (при записи) или 21 и 26 (при считывании). Если накопитель 1 организован из модулей 2 различной разрядности, например четыре и восемь разрядов, то можно обеспечить различную степень защиты старщих (четырехразрядные модули) и младщих (восьмиразрядные) разрядов кода числа от отказов. Количество модулей той и другой разрядности определяется из требования к достоверности хранения и считывания информации. Поскольку в четырехразрядных модулях 2 обеспечивается обнаружение больщего количества ошибок, это позволяет повысить достоверность хранения информации. Технико-экономическое преимущество предложенного устройства заключается в более высокой точности контроля, по сравнению с известным устройством, при использовании только двух контрольных разрядов в накопителей.

Для четырехразрядных модулей 2

1000

0101

1010

0111

1000 Для пяти-шестиразрядных модулей 2

1000

0101

1010

0111

1000

0101

1010 Для семи- и восьмиразрядных модулей 2

1000

0101

1010

0101

1010

0111

1000

0111

1000

j т

ffO

n

rrw

,T-W

;

}KZ5

-,

If Ci- S

Or

Pi/g.4

K25

Ф(/г.

6,

/K1Q6i.

r

-15

/(W

tJ

-(

n /

гУ

О

(Риг.7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «Электронная промышленность, 1979, № 5, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| МЕХАНИЧЕСКАЯ ТРАМБОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ИСКУССТВЕННЫХ ЖЕРНОВОВ | 1923 |

|

SU1033A1 |

| Под ред | |||

| В | |||

| А | |||

| Комарницкого | |||

| М., «Машиностроение, 1982, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-24—Подача