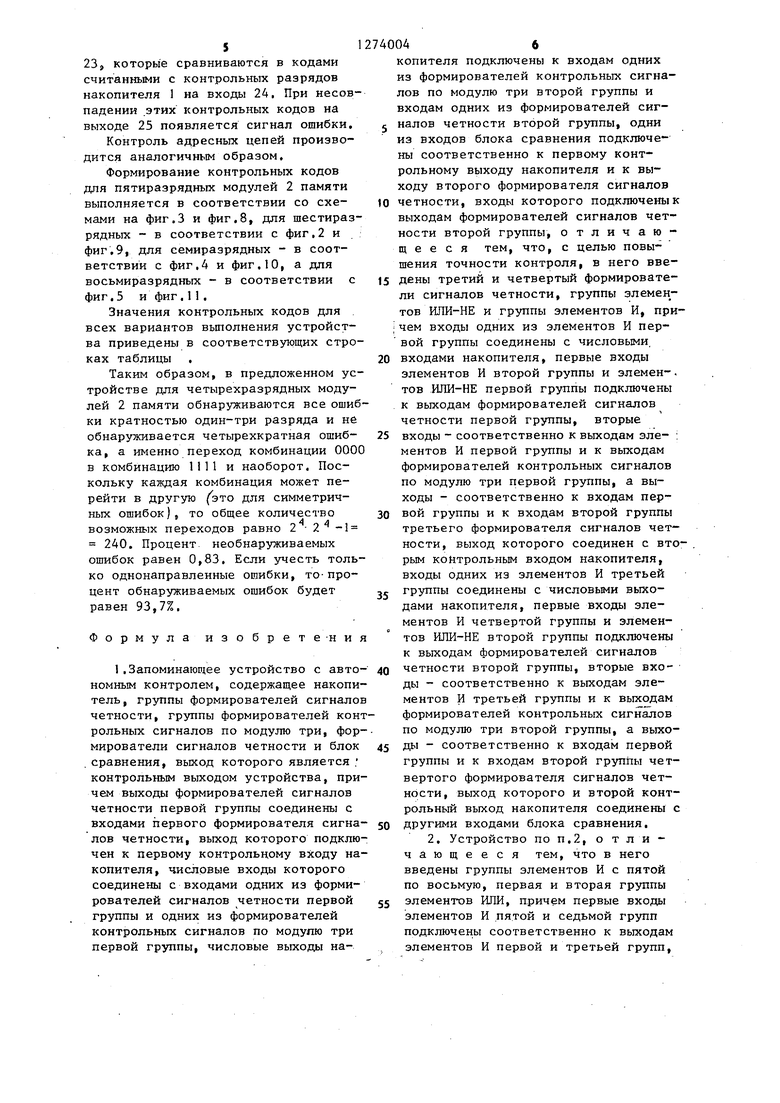

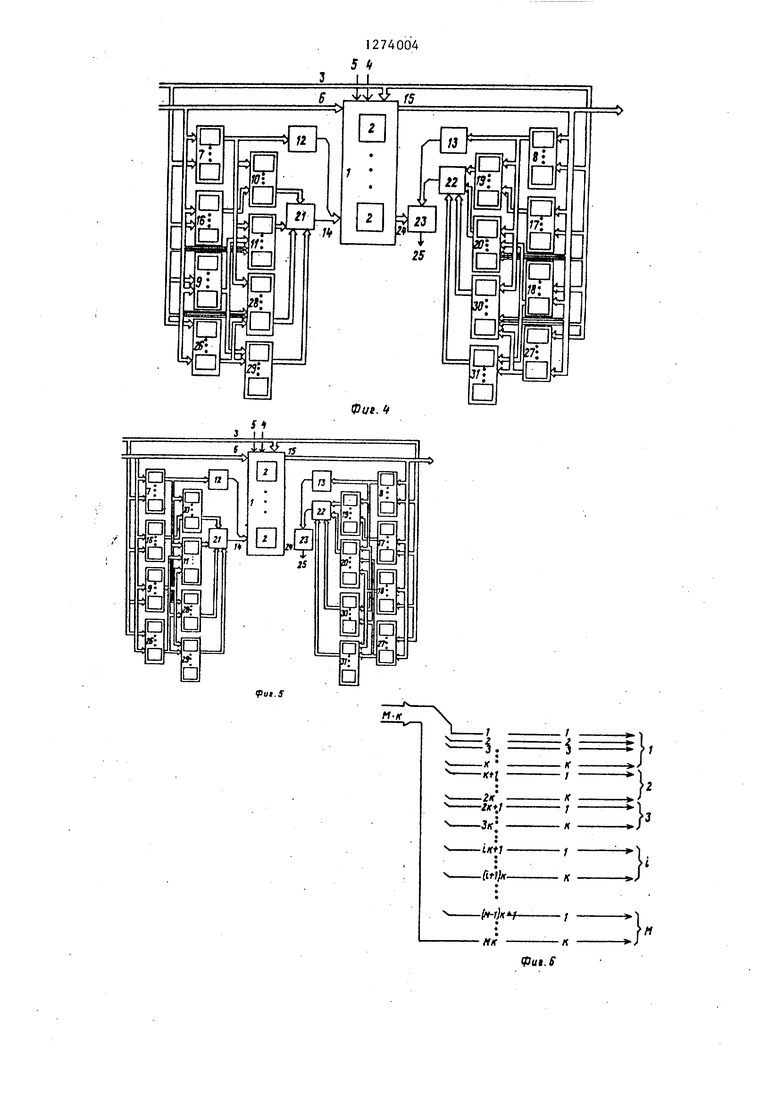

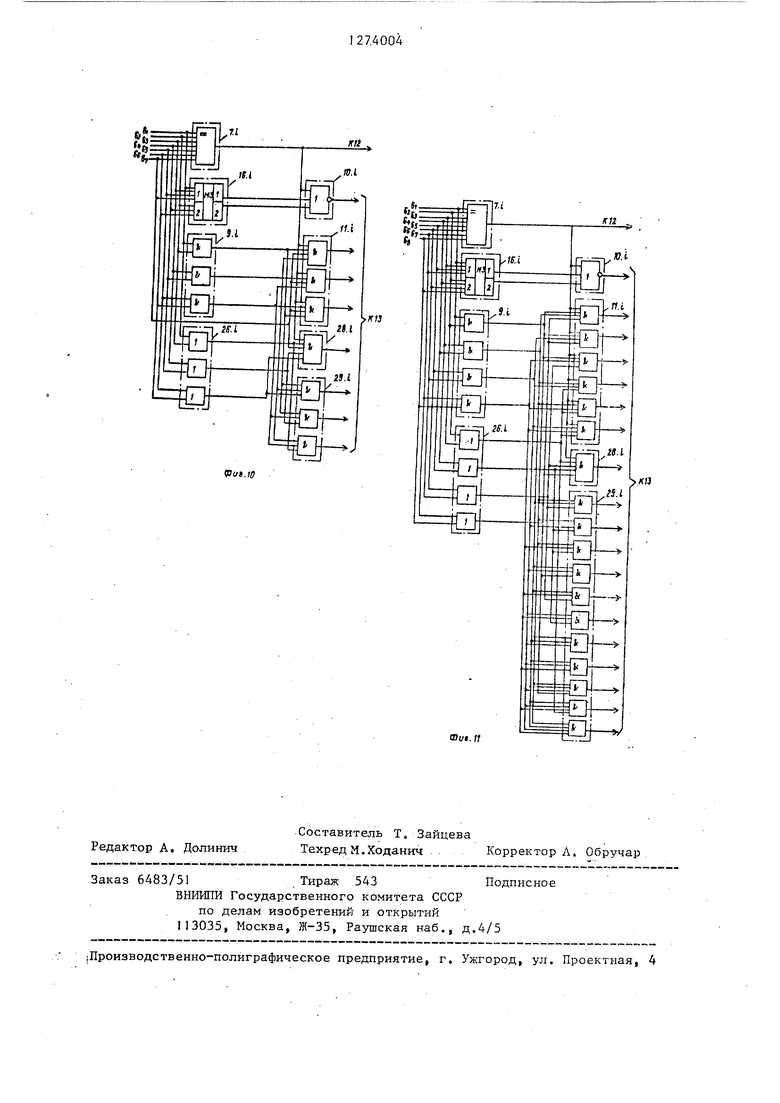

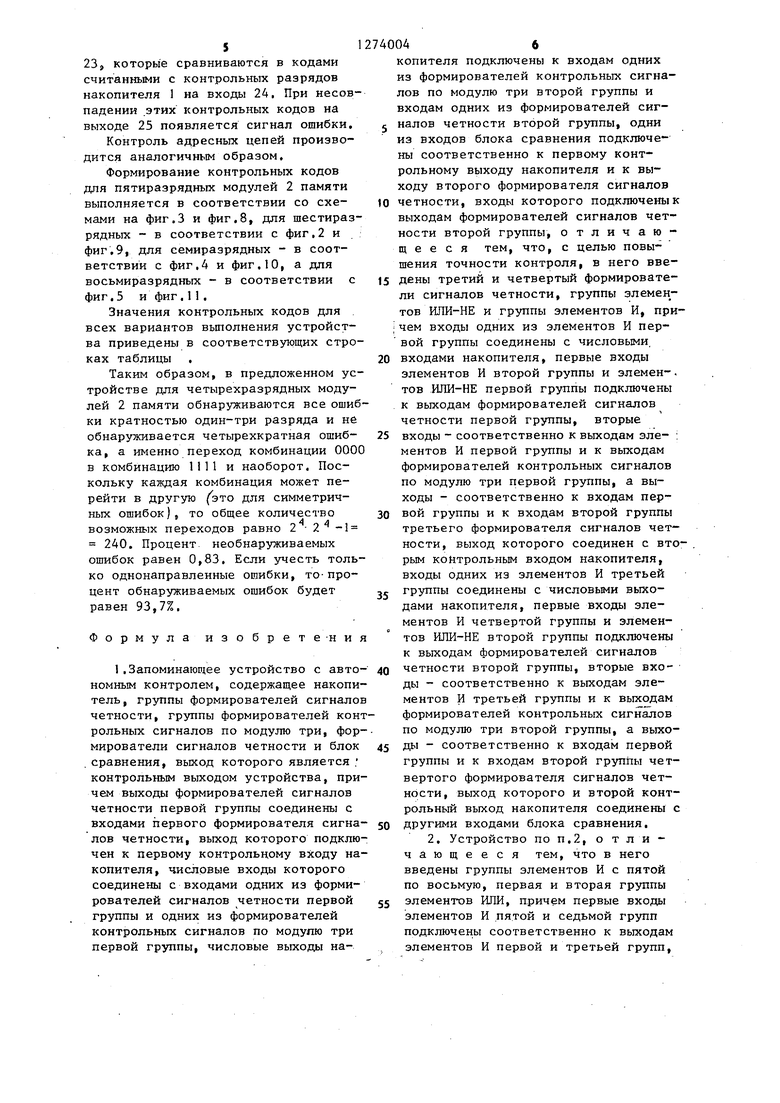

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам с автономным конт ролем, вьтолненным из интегральных микросхем. Цель изобретения - повышение точности контроля. На фиг. представлена функциональ ная схема устройства, вьтолненного из четырехразрядных модулей памяти; на фиг.2 - 5 функциональные схемы вариантов выполнения предложенного устройства соответственно из шестипяти- семи- и восьмиразрядных модулей памяти; на фиг.6 - распределение вхо дов и выходов устройства на группы; на фиг.7 - II - функциональные схемы наиболее предпочтительных вариантов подключения элементов устройства к одной группе входов (или выходов) ус тройства соответственно для четырехвосьмиразрядных групп входов (выходов) , Предложенное устройство содержи (фиг.1) накопитель 1, состоящий из М (где М - целое число К-разрядных, причем ) модулей 2 памяти с адресными 3, управляющими 4,5 и числовыми 6 входами, первую 7 и вторую 8 группы формирователей сигналов четности, первую группу элементов И 9, первую группу элементов ИЛИ-НЕ 10, вто рую группу элементов И 11, первый 1 и второй 13 формирователи сигналов четности. На фиг.1 обозначены контрольные входы 14 и числовые выходы 15 накопителя 1. Устройство содержи также первую 16 и вторую 17 группы формирователей контрольных сигналов по модулю три, третью группу элемен тов И 18, вторую группу элементов ИПИ-НЕ 19, четвертую группу элементов И 20, третий 21 и четвертый 22 формирователи сигналов четности, блок 23 сравнения со входами 24 и выходами 25. Предложенное устройство содержит (см.фиг.2 - 5) накопитель 1, выполненный из М К-разрядных (где ,5, 7 и 8 соответственно) модулей 2 памяти, а также первую 26 и вторую 27 группы элементов ИЛИ и группы элементов И 28-31 с пятой по восьмую. На фиг.6 обозначены М (где М .число модулей 2 памяти в накопителе 1) групп по К (где К - число разрядов модуля 2 памяти) разрядов, на которые распределяются адресные 3 и числовые 6 входы и числовые выходы 15 накопителя. Число формирователей 7,8,.16и 17 элементов И 9,11,18,20, 28-31, элементов ИЛИ-НЕ 10,19 и элементов ИЛИ 26, 27 в каждой группе равно числу М модулей 2 памяти в накопителе 1. На фиг.7 - 11 показаны функциональные схемы подключения одной Кразрядной группы, например, входой 6., (где К от четырех до восьми соответственно) к одним из формирователей 7,, 16,- (где ill), одним из элементов ИЛИ-НЕ 10, элементов И 9, П., 28; и 29- и элементов ИЛИ 26, при этом на формирователь 7 постуцают все разряды входов 6, на элементы И 9, например, первый и второй разряды на один из элементов И 9, а третий и четвертый разряды - на другой элемент И 9 на формирователь 16-, входы b поступают следующим образом : все разряды с нечетными ; номерами поступают на входы с весом один, а все четные - на входы весом Таким образом, каждая К-разрядная группа входов 6 (аналогично входов 3 и выходов 15) является независимой от других групп входов. Предложенное устройство работает ел едующим образом. Работу рассмотрим на примере основного варианта вьшолнения устройства (см.фиг.1 и 7). В режиме записи по входам 3 (см, фиг.1) поступают адресные коды ячеек, в которые будут записываться коды чисел. На входе 4 устанавливается потенциал разрешения записи. Коды чисел поступают на входы 6. Сформированные в формирователях 7 признаки (лог. если кодичество единиц в коде нечетно) поступают на формирователь 12, который вырабатывает значение первого контрольного разряда накопителя 1. Значение второго контрольно го разряда образуется в формирователе 21 из следующих групп сигналов: из элемента ИЛИ-НЕ 10 поступает сигнал в соответствии с третьей колонкой таблицы , т.е. единица присутствует в этом разряде, если число единиц в коде равно О или четырем, а также поступает сигнал с двух элементов И 11, который позволяет записать единицу во второй разряд конт31

рольного кода, если количество еди- . ниц равно трем.

Таблица поясняет принцип формирования контрольных разрядов чисел, имеющих одинаковое количество единиц в коде. В первой.колонке таблицы 1 указывается количество единиц в соответствующей К-разрядной группе входов, вторая колонка показьшает значения контрольных кодов .на выходах формирователя 7 и элемента ИЛИ-НЕ 10 (см. фиг.7),

В третьей колонке таблицы указаны ;значения контрольных кодой на выходах формирователя 16, а в четвертой колонке - контрольный код, который поступает на входы 14.

Продолжение таблицы

01

01

01

10

00

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам с автономным контролем, вьтолненным из интегральных микросхем, Целью изобрете.ния является повышение точности контроля, осуществляемого устройством. Устройство в основном варианте содержит накопитель, состоящий из М (где М-целое число К-разрядных, где ) модулей памяти, с адресными управляющими и численными входами, первую и вторую группы формирователей сигналов четности, первую группу элементов И, первую группу элементов ИЛИНЕ, вторую группу элементов И, пер вьй и второй формирователи сигналов четности. Устройство содержит также первую и вторую группы формирователей контрольных сигналов по модулю три, третью группу элементов И, вторую группу элементов ИЛИ-НЕ, четвертую группу элементов И, третий и четвертый формирователи сигналов четности, блок сравнения. Во-втором-пятом вариантах выполнения устройство содержит накопитель, выполненный из К К-разрядных (где К 6,5,7,8) модулей памяти, а также содержит первую и вторую группы элементов ИЛИ и групо о пы элементов И с пятой по восьмую. В предложенном устройстве для четы(Л рехразрядных модулей памяти обнарус живаются все ошибки кратностью одинтри разряда и не обнаруживается четырехкратная ошибка, а именно переход комбинации 0000 в комбинацию 1111 и наоборот. Поскольку каждая комбинация hS может перейти в другую (это для сим метричных ошибок)., то общее количест4 во возможных переходов равно 2 х X 2 - 1 240. Процент необнаруживаемых ошибок равен 0,83. Если учесть только однонаправленные ошибки, то процент обнаруживаемых ошибок будет равен 93,7%. 8 з.п.ф-лы. 11 ил. 1 табл.

Для пяти, -шестиразрядных, модулей памяти

Для семи- и восьмиразрядных модулей памяти

формирования значений контрольных разрядов, на вход 5 подается разрешающий сигнал и производится запись числа и значения его контрольных размеров в информационные и контрольные разряды накопителя 1. В режиме считывания формирование контрольных разрядов вьшолняется в формирователях 8, 17, 13,22, элементах ИЛИ-НЕ 19 и элементах И 18,20 аналогично описанному вьш1е при записи.

Сформированные значения контрольных разрядов с выходов формирователей 13, 22 поступают на входы блока 23, которые сравниваются в кодами считанными с контрольных разрядов накопителя 1 на входы 24, При несов падении этих контрольных кодов на выходе 25 появляется сигнал ошибки. Контроль адресных цепей производится аналогичным образом. Формирование контрольных кодов для пятиразрядных модулей 2 памяти выполняется в соответствии со схемами на фиг.З и фиг,8, для шестираз рядных - в соответствии с фиг,2 и фиг,9, для семиразрядных - в соответствии с фиг,4 и фиг,10, а для восьмиразрядных - в соответствии с фиг,5 и фиг,11, Значения контрольных кодов для всех вариантов выполнения устройства приведены в соответствующих стро ках таблицы , Таким образом, в предложенном ус тройстве для четырехразрядных модулей 2 памяти обнаруживаются все ошиб ки кратностью один-три разряда и не обнаруживается четырехкратная ошибка, а именно переход комбинации 000 в комбинацию 1111 и наоборот. Поскольку каждая комбинация может перейти в другую (это для симметричных ошибок), то общее количество возможных переходов равно 2 2 -1 240, Процент, необнаруживаемых ошибок равен 0,83, Если учесть толь ко однонаправленные ошибки, то-процент обнаруживаемых ошибок будет равен 93,7%, Формула изобрете-ни 1,Запоминающее устройство с авто номным контролем, содержащее накопи тель, группы формирователей сигнало четности, группы формирователей кон рольных сигналов по модулю три, фор мирователи сигналов четности и блок сравнения, выход которого является , контрольным выходом устройства, при чем выходы формирователей сигналов четности первой группы соединены с входами первого формирователя сигна лов четности, выход которого подклю чен к первому контрольному входу на копителя, числовые входы которого соединены с входами одних из формирователей сигналов четности первой группы и одних из формирователей контрольных сигналов по модулю три первой группы, числовые выходы на46копителя подключены к входам одних из формирователей контрольных сигналов по модулю три второй группы и входам одних из формирователей сигналов четности второй группы, одни из входов блока сравнения подключе ны соответственно к первому контрольному выходу накопителя и к выходу второго формирователя сигналов четности, входы которого подключены к выходам формирователей сигналов четности второй группы, отличающ е е с я тем, что, с целью повышения точности контроля, в него введены третий и четвертый формирователи сигналов четности, группы элемен тов ИЛИ-НЕ и группы элементов И, причем входы одних из элементов И первой группы соединены с числовьии входами накопителя, первые входы элементов И второй группы и элемен-. тов ИЛИ-НЕ первой группы подключены к выходам формирователей сигналов четности первой группы, вторые входы - соответственно к выходам эле- : ментов И первой группы и к выходам формирователей контрольных сигналов по модулю три первой группы, а выходы - соответственно к входам первой группы и к входам второй группы третьего формирователя сигналов четности, выход которого соединен с вторым контрольным входом накопителя, входы одних из элементов И третьей группы соединены с числовьми выходами накопителя, первые входы элементов И четвертой группы и элементов ИЛИ-НЕ второй группы подключены к выходам формирователей сигналов четности второй группы, вторые входы - соответственно к выходам элементов И третьей группы и к выходам формирователей контрольных сигналов по модулю три второй группы, а выходы - соответственно к входам первой группы и к входам второй группы четвертого формирователя сигналов четности, выход которого и второй контрольньм выход накопителя соединены с другими входами блока сравнения, 2, Устройство по п,2, о т л и чающееся тем, что в него введены группы элементов И с пятой по восьмую, первая и вторая группы элементов ИЛИ, причем первые входы элементов И пятой и седьмой групп подключены соответственно к выходам элементов И первой и третьей групп. 71 первые входы элементов И шестой и восьмой групп соединены соответственно с выходами элементов ИЛИ первой и второй групп, входы одних из элементов ИЛИ первой группы подключены к числовым входам накопителя, числовые выходы которого соединены с входами одних из элементов ИЛИ второй группы, выходы элементов И пятой и шестой групп подключены соответственно к входам третьей и четвертой групп третьего формирователя сигналов четности, выходы элементов И седьмого и восьмого групп соединены соответственно с входами третьей и четвертой групп четвертого формирователя сигналов четности. 3. Устройство по ПП.1 и 2, от личЗющееся тем, что вторые входы элементов И шестой группы соединены с числовыми входами накопителя, числовые выходы которого подключены к вторым входам элементов И восьмой группы, 4. Устройство по 11,1, о т л и ч а ю щ е е с я тем, что в него введены первая и вторая группы элементов ИЛИ и группы элементов И с пятой по- вось мую, причем первые входы элементов И пятой и шестой групп подключены к вы ходам элементов ИЛИ первой группы, вторые входы - соответственно к выходам формирователей сигналов четнос ти первой группы и к выходам элементов И первой группы, а выходы - соот ветственно к входам третьей и четвер той грзшп третьего формирователя сиг налов четности, выходы элементов ИЛИ второй группы подключены к первым входам элементов И седьмой и восьмой групп, вторые входы которых соединены соответственно с выходами формирователей сигналов четности второй группы и с выходами элементов И третьей группы, а выходы - соответственно с входами третьей и четвертой групп четвертого формирователя сигналов четности, выходы одних из элементов ИЛИ первой группы и третьи входы элементов И второй и пятой групп подключены к числовым входам накопителя, числовые выходы которого соединены с входами одних из элементов ИЛИ вто.рой группы и третьими входами элементов И четвертой и седьмой групп. 4 5. Устройство по п,1, о т л и ч апервая и вторая группы элементов ИЛИ и группы элементов И с пятой по восьмую, причем выходы элементов ИЛИ первой группы подключены к первым входам элементов И пятой и шестой групп и третьим входам элементов И второй группы, вторые входы элементов И пятой и шестой групп соединены соответственно с выходами формирователей сигналов четности первой группы и с выходами элементов И первой группы, а выходы - соответственно с входами третьей и четвертой групп третьего формирователя сигналов четности, выходы элементов ИЛИ второй группы подключены к первым входам элементов И седьмой и восьмой групп и третьим входам элементов И четвертой группы, вторые входы элементов И седьмой и восьмой групп соединены соответственно с выходами формирователей сигналов четности второй группы и с выходами элементов И третьей группы, а выходы - соответственно со входами третьей и четвертой групп четвертого формирователя сигналов чет-. ности, входы одних из элементов ИЛИ первой и второй групп подключены соответственно к числовым входам и к числовым выходам накопителя, 6,Устройство по п.1, о т л и ч аю щ е е с я тем, что адресные входы накопителя соединены со вxoдa и других формирователей сигналов четности первой и второй групп, других формирователей контрольных сигналов по модулю три и других элементов К первой и третьей групп, 7,Устройство по пп,1,2,5 и 6, отличающееся тем, что входы других элементов ИЛИ первой и второй групп соединены с адресными входами накопителя, 8,Устройство по пп,1,3,6 и 7, отличающееся тем, что адресные входы накопителя подключены к третьим входам элементов И шестой и восьмой групп, 9,Устройство по пп,1,4,6 и 7, о е с я тем, что адресные входы накопителя соединены с четвертыми входами элементов И второй, четвертой, пятой и седьмой групп, 5 «

r

sli

Фиг. 7

| Электроника, 1982, № 11, с.54-59 | |||

| Путинцев Н.Д., Аппаратурный контроль з равляющих цифровых вьиислительных машин, М.: Сов.радио, 1966, | |||

| Ситценабивная машина | 1922 |

|

SU391A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-11-30—Публикация

1983-11-24—Подача