2.Устройство по п. 1, отличающееся тем, что третьи входы одних из элементов И первой и второй групп подключены соответственно к числовым входам и к числовым выходам накопителя.

3.Устройство по п. 1, отличающееся тем, что в него введены третий и четвертый блоки свертки, одни из входов которых соединены соответственно с числовыми входами и с числовыми выходами накопителя, а выходы подключены к третьим входам одних из элементов И первой и второй групп соответственно.

4.Устройство по пп. 1 и 3, отличающееся тем, что четвертые входы одних из элементов И первой и второй групп соединены соответственно с числовыми входами и с числовыми выходами накопителя.

5.Устройство по пп. 1 и 3, отличающееся тем, что в него введены первая и вторая группы элементов ИЛИ, одни из входов которых подключены соответственно к числовым входам и к числовым выходам накопителя, причем четвертые входы одних из элементов И первой группы соединены соответственно с выходами элементов ИЛИ первой группы и с выходами третьего блока свертки, а четвертые выходы элементов И второй группы - соответственно с выходами элементов ИЛИ второй группы и с выходами четвертого блока свертки.

6.Устройство по п. 1, отличающееся тем, что адресные входы накопителя подключены к другим входаМ первого и второго формирователей сигналов четности, первого и второго блоков свертки.

7.Устройство по пп. 1, 2 и 6, отличающееся тем, что адресные входы накопителя соединены с входами других элементов И первой и второй групп.

8.Устройство по пп. 1, 3 и 6, отличающееся тем, что адресные входы накопителя подключены к другим входам третьего и четвертого блоков свертки.

9.Устройство по пп. 1, 4 и 8, отличающееся тем, что адресные входы накопителя соединены с входами других элементов И первой и второй групп.

10.Устройство по пп. 1, 5 и 8, отличающееся тем, что адресные входы накопителя подключены к другим входам элементов ИЛИ первой и второй групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU894797A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU888203A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ НАИБОЛЕЕ ВЕРОЯТНЫХ ОШИБОК, содержащее формирователи сигналов четности, блок сравнения и накопитель, числовые входы которого являются информационными входами устройства и соединены с одними из входов первого формирователя сигналов четности, выход которого подключен к первому контрольному входу накопителя, причем одни из входов блока сравнения соединены соответственно с первым контрольным выходом накопителя и с выходом второго формирователя сигналов четности, одни из входов которого подключены к числовым выходам накопнтеля, выход блока сравнения и числовые выходы накопителя являются соответственно контрольным и информационными выходами устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены третий и четвертый формирователи сигналов четности, блоки свертки и группы элементов И, причем одни из входов первого блока свертки соединены с числовыми входами накопителя, числовые выходы которого подключены к одним из входов второго блока свертки, выходы первого блока свертки соединены соответственно с первыми и вторыми входами одних из элементов И первой группы, а выходы второго блока g свертки - соответственно с первыми и вторыми входами одних из элементов И второй группы, выходы элементов И первой группы подключены к входам третьего формирователя сигналов четности, выход которого соединен с вторым контрольным входом накопителя, выходы элементов И второй группы подключены к входам четвертого-формирователя сигналов четности, выход которого и 4ib второй контрольный выход накопителя со динены с другими входами блока сравнения. оо

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, выполняемым на интегральных микросхемах.

Известно устройство с обнаружением наиболее вероятных ошибок, содержащее модульный накопитель и средства обнаружения ощибок на основе модификации кода Хэмминга 1.

Недостатком этого устройства является невысокая достоверность контроля.

Наиболее близким к изобретению является запоминающее устройство с обнаружением наиболее вероятных ошибок, содержащее накопитель, формирователи сигналов четности, усилители считывания, входы которых подключены к выходам накопителя, а выходы - к входам информационного регистра, дещифраторы адреса, адресные ключи и блок сравнения, один из входов которого подключен к контрольным выходам информационного регистра 2.

Недостатком известного устройства является низкая точность контроля, так как в нем не обнаруживаются ощибки четной кратности и не контролируются адресные цепи.

Цель изобретения - повышение точности контроля, а также обеспечение возможности обнаружения адресных ошибок и использования модулей памяти с числом разрядов от пяти до восьми.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением наиболее вероятных ощибок, содержащее формирователи сигналов четности, блок

сравнения и накопитель, числовые входы которого являются информационными входами устройства и соединены с одними из входов первого формирователя сигналов четности, выход которого подключен к первому контрольному входу накопителя, причем одни из входов блока сравнения соединены соответственно с первым контрольным выходом накопителя и с выходом второго формирователя сигналов четности, одни из входов которого подключены к числовым выходам накопителя, выход блока сравнения и числовые выходы накопителя являются соответственно контрольным и информационными выходами устройства, введены третий и четвертый формирователи сигналов четности, блоки свертки и группы элементов И,

0 причем одни из входов первого блока свертки соединены с числовыми входами накопителя, числовые выходы которого подключены к одним из входов второго блока свертки, выходы первого блока свертки соединены

соответственно с первыми и вторыми входами одних из элементов И первой группы, а выходы второго блока свертки - соответстренно с первыми и вторыми входами одних из элементов И второй группы, выходы элементов И первой группы подключены к входам третьего формирователя сигналов четности, выход которого соединен с вторым контрольным входом накопителя, выходы элементов И второй группы подключены к входам четвертого формирователя сигналов четности, выход которого и второй контрольный выход накопителя соединены с другими входами блока сравнения.

Третьи входы одних из элементов И первой и второй групп подключены соответственно к числовым входам и к числовым выходам накопителя.

При этом в устройство введены третий и четвертый блоки свертки, одни из входов которых соединены соответственно с числовыми входами и с числовыми выходами накопителя, а выходы подключены к третьим входам одних из элементов И первой и второй групп соответственно.

Четвертые входы одних из элементов И первой и второй групп соединены соответственно с числовыми входами и с числовыми выходами накопителя.

Кроме того, в устройство введены первая и вторая группы элементов ИЛИ, одни из входов которых подключены соответственно к числовым входам и к числовым выходам накопителя, причем четвертые входы одних из элементов И первой группы соединены соответственно с выходами элементов ИЛИ первой группы и с выходами третьего блока свертки, а четвертые выходы элементов И второй группы - соответственно с выходами элементов ИЛИ второй группы и с выходами четвертого блока свертки.

Адресные входы накопителя подключены к другим входам первого и второго формирователей сигналов четности, первого и второго блоков свертки.

Адресные входы накопителя соединены с входами других элементов И первой и второй групп.

Адресные входы накопителя подключены к другим входам третьего и четвертого блоков свертки.

Адресные входы накопителя соединены с входами других элементов И первой и второй групп.

Адресные входы накопителя подключены к другим входам элементов ИЛИ первой и второй групп.

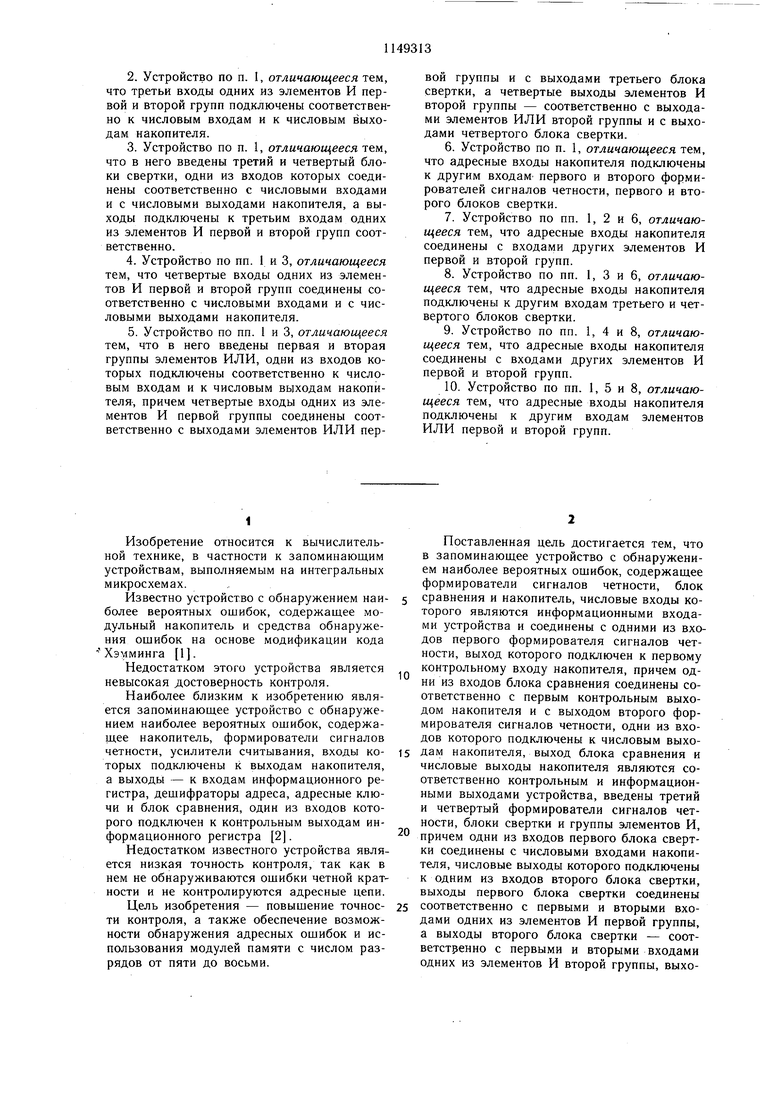

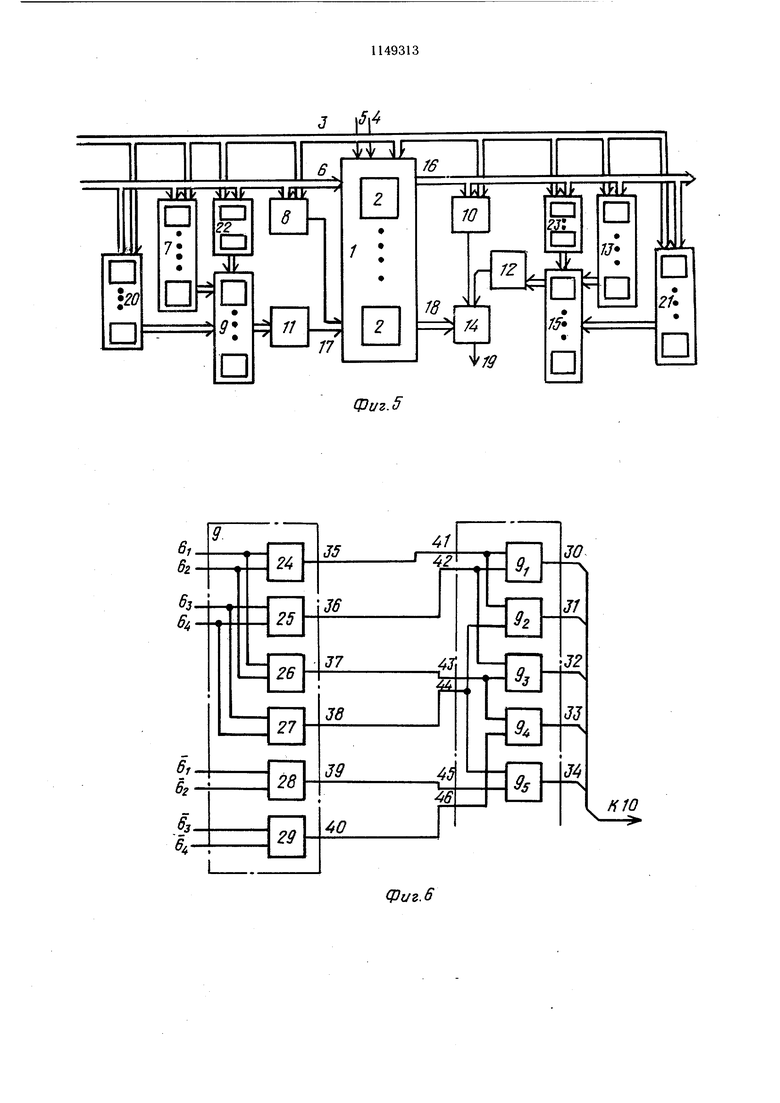

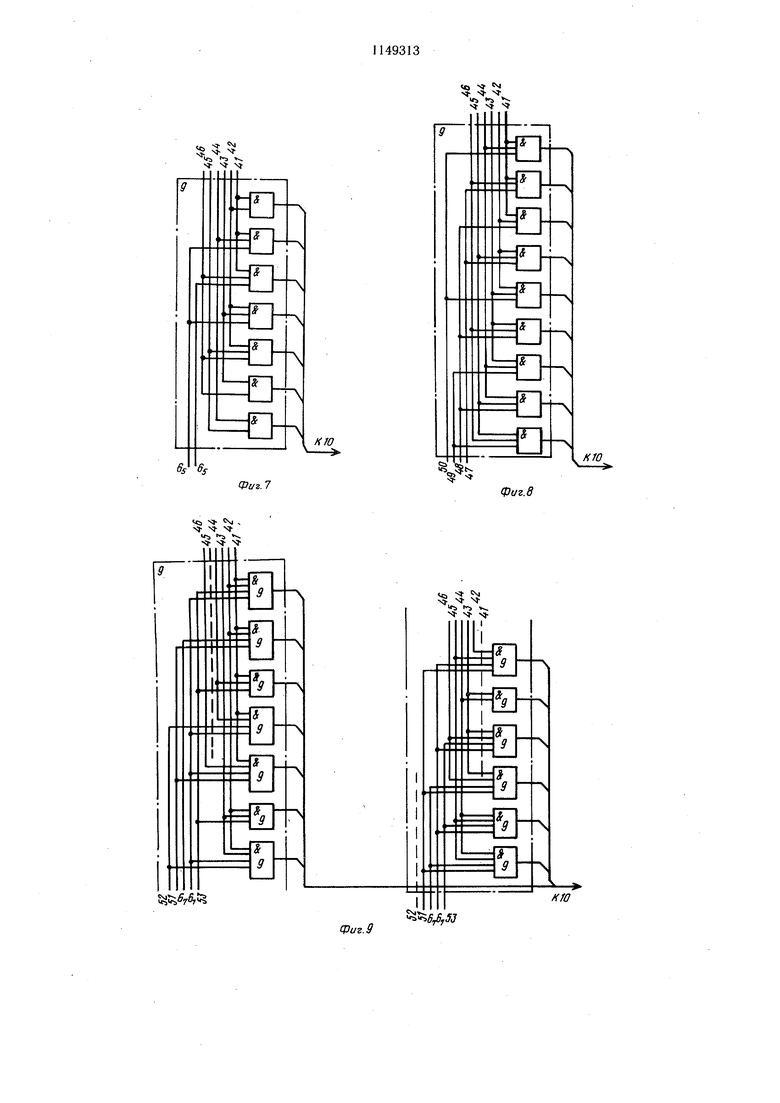

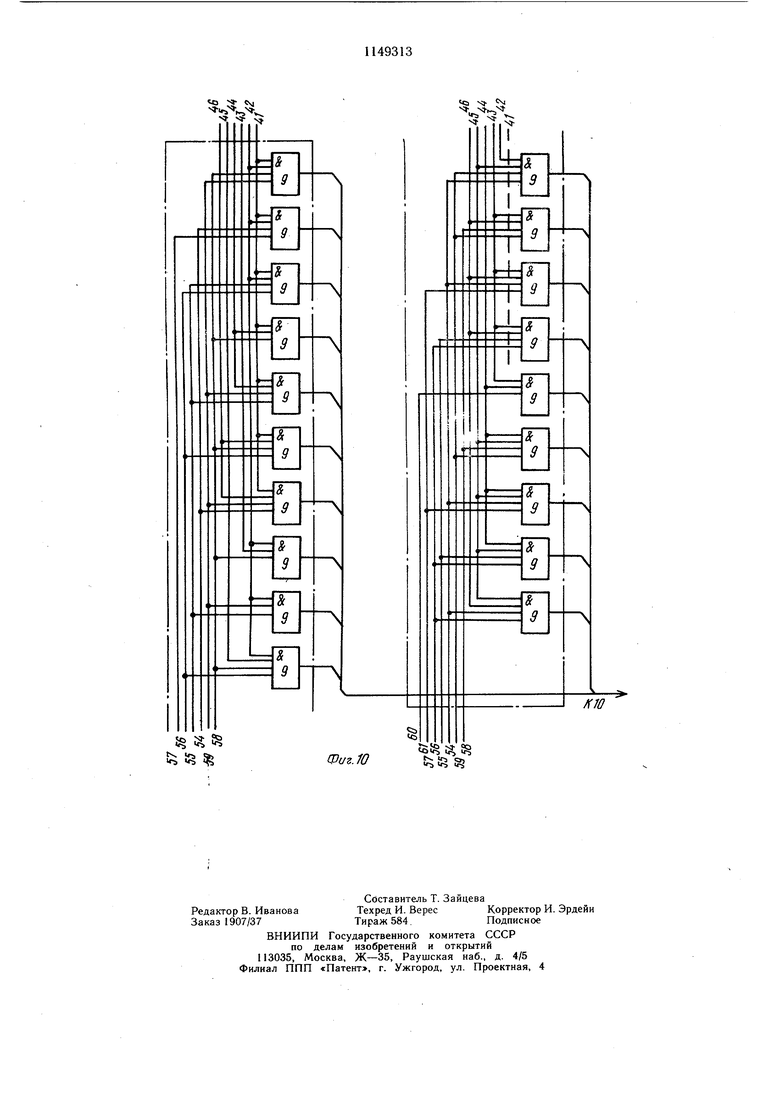

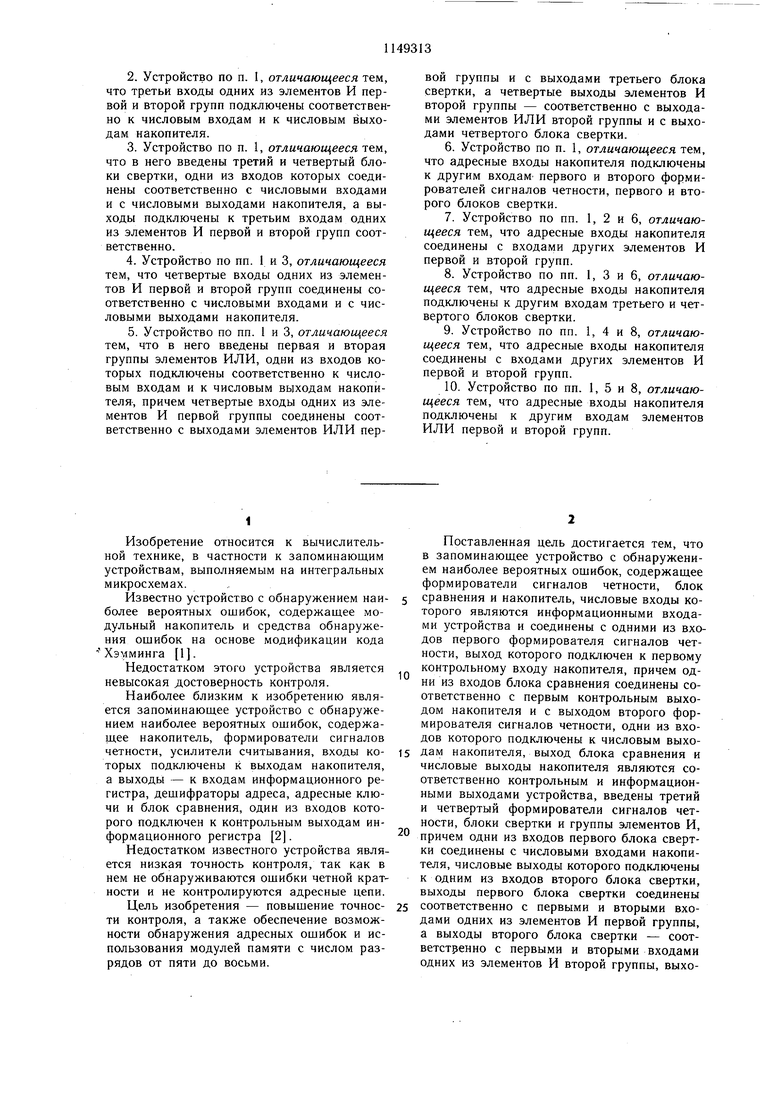

На фиг. I изображена функциональная схема предлагаемого устройства в первом варианте его выполнения; на фиг. 2-5 - то же, другие варианты выполнения; на фиг. 6 - функциональная схема наиболее предпочтительного варианта выполнения первого (второго) блока свертки и его соединения с элементами И первой (второй) группы для первого варианта выполнения; на фиг. 7-10 - наиболее предпочтительные варианты соединения элементов И первой

(второй) групп для других вариантов выполнения устройства.

Предлагаемое устройство в первом и втором вариантах его выполнения содержит г (фиг. 1 и 2) накопитель 1, выполненный на модулях 2 памяти, с адресными 3, управляющими 4 и 5 и числовыми 6 входами, первый блок 7 свертки, первый формирователь 8 сигналов четности, первую группу элементов И 9, формирователи 10-12 сигналов

четности с второго по четвертый, второй блок 13 свертки, блок 14 сравнения и вторую группу элементов И 15.

На фиг. 1-5 обозначены числовые выходы 16, контрольные входы 17 и выходы 18

5 накопителя и контрольный выход 19 устройства.

В первом варианте выполнения устройства накопитель 1 выполнен на четырехразрядных модулях 2 памяти, а во втором варианте - на пятиразрядных модулях 2

0 памяти. В третьем, четвертом и пятом вариантах выполнения устройства накопитель 1 выполнен соответственно на шести-, семи- и восьмиразрядных модулях 2 памяти.

5 В третьем и четвертом вариантах выполнения устройство содержит также (фиг. 3 и 4) третий 20 и четвертый 21 блоки свертки.

В пятом варианте выполнения устройство содержит также (фиг. 5) первую 22 и вто0 рую 23 группы элементов ИЛИ.

Накопитель 1 состоит из М модулей 2 памяти с числом разрядов К (где К имеет значения от четырех до восьми). В соответствии с этим входы 6 и 3 и выходы 16 накопителя 1 распределяются на М групп по

5 к разрядов в каждой группе, которые подключаются к входам соответствующих групп элементов в блоках 7, 13, 20 и 21 свертки, элементов И 9 и 15 и ачементов ИЛИ 22 и 23 в соответствии с фиг. 1 -10.

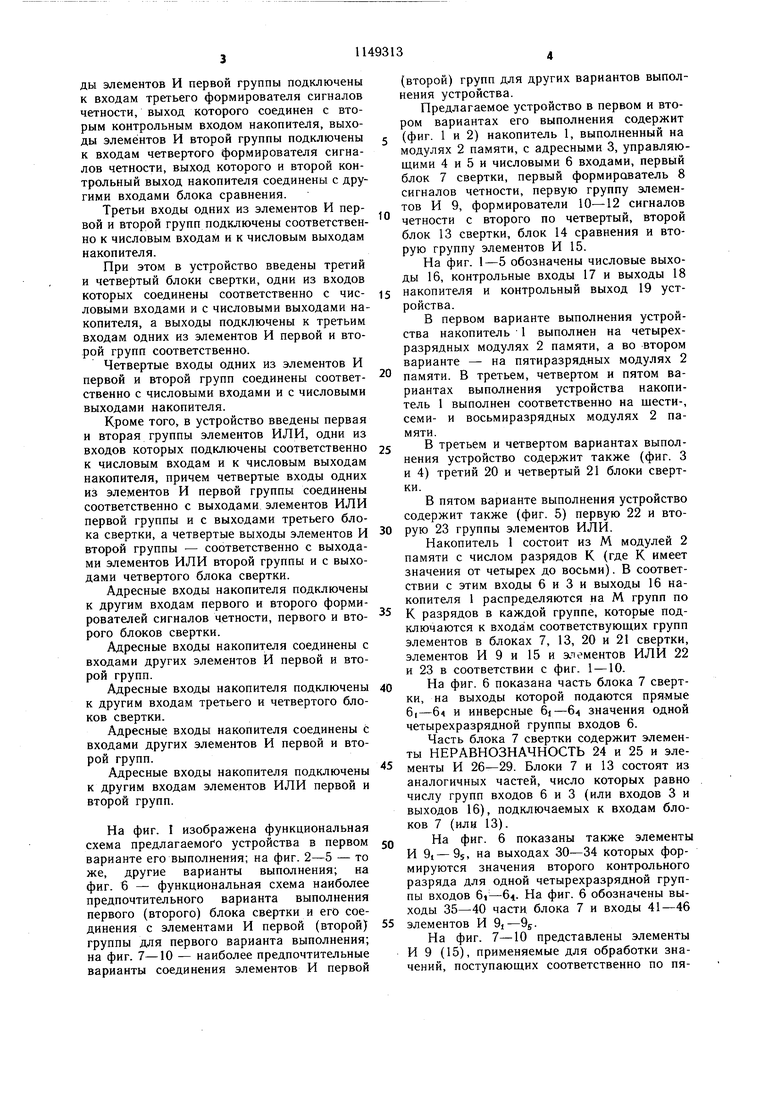

0 На фиг. 6 показана часть блока 7 свертки, на выходы которой подаются прямые 6i-64 и инверсные 6i-64 значения одной четырехразрядной группы входов 6.

Часть блока 7 свертки содержит элементы НЕРАВНОЗНАЧНОСТЬ 24 и 25 и элементы И 26-29. Блоки 7 и 13 состоят из аналогичных частей, число которых равно числу групп входов 6 и 3 (или входов 3 и выходов 16), подключаемых к входам блоков 7 (или 13).

0На фиг. 6 показаны также элементы

И 9t-9s, на выходах 30-34 которых формируются значения второго контрольного разряда для одной четырехразрядной группы входов 6i-64. На фиг. 6 обозначены выходы 35-40 части блока 7 и входы 41-46

5 элементов И .

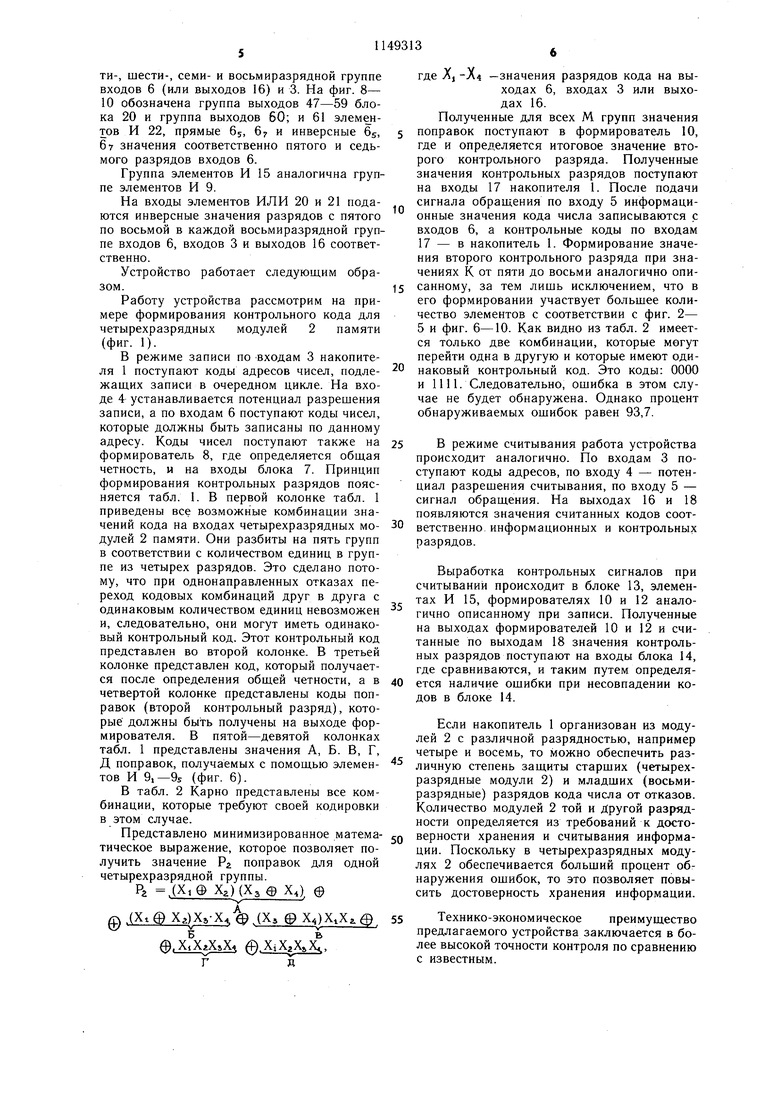

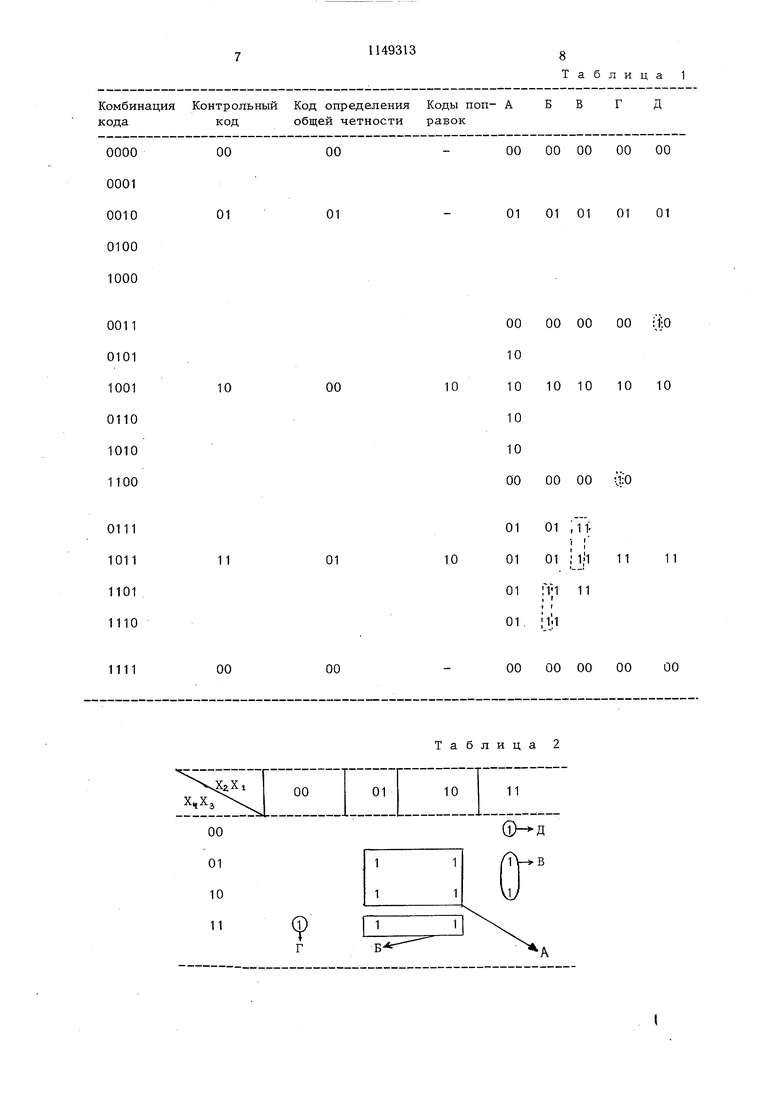

На фиг. 7-10 представлены элементы И 9 (15), применяемые для обработки значений, поступающих соответственно по пяТИ-, шести-, семи- и восьмиразрядной группе входов 6 (или выходов 16) и 3. На фиг. 8- 10 обозначена группа выходов 47-59 блока 20 и группа выходов 60; и 61 элементов И 22, прямые 65, 6 и инверсные 65, 6 7 значения соответственно пятого и седьмого разрядов входов 6. Группа элементов И 15 аналогична группе элементов И 9. На входы элементов ИЛИ 20 и 21 подаются инверсные значения разрядов с пятого по восьмой в каждой восьмиразрядной группе входов 6, входов 3 и выходов 16 соответственно. Устройство работает следующим образом. Работу устройства рассмотрим на примере формирования контрольного кода для четырехразрядных модулей 2 памяти (фиг. 1). в режиме записи по входам 3 накопителя 1 поступают коды адресов чисел, подлежащих записи в очередном цикле. На входе 4 устанавливается потенциал разрешения записи, а по входам 6 поступают коды чисел, которые должны быть записаны по данному адресу. Коды чисел поступают также на формирователь 8, где определяется общая четность, и на входы блока 7. Принцип формирования контрольных разрядов поясняется табл. 1. В первой колонке табл. 1 приведены все возможные комбинации значений кода на входах четырехразрядных модулей 2 памяти. Они разбиты на пять групп в соответствии с количеством единиц в группе из четырех разрядов. Это сделано потому, что при однонаправленных отказах переход кодовых комбинаций друг в друга с одинаковым количеством единиц невозможен и, следовательно, они могут иметь одинаковый контрольный код. Этот контрольный код представлен во второй колонке. В третьей колонке представлен код, который получается после определения общей четности, а в четвертой колонке представлены коды поправок (второй контрольный разряд), которые должны быть получены на выходе формирователя. В пятой-девятой колонках табл. 1 представлены значения А, Б. В, Г, Д поправок, получаемых с помощью элементов И 9,-9s (фиг. 6). В табл. 2 Карно представлены все комбинации, которые требуют своей кодировки в этом случае. Представлено минимизированное математическое выражение, которое позволяет получить значение Р поправок для одной четырехразрядной группы. Рг .(Xi@ Хг)(ХзФ X,), @ 9Xa).(Xi X)XiXj Ш.Х. ffi.XjXA, гд где .X, -Х4 -значения разрядов кода на выходах 6, входах 3 или выходах 16. Полученные для всех М групп значения поправок поступают в формирователь 10, где и определяется итоговое значение второго контрольного разряда. Полученные значения контрольных разрядов поступают на входы 17 накопителя 1. После подачи сигнала обращения по входу 5 информационные значения кода числа записываются с входов 6, а контрольные коды по входам 17 - в накопитель 1. Формирование значения второго контрольного разряда при значениях К от пяти до восьми аналогично описанному, за тем лишь исключением, что в его формировании участвует большее количество элементов с соответствии с фиг. 2- 5 и фиг. 6-10. Как видно из табл. 2 имеется только две комбинации, которые могут перейти одна в другую и которые имеют одинаковый контрольный код. Это коды: 0000 и 1111. Следовательно, ошибка в этом случае не будет обнаружена. Однако процент обнаруживаемых ошибок равен 93,7. В режиме считывания работа устройства происходит аналогично. По входам 3 поступают коды адресов, по входу 4 - потенциал разрешения считывания, по входу 5 - сигнал обращения. На выходах 16 и 18 появляются значения считанных кодов соответственно информационных и контрольных разрядов. Выработка контрольных сигналов при считываний происходит в блоке 13, элементах И 15, формирователях 10 и 12 аналогично описанному при записи. Полученные на выходах формирователей 10 и 12 и считанные по выходам 18 значения контрольных разрядов поступают на входы блока 14, где сравниваются, и таким путем определяется наличие ошибки при несовпадении кодов в блоке 14. Если накопитель 1 организован из модулей 2 с различной разрядностью, например четыре и восемь, то можно обеспечить различную степень защиты старщих (четырехразрядные модули 2) и младших (восьмиразрядные) разрядов кода числа от отказов. Количество модулей 2 той и Другой разрядности определяется из требований к достоверности хранения и считывания информации. Поскольку в четырехразрядных модулях 2 обеспечивается больщий процент обнаружения ошибок, то это позволяет повысить достоверность хранения информации. Технико-экономическое преимущество предлагаемого устройства заключается в более высокой точности контроля по сравнению с известным.

11

10

00 01 10 11

Г S

JiM.

j if

apuz.Z

Фuг.J

Фиг.4

Фиг.б

«о - CV4 1Г К, 5.

ч

:§

i f -, v ч

НЮ

КЮ

Фиг.7

Фиг. 9

Фиг.8

КЮ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «Электронная промышленность, 1979, № 5, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| МЕХАНИЧЕСКАЯ ТРАМБОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ИСКУССТВЕННЫХ ЖЕРНОВОВ | 1923 |

|

SU1033A1 |

| Под ред | |||

| В | |||

| А | |||

| Комарницкого | |||

| М., «Машиностроение, 1982, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-24—Подача