Фг/г. /

2.Устройство по п. 1, отличающееся тем, что адресные входы накопителя соединены с входами других формирователей контрольных сигналов по модулю три первой и второй групп и входами других формирователей сигналов коррекции первой и второй групп.

3.Устройство по пп. 1 и 2, отличающееся тем, что каждый формирователь сигналов коррекции содержит элементы И с первого по шестой, элементы ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первым входам третьего-и пятого элементов И, причем выходы первого и второго элементов ИЛИ соединены соответственно с первым входом шестого элемента И и

с первым входом четвертого элемента И, выход первого элемента И подключен к вторым входам третьего и шестого элементов И, вторые входы четвертого и пятого элементов И соединены с выходом второго элемента И, первые и вторые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента ИЛИ соответственно объединены и являются первым и третьим прямыми входами формирователя, вторым и четвертым прямыми входами которого являются входы первого элемента И, а первым, третьим, вторым и четвертым инверсными входами - соответственно первые и вторые входы первого элемента ИЛИ и второго элемента И,выходами формирователя являются выходы элементов И с четвертого по шестой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU888203A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU894797A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее накопитель, числовые входы которого подключены к входам одних из формирователей контрольных сигналов по модулю три первой группы, а числовые выходы - к входам одних из формирователей контрольных сигналов по модулю три второй группы, и блок сравнения, одни из входов которого соединены с контрольными выходами накопителя, а выход является контрольным выходом устройства, информационными входами и выходами которого являются числовые входы и выходы накопителя, дтличающееся тем, что, с целью повышения точности контроля устройства, в него введены группы формирователей сигналов коррекции и формирователи сигналов четности, причем входы одних из формирователей сигналов коррекции первой группы соединены с числовыми входами накопителя, а выходы подключены соответственно к одним из входов первого и второго формирователей сигналов четности, другие входы которых соединены с выходами формирователей контрольных сигналов по модулю три первой группы, а выходы - с контрольными входами накопителя, входы одних из формирователей сигналов коррекции второй группы подключены к числовым выходам накопителя, а выходы соединены соответственно с одними из входов третьего и четвертого формирователей сигналов четности, другие входы которых подключены к выходам формирователей контрольных сигналов по модулю три второй группы, а выходы - к другим входам блока сравнения. СО со 01

1

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств, выполняемых на интегральных микросхемах.

Известно запоминаюшее устройство с обнаружением ошибок, содержащее модульный накопитель и средства обнаружения ошибок на основе модификации кода Хэмминга 1.

Недостатком этого устройства является низкая точность контроля.

Наиболее близким техническим решением к изобретению является запоминающее устройство с обнаружением ошибок, содержащее накопитель, блок сравнения, одни из входов которого подключены к первому и второму контрольным выходам накопителя, и формирователи контрольных сигналов по модулю три, входы одних из которых соединены с информационными входами накопителя, а входы других - с выходами накопителя 2.

Недостатком известного устройства является низкая точность контроля, так как в нем не обнаруживаются двухразрядные и четырехразрядные ошибки при применении в накопителе четырехразрядных модулей памяти. Не обнаруживаются наиболее вероятные ошибки при применении пяти-восьмиразрядных модулей памяти и не контролируются адресные цепи.

Цель изобретения - повышение точности контроля устройства при применении четырех-восьмиразрядных модулей памяти, а также обнаружение адресных ошибок.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением ошибок, содержащее накопитель, числовые входы которогЪ подключены к входам одних из формирователей контрольных сигналов по модулю три первой группы, а числовые выходы - к входам одних из формирователей контрольных сигналов по модулю три второй группы, и блок сравнения, одни из входов которого соединены с контрольными выходами накопителя, а выход является контрольным выходом устройства, инQ формационными входами и выходами устройства являются числовые входы и выходы накопителя, введены группы формирователей сигналов коррекции и формирователи сигналов четности, причем входы одних из формирователей сигналов коррекции первой

5 группы соединены с числовыми входами накопителя, а выходы подключены соответственно к одним из входов первого и второго формирователей сигналов четности, другие входы которых соединены с выходами

Q формирователей контрольных сигналов по модулю три первой группы, а выходы - с контрольными входами накопителя, входы одних из формирователей сигналов коррекции второй группы подключены к числовым выходам накопителя, а выходы соединены

соответственно с одними из входов третьего и четвертого формирователей сигналов четности, другие входы которых подключены к выходам формирователей контрольных сигналов по модулю три второй группы, а выходы - к другим входам блока сравнения. Кроме того, адресные входы накопителя соединены с входами других формирователей контрольных сигналов по модулю три первой и второй групп и входами других формирователей сигналов коррекции первой и второй групп.

При этом каждый формирователь сигналов коррекции содержит элементы И с первого по шестой, элементы ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первым входам третьего и пятого элементов И, причем выходы первого и второго элементов ИЛИ соединены соответственно с первым входом шестого элемента И и с первым входом четвертого элемента И, выход первого элемента И подключен к вторым входам третьего и шестого элементов И, вторые входы четвертого и пятого элементов И соединены с выходом второго элемента И, первые и вторые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента ИЛИ соответственно объединены и являются первым и третьим прямыми входами формирователя, вторым и четвертым прямыми входами которого являются входы первого элемента И, а первым, третьим, вторым и четвертым инверсными входами - соответственно первые и вторые входы первого элемента ИЛИ и второго элемента И, выходами формирователя являются выходы элементов И с четвертого по шестой.

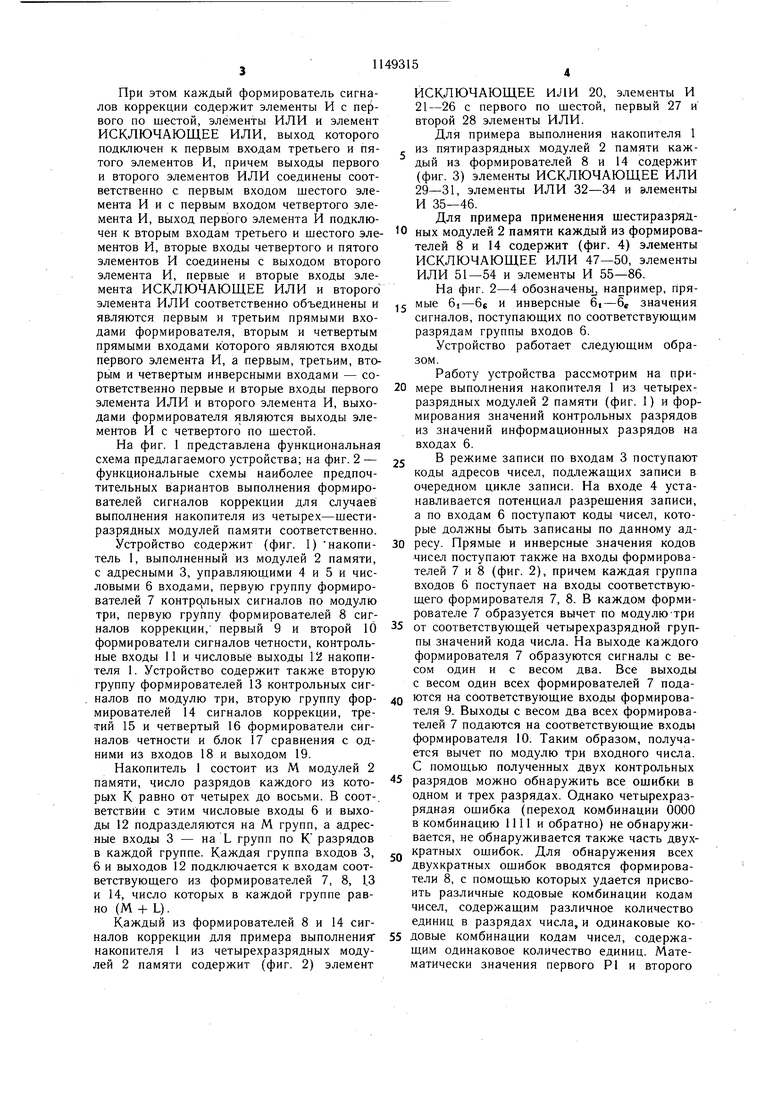

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональные схемы наиболее предпочтительных вариантов выполнения формирователей сигналов коррекции для случаев выполнения накопителя из четырех-шестиразрядных модулей памяти соответственно.

Устройство содержит (фиг. 1) накопитель 1, выполненный из модулей 2 памяти, с адресными 3, управляющими 4 и 5 и числовыми 6 входами, первую группу формирователей 7 контрс)льных сигналов по модулю три, первую группу формирователей 8 сигналов коррекции, первый 9 и второй 10 формирователи сигналов четности, контрольные входы 11 и числовые выходы 2 накопителя 1. Устройство содержит также вторую группу формирователей 13 контрольных сигналов по модулю три, вторую группу формирователей 14 сигналов коррекции, третий 15 и четвертый 16 формирователи сигналов четности и блок 17 сравнения с одними из входов 18 и выходом 19.

Накопитель 1 состоит из М модулей 2 памяти, число разрядов каждого из которых К равно от четырех до восьми. В соот-. ветствйи с этим числовые входы 6 и выходы 12 подразделяются на М групп, а адресные входы 3 - на L групп по К разрядов в каждой группе. Каждая группа входов 3, 6 и выходов 12 подключается к входам соответствующего из формирователей 7, 8, 1,3 и 14, число которых в каждой группе равно (М 4- L).

Каждый из формирователей 8 и 14 сигналов коррекции для примера выполнения накопителя 1 из четырехразрядных модулей 2 памяти содержит (фиг. 2) элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 20, элементы И 21-26 с первого по шестой, первый 27 и второй 28 элементы ИЛИ.

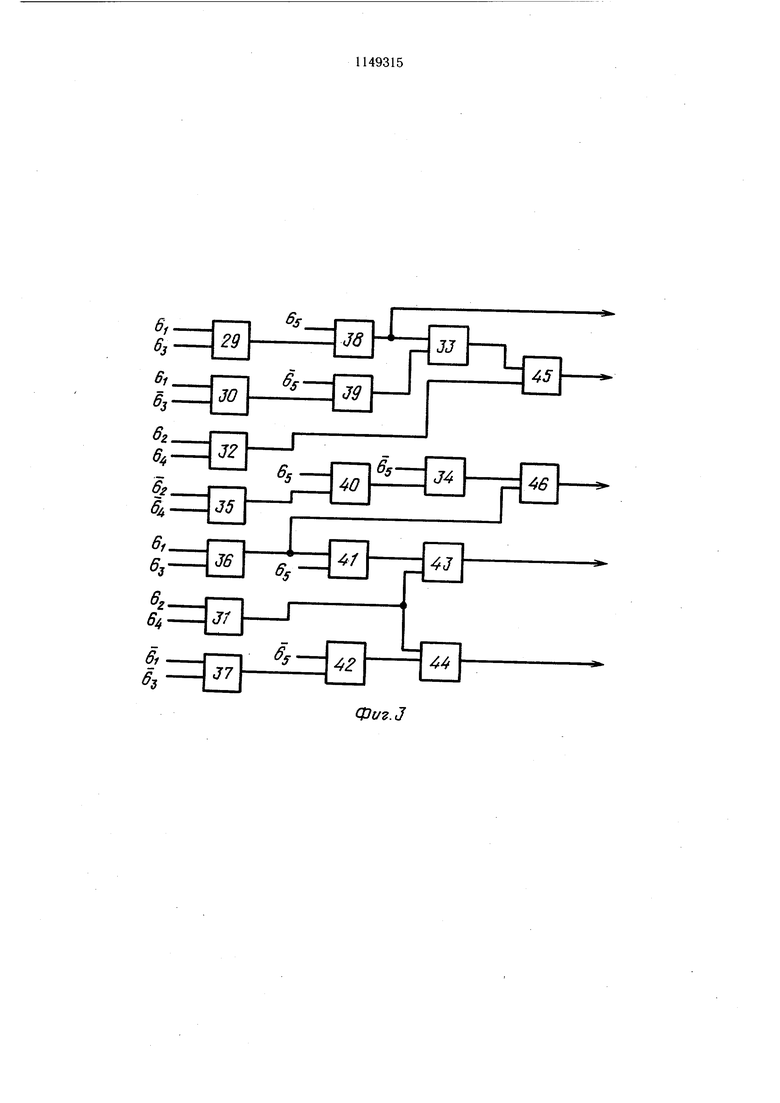

Для примера выполнения накопителя 1 из пятиразрядных модулей 2 памяти каждый из формирователей 8 и 14 содержит (фиг. 3) элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 29-31, элементы ИЛИ 32-34 и элементы И 35-46.

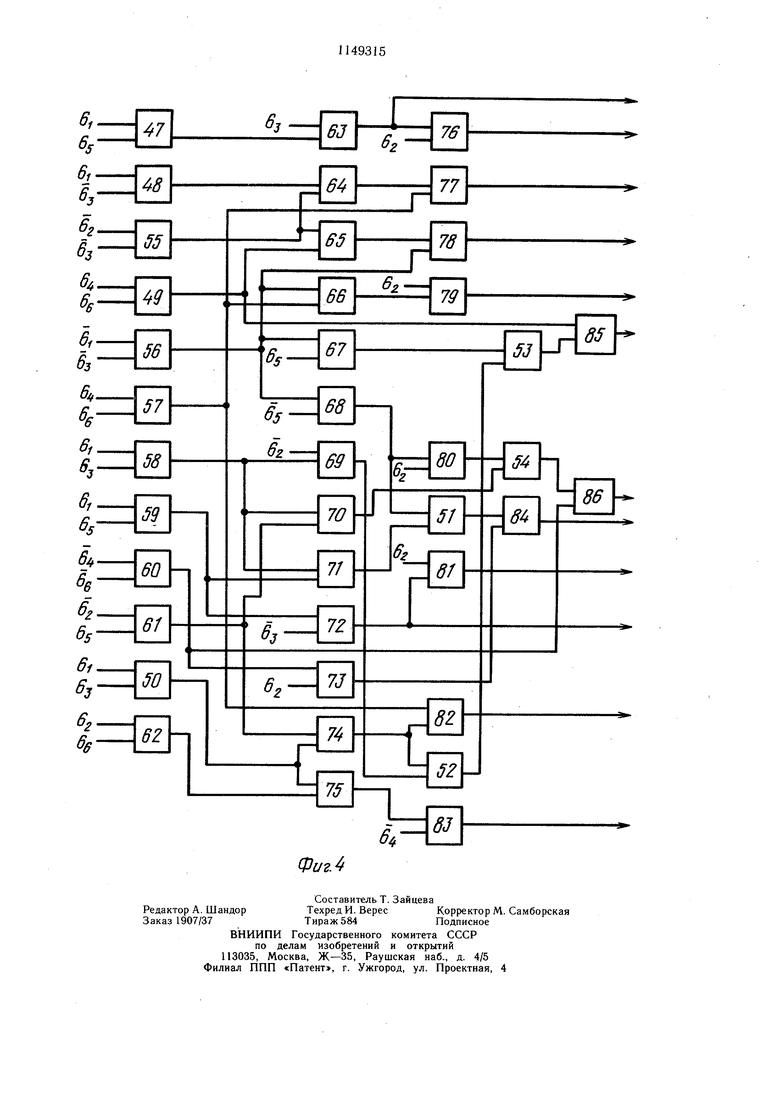

Для примера применения шестиразряд0 ных модулей 2 памяти каждый из формирователей 8 и 14 содержит (фиг. 4) элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 47-50, элементы ИЛИ 51-54 и элементы И 55--86.

На фиг. 2-4 обозначень например, г1ря5 мые 6i-6б и инверсные 6,-6 значения сигналов, поступающих по соответствующим разрядам группы входов 6.

Устройство работает следующим образом.

Работу устройства рассмотрим на примере выполнения накопителя 1 из четырехразрядных модулей 2 памяти (фиг. 1) и формирования значений контрольных разрядов из значений информационных разрядов на входах 6.

5 В режиме записи по входам 3 поступают коды адресов чисел, подлежащих записи в очередном цикле записи. На входе 4 устанавливается потенциал разрешения записи, а по входам 6 поступают коды чисел, которые должны быть записаны по данному адресу. Прямые и инверсные значения кодов чисел поступают также на входы формирователей 7 и 8 (фиг. 2), причем каждая группа входов 6 поступает на входы соответствующего формирователя 7, 8. В каждом формирователе 7 образуется вычет по модулютри

5 от соответствующей четырехразрядной группы значений кода числа. На выходе каждого формирователя 7 образуются сигналы с весом один и с весом два. Все выходы с весом один всех формирователей 7 подаются на соответствующие входы формирователя 9. Выходы с весом два всех формирователей 7 подаются на соответствующие входы формирователя 10. Таким образом, получается вычет по модулю три входного числа. С помощью полученных двух контрольных

5 разрядов можно обнаружить все ошибки в одном и трех разрядах. Однако четырехразрядная ошибка (переход комбинации 0000 в комбинацию 1111 и обратно) не обнаруживается, не обнаруживается также часть двух- кратных ошибок. Для обнаружения всех двухкратных ошибок вводятся формирователи 8, с помощью которых удается присвоить различные кодовые комбинации кодам чисел, содержащим различное количество единиц в разрядах числа, и одинаковые кодовые комбинации кодам чисел, содержащим одинаковое количество единиц. Математически значения первого Р1 и второго Р2 контрольных разрядов, получаемых на выходе .формирователей 9 и 10, можно описать следуюшим образом: Р1 |Дг/ ® xixi(xjvxi)vxix(x/ е х)} мод. 2;.. . Р2 S (ri ф xixi(xVx|)vxixi(x{ @ xi)} мод. 2; где г} , г вычет по модулю три с весом один и весом два соответственно;1 - номер модуля 2, i 1-4-М; Xj,xbxi)i - значения разрядов кода числа i-и группы входов 6. Значения контрольных разрядов Р1 и Р2 поступают на входы 11 накопителя 1. По входу 5 подается сигнал обраш,ения и информационные разряды числа совместно с контрольными записываются в соответствующие разряды накопителя 1. В режиме считывания значения контрольных разрядов РГи Р2 поступают на входы 18 блока 17, а информационные разряды поступают на входы формирователей 13 и 14, а с их выходов - на входы формирователей 15 и 16. В результате на выходе формирователей 15 и 16 образуются значения контрольных разрядов из считанных информационных разрядов. Выработка значений контрольных разрядов при считывании полностью аналогична получению их при заФиг. 2 писи. в результате в блоке 17 происходит сравнение контрольных кодов, что позволяет на выходе 19 получить признак совпадения или несовпадения. Работа устройства с модулями другой разрядности происходит аналогично. Поскольку процент обнаруживаемых ошибок при модулях два с четырьмя разрядами выше, чем при модулях два с большей ра зрядностью, то целесообразно организовать накопитель 1 так, чтобы старшие разряды ко-. да чисел хранились в четырехразрядных модулях два, а младшие - в модулях два большей разрядности, что также повышает достоверность хранения информации. Количество тех и других модулей два определяется из требований по надежности к устройству. Таким образом, для четырехразрядных модулей два памяти обнаруживаются все ошибки кратностью один-три разряда, т.е. всего 93, всех однонаправленных ошибок, и не обнаруживаются четырехкратные ошибки, а для пятиразрядных модулей два памяти обнаруживаются все ошибки кратностью один, три-пять бит. Технико-экономическое преимушество предложенного устройства заключаются в более высокой точности контроля по сравнению с известным устройством.

Фuг.J

S

6j. 6356

/,

r65

.

65 61.

6,62

66

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «Электронная промышленность, 1979, № 5, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сидоров А | |||

| М | |||

| Методы контроля электронных цифровых машин | |||

| М., «Советское радио, 1966, с | |||

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-24—Подача