(54) ЗАПОМИНАЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1164790A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

Изобретение относится к области числительной техники, а именно, к з поминающим устройствам. Известно запоминающее устройство с самоконтролем pj, которое осу ществляет контроль сравнением в каж дом такте считываемой из двух идентичных накопителей информации, образованием сверток для каждого накопителя в случае несравнения хотя бы по одному из разрядов и отключением накопителя, в котором свертка не совпала с информацией в контроль ном разряде. Недостатком этого устройства является недостаточно высокая надежность системы памяти, определяемая выбранным методом общего резервирования.. Из известных устройств наиболее близким к изобретению является запо минающее устройство с самоконтролем ZJ, в котором реализуется мето аналогичный методу раздельного резе вирования по зонам (группам) большой интегральной схемы (БИС). Это устройство содержит накопителЬ} блоки поразрядного сравнения, блою. формирования сигнала отказа, блоки контроля, блок задержки строба считывания, группы дешифраторов, регистры и схемы сравнения адресов, причем адресные входы депшфраторов соединены с адресными шинами, управляю1цие входы дешифраторов первой группы соединены соответственно с выходами блоков контроля и четвертыми входами схем поразрядного сравнения, выходы дешифраторов первой группы соединены соответственно с входами регистров, выходы которых подключены к первым входам схем сравнения адресов, вторые входа которых соединены соответственно с выходами дешифраторов второй группы, выходы схем сравнения адресов соединены с пятыми входами схем поразрядного сравнения и третьиNJH входами блока формирования сигнала отказа.

Недостатком этого устройства является недостаточно высокая надежность, так как раздельным резервированием охвачены группы БИС, составляющие зоны адресов, например 16 ВИС.

Целью изобретения является повьппение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминаю щее устройство с самоконтролем, содержащее накопители, информационные выходы каждого из которых подключены к соответствующим входам схем сравнения и ко входам соответстсвующего блока контроля, управляющий выход каждого из накопителей подключен к первому управляющему входу соответствующего блока контроля, выход которого подключен к соответствующему управляющему входу формирователя сигналов отказа, первый выход формирователя сигналов отказа подключен ко вторым управляющим входам блоков контроля, а второй выход формирователя сигналов отказа подключен ко входу блока задержки, первый выход которого подключен к первым управляющим входам схем сравнения, дополнительно введены регистры, первые входы каждого из которых подключены к соответствующим выходам схем сравнения, первые выходы - к соответствующим управляющим входам схем сравнения, а управляющие входы каждого из регистров подключены к выходу со.отв&тствующего блока контроля, дополнительные накопители, входы каждого из которых подключены ко вторым выходам соответствующего регистра, а выходы ко вторым входам соответствующего регистра, и блок управления, вход которого подключен ко второму уйравляющем выходу блока задержки, а управляющие выходы блока управления подключены к соответствующим управляющим входам дополнительных накопителей.

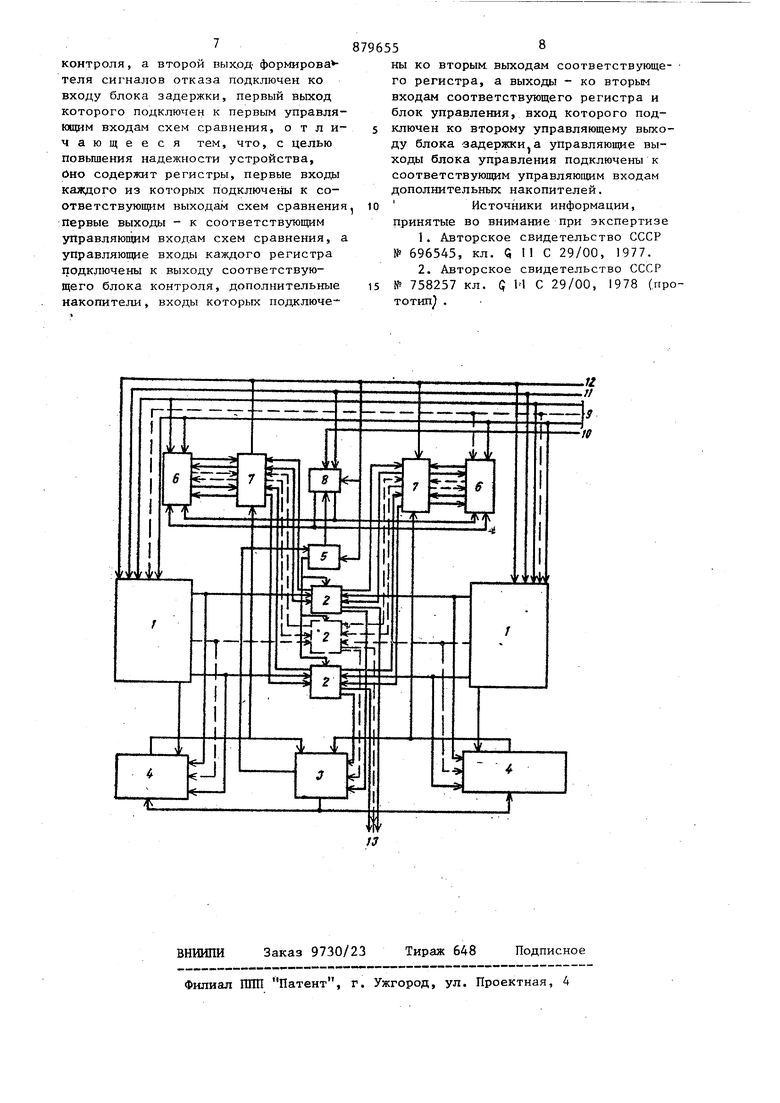

На чертеже изображена блок-схема П8 едложенного устройства.

Устройство содержит накопители 1, схемы сравнения 2, формирователь сигналов отказа 3, блоки контроля 4, блок задержки 5. дополнительные накопители 6,регистры 7, блок управления 8, адресные шины 9, шину начальной установки 10, щину записьсчитывание 11, щину запрос 12, выходные шины устройства 13.

Устройство работает следующим образом.

При подготовке к работе в дополнительные накопители 6 записываются,

например, программным путем все О (все 1), представляющие собой информацию об отсутствии неисправных ячеек в обоих накопителях 1. Для этого от ЭВМ на входы дополнительных накопителей 6 подаются последовательно все сочетания старших разрядов адреса по адресным шинам 9, на входы блока управления 8 - сигналы запроса.по шине 12, начальной установки по шине 10 и команды запись по шине 1 1 , на входы регистров 7 - сигналы запроса. При этом регистры 7 сбрасываются .в исходное состояниеJустройство управления 8 подает сигнгшзаписи на

0 .дополнительные накопители 6 в момент времени, последуюший за установкой регистров 7 в исходное состояние. Содержимое регистров, соответствующее отсутсвию неисправных ячеек накопителей 1, записывается,таким образом, в каждом такте в соответствующие адреса дополнительныхнакопителей до полного их заполнения.

В начале -работы на входы двух накопителей 1

одновременно подаются сигналы кода адреса, числа, записи считывания, запроса. После того, как записана необходимая информация, в такта х считывания при исправной работе обоих накопителей 1 информация на их выходах совпадает, поэтому с выходов схем сравнения 2, проводящих поразрядное сравнение, считанная информация поступает на выход устройства. Одновременно в каждом уакте происходит считывание начально записанной информации из дополнительных накопителей 6 в регистры 7 и ее перезапись обратно по тем же адресам.

Для осуществления этого условия дополнительные накопители 6 должны обладать большим быстродействием, чем накопители 1, а блок управления 8 должен вырабатывать из сигнала запрос ЭВМ второй, сдвинутый во времени, запрос дополнительных накопителей 6. Возможно также использование в качестве дополнительных накопителей БИС ОЗУ, в которых предусмотрен дополнительный режим работы считывание-модификация-запись.

В. случае неисправности одного из накопителей I произойдет несовпадение информации хотя бы в одном из разрядов. Сигнал несовпадения поступит на формирователь сигналов отказа 3, который вырабатывает сигнал запуска блоков контроля 4, например, по модулю два, на входы которых подаются сигналы считывания соответствующих накопителей, а также конт- рольный код, записываемый в дополнительном разряде каждого накопителя. На время выполнения операции свертки происходит задержка строба считывания информации с помощью блока задержки 5, управляемого сигналом от блока формирователя сигналов отказа 4. Блок контроля 4 связанный с неисправным накопителем, вырабатывает сигнал отказа накопителя, который поступает на вход формирователя сигналов отказа 3 и устанавливает его в исходное состояние. Сигнал отказа на копителя поступает также на управляю щий вход соответствующего регистра 7 разрешая за.пись информации, о неисправном разряде, получаемой с выхода схемы поразрядного сравнения 2, в соответствующий разряд регистра. Выходы регистра 7 соединены с соответствующими входами схемы сравнения 2, поэтому после записи в регистр инфор мации о неисправном разряде заблокируется выход неисправного разряда не исправного накопителя 1 и после выработки блоком задержки 5 задержанно го строба произоГтдет считывание истинной информации с выходов схем сра нения. Одновременно инфогмация с выходов обоих регистров 7 будет перезаписана в соответствующие ячейки до полнительных накопителей по вторсму для данного такта сигналу запроса, вырабатываемому блоком управления 8 -после задержки на время выполнения рассмотренных выше операций. Признак записи в дополнительные накопители 6 вырабатывается также блоком управления 8 в каждом такте после сч тывания в,регистры информации, хранимой в дополнительных накопителях. В дальнейшем при обращении к запоминающему устройству по адресам, относящимся к неисправной зоне, контроль по модулю два может не проводиться, так как при каждом последующем обращении происходит считывание информации из дополнительных накопите лей 6 в регистры 7, выхода блокируют соответствующий разряд схе мы сравнения и считываемую из не5. 6 исправного разряда одного из накопителей I информацию. По мере появления последуюпфсх отказов происходит заполнение вспомогательных запоминающих устройств информацией о неисправных разрядах и зонах накопителей. Выходы регистров 7 могут быть выведены на пульт оператора для контроля за состоянием функционирования запоминающего устройства и выявленными неисправностями. Предлагаемое техническое решение обеспечивает раздельное резервирование запоминающего устройства с глубиной резервирования до одной БИС или части БИС. Глубина резервировашя, а следовательно и выигрьпп в надежности определяются соотношением информационной емкости основных накопителей и дополнительных накопителей. При информационной емкости каждого из дополнительных накопителей, равной количеству БИС в основном накопителе, достигается эффективность резервирования, равноценная эффективности пог лементного резервирования на уровне ВИС. Но при этом исключаются присущие поэлементному резервированию недостатки : большое количество элементов объединения БИС и их разделения в случае отказа любой из них, зависимости от некоторых распространенных видов отказов (пробой и утечки входаолс цепей БИС,обрывы или замыкания коммутационных шин, отказы схем управления) . При относительно небольшой емкости накопителя или высокой степени интеграции, входящих в него БИС., глубина резервирования может быть обеспечена на уровне соответствующих частей каждой из БИС. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопители, информационные выходы каждого из которых подключены к соответствующим входам схем сравнения и ко входам соответствующего блока контроля дополнительного информационного разряда вьк ход каждого из накопителей подключен к первому управляющему входу соответствующего блока контроля, выход которого подключен к соответствукщему управляющему входу формирователя сигналов отказа, первый выход формирователя сигналов отказа прдкяочен ко вторым управляющим входам блоков

контроля, а второй вых,од формирова теля сигналов отказа подключен ко входу блока задержки, первый выход которого подключен к первым управляющим входам схем сравнения, о т л ичающееся тем, что, с целью повьпаения надежности устройства, Оно содержит регистры, первые входы каждого из которых подключены к соответствующим выходам схем сравнени первые выходы - к соответствующим управляющим входам схем сравнения, управляющие входы каждого регистра подключены к выходу соответствующего блока контроля, дополнительные накопители, входы которых подключе79655

ны ко вторым, выходам соответствующего регистра, а выходы - ко вторым входам соответствующего регистра и блок управления, вход которого подключен ко второму управляющему выходу блока -задержки J а управляющие выходы блока управления подключены к соответствующим управляюнщм входам дополнительных накопителей. 10 Источники информации,

принятые во внимание при экспертизе

№ 758257 кл. Q 1-1 С 29/00, 1978 (проТОТИП

Авторы

Даты

1981-11-07—Публикация

1980-03-24—Подача