(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935959A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

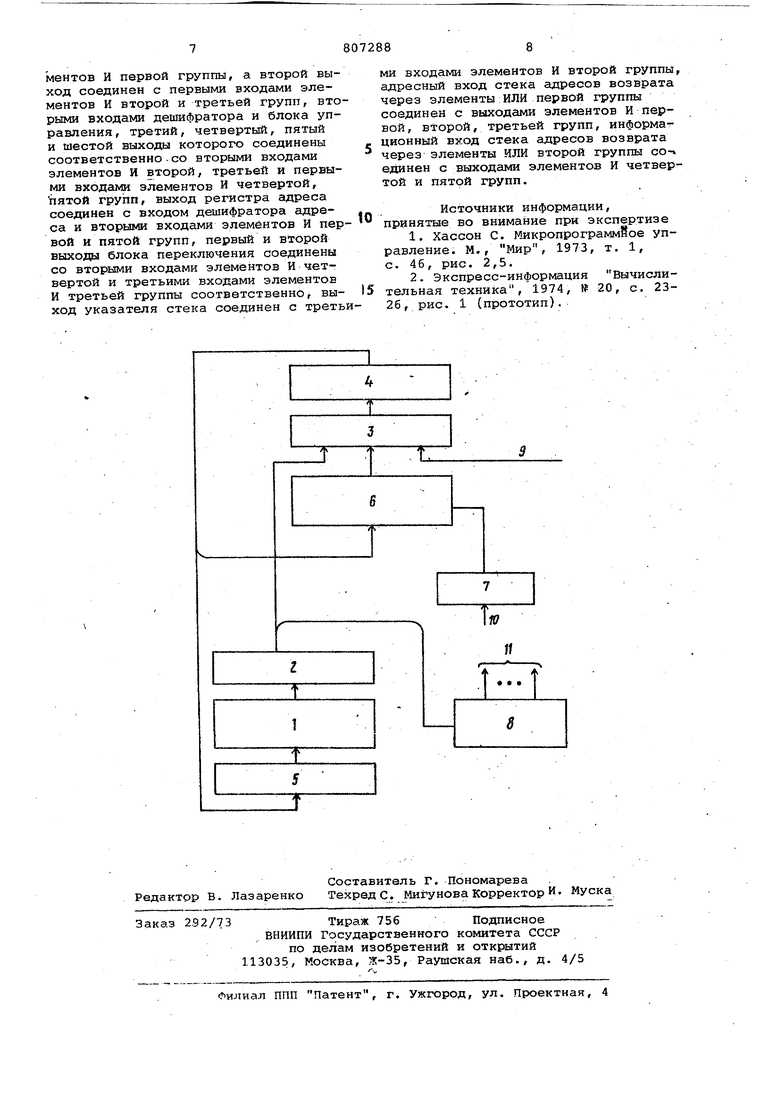

. - 1 Изобретение относится к вычисли1тельной технике и может найти применение в цифровых вычислительных машинах (ЦВМ). Известно микропрограммное устройство управления ЦШ1., содержащее 6JjOK памяти микрокоманд, дешифратор, регистр адреса, регистр микрокоманд, регистр адреса возврата, блок формирования адреса, блок переключения, блок управления Щ. Однако устройство обладает низкими функциональными возможностями, так как число вложенных микропрограм не превьадает одной (равно числу реги стров адреса возврата). Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее блок памяти микрокоманд, блок формирования адреса, регистр адреса, дешифратор, стек адресов возврата, указатель стека, блок местного управления. Устройство имеет в своем составе стек адресов возврата, который вместе с указателем стека позволяет увеличить число вложенных микроподпрограмм до семи j. Недостатками устройства являются 1евозмо кность использования произвольного обращения кэлементам стека без нарушения последовательного механизма адресации, кроме того, содержимое ст,ека заполняется последовательно только значением регистра адреса микрокоманд, что не позволяет изменять содержимое элементов стека в случае необходимости модифицировать последовательность выполнения микроподпрограмм. Указанные недостатки приводят в итоге к непроизводительным затратам объема микропрограммной памяти, так как не позволяют объединить подобные участки микропрограмм, отличающихся одной или несколькими микрокомандами или микроподпрограммами. Цель изобретения - уменьшение объема микропрограммной памяти и увеличение функциональных возможностей микропрограммного устройства управления. Цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор, регистр адреса, регистр 1 мкрокоманд, блок переключения, блок управления, блок Лормирования адреса, стек адресов возврата, указатель стека, причем выход блока памяти микрокоманд соединен со входом регистпа микрокоманд, выход которого соединен с первыми входаг.о1 блоков управления и переключения, -первый выход последнего соединен с первым, входом блока формирования адреса, выход которого соединен с входом регистра адреса, йыход которого соединен с первым вхо дом дешифратора, выход которого соединен с входом блока памяти микрокоманд, второй выход блока переключени соединен с первым входом указателя стека, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен со вторым входом блока переключения, третий вход которого соединен с первым входом устройства, второй вход которого соединен со вторым входом блока формирования адреса, третий вход которого соединен с выходом сте ка адресов .возврата введены группы элементов И, ИЛИ, дешифратор адреса, причем, первый выход дешифратора-адресасоединен с первыми входами элементов И первой группы, а второй выход соединен с первыми входами элементов И второй и третьей групп, вто рыми входами дешифратора и блока управления, третий, четвертый, пятый и шестой выходы которого соединены соответственно со вторыми входами элементов И второй, третьей и первыми входами элементов И четвертой, пятой групп, выход регистра адреса соединен с входом дешифратора адреса и вторыми входами элементов И первой и пятой групп, первый и второй выход 1блока переключения соединены со втор ми входами элементов И четвертой и третьими входами элементов И третьей групп соответственно, выход указателя стека соединен с третьими входами элементов И второй группы, адресный вход стека адресов возврата через элементы ИЛИ первой группы соединен с выходами элементов И первой, второ третьей групп, информационный вход стека адресов возврата через элемент ИЛИ второй группы соединен с выходам элементов И четвертой и пятой групп На чертеже приведена блок-схемаустройства. Устройство содерчсит блок 1 памяти микрокоманд, регистр 2 микрокоманд, содержащий поля 3-5, блок 6 переключения, блок 7 Формирования адреса, регистр 8 адреса, дешифратор 9, стек 10 адресов возврата, блок 11 управ пе ния, указатель 12 стека, дешифратор 13 адреса, группы элементов И 14-18 группы элементов ИЛИ 19 и 20, входы 21 и 22 устройства. Устройство работает следующим образом. В первом такте из блока 1 памяти на регистр 2 считывается очередная микрокоманда по адресу, поступившему из регистра 8 на вход дешифратора 9 Во втором такте в зависимости от начения разрядов полей 3-5 блок 11 правления вырабатывает управляющие игналы, которые поступают в устройтва и схемы цифровой вычислительной ашины. Один из этих сигналов, являощийся признаком естественной адресаии или отсутствия условия перехода, увеличивает содержимое регистра 8 адреса на единицу. В третьем такте продолжается отработка управляющих сигналов, «а также осуществляется подготовка схем к чтению очередной.микрокоманды. Аналогичным образом в последующих трехтактных циклах происходит выборка tt выполнение очередных микрокоманд. Отличие заключается лишь в формировании адреса в микрокомандах передачи управления, ухода или выхода из микроподпрограммы. Отличительная часть работы устройства выполняется в этом случае следукицим образом. При выполнении микрокоманды безусловного или условного перехода (код микрокоманды указывается, например, в поле 3), во втором такте на первом выходе блока б переключения формируется адрес перехода, например, путем передачи поля 5, который посту- пает на вход блока 7, где в случае условной передачи происходит его модификация в зависимости от условий, поступающих по входу 22. В третьем такте адрес перехода, сформированный в блоке 7, записывается на регистр 8. При вьтолнении микрокоманды ухода на микроподпрограмму, во втором такте значение указателя 12 стека и регистра 8 увеличивается на единицу, а на первом выходе блока б формируется адрес перехода на микроподпрограмму. Затем происходит запись содержимого регистра 8 через группу элементов И 14 и ИЛИ 19 в стек 10 адресов возврата по адресу, поступающему из указателя 12 стека через группу элементов И 17 и ИЛИ 20. В третьем такте адрес перехода записывается на регистр 8. . При выполнении микрокоманды выхода из микроподпрограммы, во втором такте осуществляется чтение верхнего элемента стека 10, определяемого содержимым указателя 12 стека, на блока 7. В третьем такте адрес возврата записывается на регистр 8. Затем значение указателя 12 стека уменьшается на единицу., При выполнении микрокоманды изменения последовательности работы со стеком, во втором такте -на втором выходе блока 6 формируется код, например , путем передачи поля 5, который записывается на указатель 12 стека. Кроме указанных режимов работы со стеком 10, устройство имеет возможность произвольного обращения к элементам стека, без нарушения последовательного механизма адресации, как в режиме чтения , так и в режиме записи информацией из полей текущей мик рокоманды или других блоков ЦВМ. Отличительная часть, работы устройстваiT в этих режимах выполняется следующим образом. При выполнении микрокоманды записи в стек, во втором такте на первом выходе блока 6 формируется константа например, путем передачи поля 5, которая через группу элементов И 15 и ИЛИ 19, поступает на информационный вход стека 10. На втором выходе блок б формируется адрес записи,, например путем передачи поля 4, который через группу элементов И 16 и ИЛИ 20 посту пает на адресный вход стека 10. Затем происходит запись В стек. Содержимое регистра 8 в этом такте увеличивается на единицу. . Режим записи информации из внешних блоков по входу 21 осуществляетс аналогичным образом. При этом по вхо ду 21 может поступать как информация так и адрес записи. При выполнении микрокоманда чтения стека по адресу во BTOJPOM такте на втором выходе блока б из поля мик рокоманды 4 .формируется ещрес, который через группу элементов Иг 16 и ,ЛИ 20 поступает на адресный вход сте; аЮ. Затем происходит чтение инфор мации из стека 10, которая поступает на вхрд блока 7. в третьем такте информация записывается на регистр 8. Аналогичным образом происходит чтение стека по адресу, поступающему по входу 21. Режим чтения стека по содержимому регистра 8 адреса осуществляется cлeдsтощим образом. При появлении в старшей части регистра 8 определенного кода (например, всех единиц, что соответствует присвоению элементам стека последних адресов поля микропрограммной памяти дешифратор 13 адреса подключает к аД ресным входам стека 10 через группу элементов ИЛИ 20 и И 18, младшую часть содержимого регистра 8 адреса. Одновременно второй выход дшиф ратора 13 адреса запрещает возможную передачу адреса через группу элементов И 16 и 17, блокирует дешифратор 9 и запускает блок 11 управления на отработку режима чтения из стека 10. В результате в первом такте, вместо чтения очередной мисрокоманды из блока 1 памяти на регистр 2 будут записаны все нули, что является признаком отсутствия микроопераций. Во втором такте выполняется чтение из стека 10 информации, которая на третьем такте запишется в регистр В. Если вновь сформирбванный адрес не относится к области адресов памяти, присвоенной элементам стека,, то в следующем такте происходит выборка :микрокоманды. В противном случае, повторяется режим чтения стека по содержимому регистра 8 аналогично описанному выде. Возможность использования произвольного обращения к элементам стеka без нарушения последовательного механизма €1дресации, как в режиме чтения, так и в режиме записи информации из полей текущей микрокоманды или других блоков ЦВМ позволяет объ;единять подобные участки микропрограмм, отличающиеся одной или несколькими микрокомандами или микрогподпрограммами. Для этого на месте отличающихся микрокоманд прошивается микрокоманда .ухода на микроподпрограмму, адресующая фиксированную ячейку стека, которая используется в дальнейшем для косвенной адресации. Таким образом, увеличение функциональных возможностей за счет реализации произвольно Х обращения к элементам стека без нарушения последовательного механизма адресации, как в режиме чтения, так в режиме записи информации , позволяет сократить объем микропрограммной памяти. Формула изобретения Микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор, регистр адреса, регистр микрокоманд, блок переключения, блок управления, блок формирования адреса, стек адресов возврата, указатель стека, причем, выход блока памяти микрокоманд соединен со входом регистра микрокоманд, выход ко-, торого соединен с первыми входами блоков управления и переключения, первый выход последнего соединен с первым входом блока формирования адреса, выход которого соединен с входом регистра адреса, выход которого соединен с первым входом дешифратора , выход которого соединен с входом блока памяти микрокоманд, второй выход блока перекдночения соединен с первым входом указателя стека, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен со вто1ялм. входом блока переключения, третий вход которого соединен с; первым входом устройства, второй вход которого соединен со вторым входом блока формирования адреса, третий вход которого соединен с выходом стека адресов возврата, отличащщееся тем, что, с целью уменьшения объема борудования оно содержит группы лементов И, ИЛИ, дешифратор адреса, ричем, первый выход дешифратора адеса соединен с первыми вгодами элементов И первой группы, а второй выход соединен с первыми входами элементов И второй и третьей групп, вторыми входами дешифратора и блока управления, третий, четвертый, пятый и шестой выходы которого соединены соответственно.со вторыми входами элементов И второй, третьей и первыми входами элементов И четвертой, пятой групп, выход регистра адреса соединен с входом дешифратора адреса и вторыми входами элементов И первой и пятой групп, первый и второй выходы блока переключения соединены со вторыми входами элементов И четвертой и третьими входами элементов И третьей группы соответственно, выход указателя стека соединен с третьми входами элементов И второй группы адресный вход стека адресов возврата через элементы ИЛИ первой группы соединен с выходами элементов И первой, второй, третьей групп, информационный вход стека адресов возврата через элементы ИЛИ второй группы со- единен с выходами элементов И четвертой и пятой групп.

Источники информации, принятые во внимание при экспертизе

с. 46, рис. 2,5,

Авторы

Даты

1981-02-23—Публикация

1978-07-17—Подача