SJ

Сл

tNd

У

ОР

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в различного типа счетно-решающих устройствгис, системах и приборах автоматического контроля и регулирования, а также в других устройствах, осуществляющих преобразование дискретной информации.

Известен преобразователь параллельного кодаiв последовательный, содержащий регистр хранения (сдвиговый регистр), элементы И, Подключенные к выходу устройства и « регистрам сдвига ij.

Недостатком его является относительно низкое быстродействие и невозможность использования при болшой частоте обмена информационными словами, вызванная.применением распределенных по нескольким шинам импульсов и необходимостью применения подготовительных сигналов.

Наиболее близким к предлагаемому преобразователю является-преобразователь параллельного кода в последовательный, содержащий группу регистров сдвига, информационные входы которых подключены к информациойному входу преобразователя, вход адреса которого через дешифратор соединен с адресными входами ре- гистров сдвига, элементы И, вьаходной элемент И, дешифратор, регистр; управления, входной счетчик, счетчик, управления и коммутатор, причем выходы разрядов всех регистров сдвига .через коммутатор соединен с выходным элементом И, вход синхроимпульсов через входной счетчик и элемент И соединен со счетчиком и регистром управления, выходы которых соответственно соединены с входами коммутатора и через группу элементов И с входами регистров сдвига, а сброс - с соот ветствующими входами счетчика и регистра управления, а также входного счетчика С23«

Недостатками известного устройства являются относительно низкое быстродействие;.., вызванное тем, что преобразование информации ведется обязательно со всей группы регистров сдвига (от первого до последнего), кроме того, оно не позволяет производить преобразование информации , начиная с любого регистра сдвига. Быстродействие снижает также необходимость подачи адресных посылок, количество которых равно числу регистров сдвига. Кроме того, устройство имеет довольно .сложную схему, вызванную применением регистра управления, входнозго счетчика, счетчика управления и коммутатора, что снижает также показатели надежности. Надежность уменьшается также из-за необходимости установки на регистре правления начальных условий в первом разряде.

Целью изобретения является повышение быстродействия преобразования и надежности.

Поставленная цель дост;ягается TQM, что в преобразователь параллелного кода в последовательный, содержащий группу регистров сд.вига, информационные входы которых подключены к информационному входу преобразователя , вход адреса которого через дешифратор соединен с адресными входами регистров сдвига группы, элементы И, введены триггеры адреса, выходной элемент ИЛИ, а регистры сдвига группы со эдинены последовательно,- причемвыходы дешифратора соединены соответственно с единичными входами триггеров адреса, нулевые входы которых подключены к входу о.бнуления преобразователя, а единичные выходы - к первым входам соответствующих элементов И, выходы которых чер€3 выходной элемент ИЛИ соединены с выходом преобразователя, вторые входы элементов И подключены к выхсщам соответствующих регистров сдвкга группы а третьи входы объединены и .подключены к.входу синхронизации преобразователя, соединенного со сдвиговы™ ми входами регистров сдвиха группы.

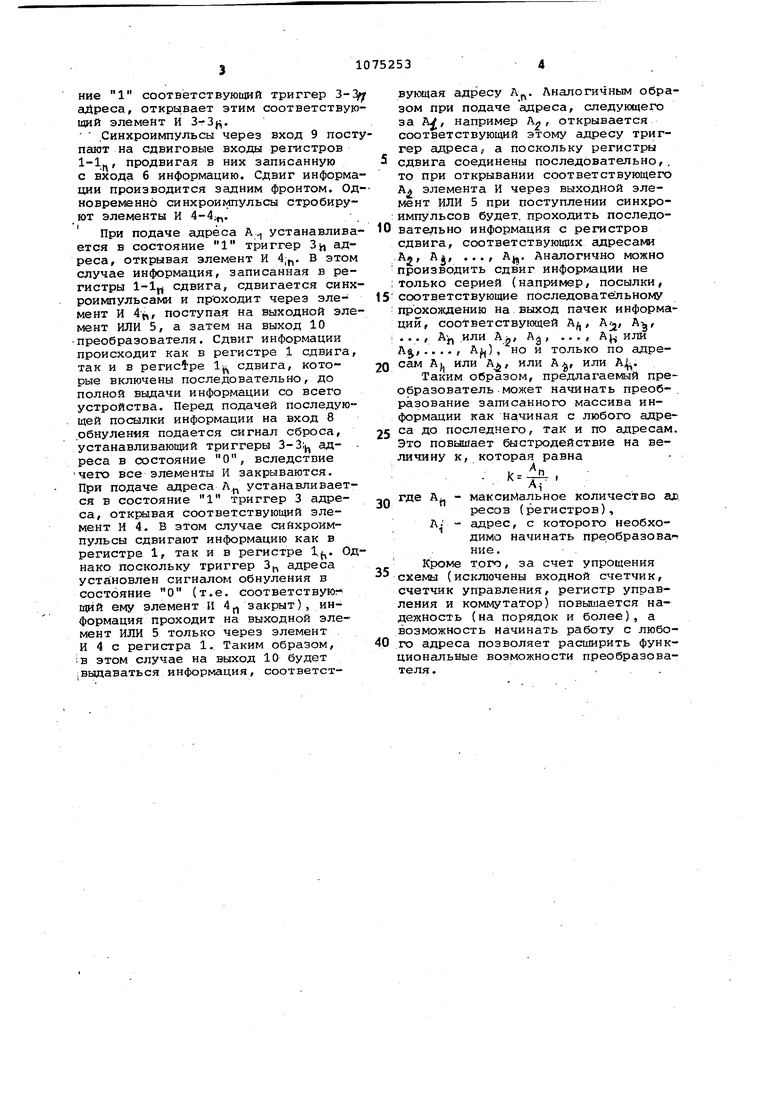

На. чертеже представлена, функциональная схема преобразова еля. Преобразователь содержит, регистры , сдвига, дешифратор 2, триггеры ,адреса (количество которых равно количеству регистров сдвига), элементы И 4-|-4у, выходной элемент Vism 5, информационный. вход 6 преобразователя, вход 7 здреса, вход 8 обнуления, вход 9 синхронизации, выход 10 преобразователя.

Устройство для преобразования параллельного кода в последовательный работает следующим образом.

Через вход 6 подается параллельный код, который необходима преобразовать в последовательный, а через вход 7 на дешифратор 2 подается адрес. Расшифрованный дешифратором 2 адрес производит запись информации в регистры 1-i и одновременно устанавливает соответствующий данному адресу триггер 3-3 адреса в состояние 1. Триггеры 3-Зд адреса перед посылкой адреса устанавливаются в сюстояние О сигналом по входу 8.

Таким образом, массив инфсэрмации подлежавши преобразованию, записывается в регистры сигналами с дешифратора 2. Одновременно дешифратор 2, устанавливая в состояние 1 соответствующий триггер 3адреса, открывает этим соответствугощий элемент И 3-3|.

.Синхроимпульсы через вход 9 пост пают на сдвиговые входы регастров 1-1, продвигая в них записанную с входа б информацию. Сдвиг информации производится задним фронтом. Одновременно синхроимпульсы стробируют элементы И 4-4;.

При подаче адреса А . устанавливается в состояние 1 триггер 3 адреса, открывая элемент И 4;, В этом случае информация, записанная в регистры 1-1у| сдвига, сдвигается синхроимпульсами и проходит через элемент И 4f,, поступая на выходной элемент ИЛИ 5, а затем на выход 10

преобразователя. Сдвиг информации происходит как в регистре 1 сдвига, так и в регистре сдвига, которые включены последовательно, до полной вьщачи информации со всего устройства. Перед подачей последующей посылки информации на вход 8 обнуления подается сигнал сброса, устанавливающий триггеры 3-3; ад- реса в состояние О, вследствие

чего все элементы И закрываются. При подаче адреса Л устанавливается в состояние 1 триггер 3 адреса, открывая соответствующий элемент И 4. В этом случае синхроимпульсы сдвигают информацию как в регистре 1, так и в регистре 1. Однако поскольку триггер 3 адреса установлен сигналом обнуления в состояние О (т.е. соответствуют щий ему элемент И 4 закрыт), информация проходит на выходной элемент ИЛИ 5 только через элемент И 4 с регистра 1. Таким образом,

3 этом случае на выход 10 будет

;выдаваться информация, соответствующая адресу Afj. Аналогичным образом при подаче адреса, следующего за А, например Ал, открывается соответствующий этому адресу триггер адреса, а поскольку регистры 5 сдвига соединены последовательно,, то при открывании соответствующего А элемента И через выходной элемент ИЛИ 5 при поступлении синхро:импульсов будет. проходить последо0 вательно информация с регистров сдвига, соответствующих адресами .Ag, Aj, ..., Aj,. Аналогично можно производить сдвиг информации не ;только серией (например, посылки, 5соответствующие последовательному

прохождению на выход пачек информации, соответствующей А, А, АЪ/

. .. , Aj, или А J, Ад , ... А ц или А,...., А), но и только по адре0 сам Aj или А, или А, или А.

Таким образом, предлагаемый преобразователь может начинать преоб-. разование записанного массива информации как Начиная с любого адре5 са до последнего, так и по адресам. Это повышает быстродействие на величину к, которая равна

- . ,

А

где А(, - максимальное количество ал

(1 ресов (регистров),

i адрес, с которого необходимо начинать прербразование. - .

г Кроме того, за счет упрощения схемы (исключены входной счетчик, счетчик управления, регистр управления и коммутатор) повышается надежность (на порядок и более), а возможность начинать работу с любо0 го адреса позволяет расширить функциональные возможности преобразователя.

I-х)д

Зп

Г

гЗЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU855651A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

ПРЕОБРАЗОВАТЕЛЬ ПАРАЛДЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ, содержащий группу регистров сдвига, ин.формационные входы которых подключены к информационному входу преообраэователя, вход адреса которого Через дешифратор соединен с адрес- ными входами регис1 ров сдвига группы, элементы И, отличающи .file я тем, что, с целью повышения ;быстродействия преобразования, в него введены триггеры адреса/ выход|Ной элеме нт ИЛИ, а регистры сдвига :группы соединены последовательно, ;прич выходы дешифратор соединены I соответственно с единичными входа;ми триггеров адреса, нулевые входы , I которых подключены к входу обнулеI НИН преобразователя, а единичные I выходы - к первым входам соответствующих элементов И, выходы которых через выходной элемент ИЛИ соединены с выходом пр еобразователя, вторые входы элементов И подключены к выходам соответствующих регистров сдвига группы, а третьи входы объе- . S дине1&1 и подключены к входу синхронизации преобразователя, соеди; немного со сдвиговыми входами регистров сдвига группы.

Ъ

z

LF

LZ

I Л I

4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 0 |

|

SU217712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU855651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-20—Подача