Изобретение относится к вычислительной технике, предназначено для использования в контрольно-измерительной технике и является усовершенствованием устройства по основному авт. св. № 857890.

Цель изобретения - повышение достоверности и быстродействия контроля за счет сокращения временного интервала смены каждого тестового набора до минимально необходимого путем кодирования длительности каждого временного интервала смены тестового набора специально вьщеленных для это цели групп разрядов каждого тестового набора.

При этом изменение частоты смены тестовых наборов производится аппаратно с помощью преобразователя кода во времэнной интервал следования импульсов непосредственно в динамике контроля, а также за счет формирования временной диаграммы контроля.соответствующей рабочей, а также путем определения частотновременной области устойчивой работы объекта контроля, так как формирование временного интервала (длительности) воздействия входных сигналов на объект контроля и контролируемых операций, равных рабочим, позволяет производить контроль, исполнения конролируемым объектом каждой операции с учетом влияния переходных процессов, возникающих в объекте контроля при исполнении каждой предьщущей операции на правильность исполнения каждой следующей за ней операции,, а контроль с длительностью воздействия входных сигналов и длительность контролируемых операций, отличающимися от рабочих, позволяет определить устойчивость работы объекта контроля, так как в реальных условиях под воздействием внешних факторов частота функционирования объекта контроля может отличиться от частоты, на которой производится контроль из считмва.емой рабочей t

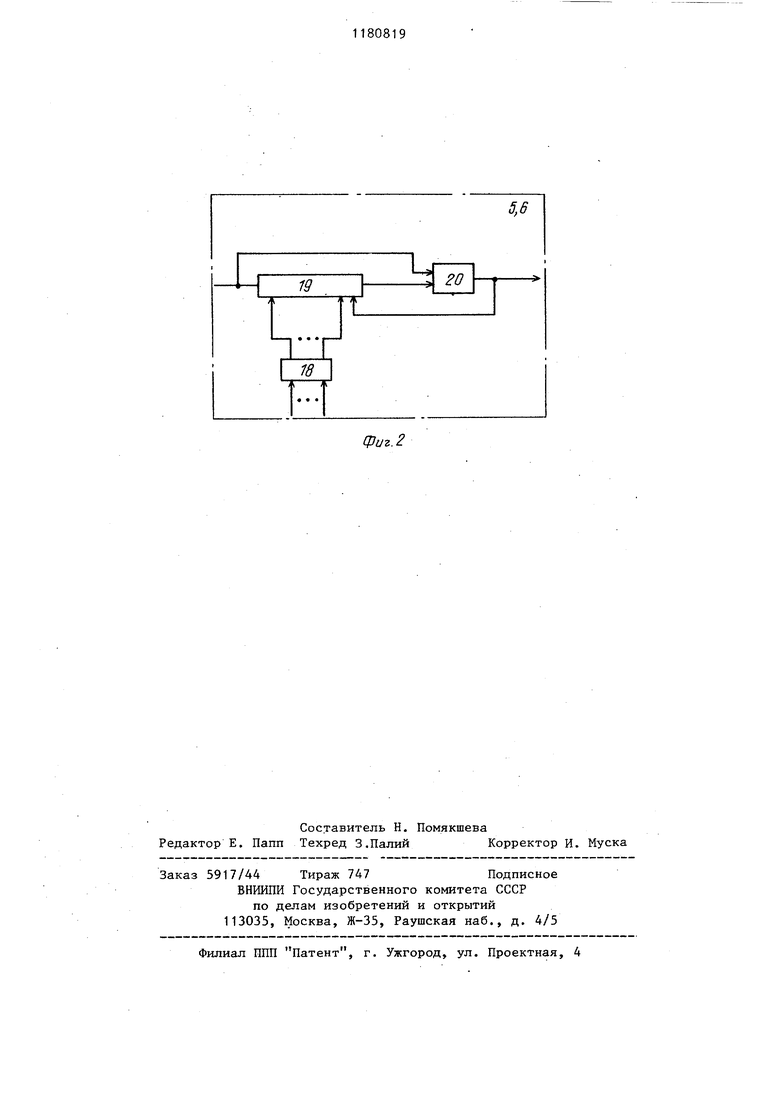

На фиг. 1 предетаалена блок-ехема многоканального уетройетаа для функционального контроля интегральных схем; на фиг. 2 - функциональная схема преобразователя кода во временной интервал следования импульса.

Многоканальное устройство для функционального контроля интегральных схем содержит триггер 1 запуска, единичный вход которого соединен с запускающим входом устройства, а нулевой выход с выходом управляющего элемента ИЛИ 2, управляющий элемент И 3, первый вход которого соединен с единичным выходом триггера 1 запуска, второй вход с выходом тактового генератора 4, а выход - с тактовым входом первого преобразователя 5 кода во временной интервал следования импульсов, выход которого Соединен с тактовьм входом преобразователя 6 кода во временной интервал следования импульсов, регистр 7 управления для управления преобразователя 5 кода во временной интервал, группу элементов ИЛИ 8, распределитель 9 для синхронизации и управления блоками устройства, входной регистр 10 для приема контролируемых сигналов с объекта кoнтpoлЯyN каналов, каждый из которых содержит блок 11 сравнения, для сравнения контролируемых сигналов объектаконтроля с контрольными сигналами, блок 12 памяти для хранения и вьщачи тестовых наборов, выходной регистр 13, первый элемент И 14, триггер 15 для хранения результата сравнения блока 11, второй элемент И 16 и третий элемент И 17, причем каждый преобразователь 5 и 6 содер-. жит дешифратор 18, входы которого соединены с входами преобразователя 5 или бис информационными входами сдвигового регистра 19, и элемент И 20. Сдвиговьй регистр 19 может быт выполнен аналогично.

Функционирование устройства осуществляется следующим образом.

В блок 12 памяти i-го канала записаны наборы управляющих и контрольных сигналов теста (тестовый набор) с номерами i, N+i, 2N+i и т.д., где , а в регистр 7 управления записан код периода следования импульсов на выходе преобразователя 5 кода эо временнай интервал. Предварительно иа блока 12 памяти каждого канала выбраны первые наборы управляющих и контрольных сигналов. Далее во всех каналах, кроме N-ro, осуществляется запись выбранных наборов управляющих и контрольных сигналов в соответствующие выходные регистры 13 и регистры блоков 11 сравнения. После этого во всех блоках 12 памяти, кроме

(N-1)-ro и N-го каналов, выбираются вторые наборы управляющих и контрольных сигналов. Затем из выходного регистра 13 первого канала через элементы ИЛИ 8 на объект контроля и преобразователь 6 кода во временной интервал подается первый набор управляющих сигналов.

По сигналу с запускающего входа устройства триггер 1 запуска уставав ливается в единичное состояние, вследствие чего снимается блокировка с управляющего элемента И 3. Импульсы с выхода генератора 4 поступают на вход первого преобразователя 5 кода во временной интервал и сдвиговый регистр 19 начинает сдвиг единичного уровня в направлении от младших разрядов сдвигового регистра к старшему, срабатывая по заднему фронту тактовых импульсов генератора 4. При достижении старшего разряда единичным уровнем.и с приходом следующего тактового импульсоа генератора 4 в результате срабатывания элемента И 2 импульс с выхода последнего,соединенного с выходом преобразователя 5 кода во временной интервал, поступает на вход следующего преобразователя 6 кода во временной интервал и вход режима работы сдвигового регистра 19. При этом по заднему фронту тактового импульса происходит запись информации, поступающей на входы сдвигового регистра 19с выходов дешифратора 18, в результате чего устанавливается в единичное состояние, соответствующее коду на входе дешифратора 18, один из разрядов распределителя 9. Таким образом преобразователь кода во временной интервал подготавливается к следующему такту работы.

Преобразователь 6 кода во временной интервал с поступлением на его вход тактовых импульсов с выхода преобразователя 5 кода во временной интервал работает аналогичным образом и на выходе преобразователей 5 и 6 кода во временной интервал образуются последовательности импульсов с временным интервалом, соответствующим коду в регистре 7 управления и на входах первой группы элементов ИЛИ 8, при этом период следования импульсов на выходе преобразователя 5 кода во временной интервал устанавливается равным весовому значению кода временного интервала смены тестовых наборов, под который в тестовом наборе отведена группа разрядов, а на выходе преобразователя 6 кода во временной интервал - равным времени смены тестовых наборов и изменяется в динамике контроля с изменением кода на выходах первой группы элементов ИЛИ 8, постпающего на соответствующие входы преобразователя 6 кода во временной интервал. Импульсы с выхода преобразователя 6 кода во временной интервал поступают на тактовый вход распределителя 9 и управляющий вход входного регистра 10. При этом входной регистр 10 функционирует по переднему фронту единичного логического уровня, вьфабатываемого преобразователем 6 кода во временной интервал, распределитель 9 - по заднему фронту указанного единичного логического уровня. Вследствие этого в первом такте работы осуществляется запись во входной регистр 10 первого набора выходных сигналов объекта контроля, который сравнивается в блоке 11 сравнения первого канала с первым набором контрольных сигналов, поданных с выходов соответствующего блока 12 памяти и хранимых в регистре указанного блока 11 сравнения. По первому сигналу распределителя 9 результат сравнения через элемент И 14 первого канала запоминается на соответствующем триггере 15, предварително установленном в нулевое состояние Одновременно с этим осуществляется запись в выходной регистр 13 N-ro канала тестового набора управляющих сигналов и выборка очередного тестового набора управляющих и контрольных сигналов в блоке 12 памяти (N-1)-го канала, а также подача из выходного регистра 13 второго канала через группу элементов ИЛИ 8 на входы преобразователя 6 кода во временной интервал и объект контроля второго тестового набора управляющих сигналов.

Во втором такте работы после окончания заданного временного интервала осуществляется запись во входной регистр 10 второго набора выходных сигналов с объекта контроля, который сравнивается в блоке 11 сравнения второго канала с вторым тестовым набором контрольных сигналов, поданных с выходов соответствующего блока 12 памяти и хранимых в регистре указанного блока 11 сравнения. По второму сигналу распределителя 9 результат сравнения через элемент И 1А второго канала запоминается на соответствующем триггере 15 этого канала, предварительно установленном в нулевое состояние. Одновременно с этим осуществляется анализ содержимого триггера 15 первого канала с помощью разблокировки элементов И 16 и 17 этого же какала. При совпадении первых наборов входных сигналов объекта контроля и контрольных сигналов на блоке 11 сравнения первого канала, т.е. при правильном функционировании объекта контроля триггер 15 первого канала находится в единичном состоянии, в ре зультате чего при помощи единичного логического уровня с выхода соответствующего выходного элемента И 16 осуществляется запись очередного тестового набора управляющих и контрольных сигналов в выходной регистр 13 и регистр блока 11 сравнения этого канала. Одновременно по второму сигналу распределителя 9 осуществляется выборка очередного тестового набора управляющих и контрольных сигналов в блоке памяти N-ro канала, а также подача из выходного регистра 13 третьего канала через группу элементов ИЛИ 8 на входы преобразователя 6 кода во временной интервал и объекта контроля третьего набора управляющих сигналов. .

При неправильном функционировании объекта контроля триггер 15 первого канала находится в нулевом состоянии в результате чего при помощи единичного логического уровня с выхода соответствующего элемента И 17 через управляющий элемент ИЛИ 2 триггер 1 запуска переводится в нулевое состояние. Вследствие этого триггер 4 отключается от преобразователя 5 кода во временной интервал.

Работа устройства ведется в режиме Тоден - Брак.

Дальнейшая работа устройства осуществляется аналогично при подаче на запускающий вход триггера 1 запуска сигнала с запускающего входа устройства, при этом каждый i-й сигнал распределителя 9 устанавливает триггер 15 (i-2)-ro канала в исходное нулевое состояние.

При определении частотно-времейной области устойчивой работы объекта контроля в регистр 7 управления записывается с помощью средств устройства новое значение кода для получения на выходе преобразователя 5 кода во временной интервал требуемого временного интервала следования импульсов, значение которого является весовым для преобразователя 6 кода во временной интервал, на информационные входы которого поступает код временного интервала смены тестовых наборов с группы соответствующих выходов группы элементов ИЛИ 8, т.е. изменяя ход в регистре 7 управления, можно оперативно изменять временной интервал смены тестовых наборов и временной интервал, по окончании которого производится контроль выходных сигналов объекта контроля, не изменяя соответствующего кода в тестовых наборах, для изменения которых требуется перегрузка блоков 12 памяти, что приводит к возрастанию времени контроля.

5,6

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля сложных релейных распределителей | 1987 |

|

SU1522209A2 |

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для тестового контроля электромеханических блоков | 1982 |

|

SU1151973A1 |

1. МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ по авт. св. № 857890, отличающееся тем, что, с целью повышения достоверности и быстродействия, в него введены первый и второй преобразователи кода во временной интервал, регистр управления, группа входов которого соединена с соответствующими входами устройства, а группа выходов - с группой соответствующих входов первого преобразователя кода во временной интервал, тактовый вход которого соединен с выходом управляющего элемента И, а выход - с тактовым входом второго преобразователя кода во временной интервал, группа входов которого соединена с соответствующей группой выходов группы элементов ИЛИ, а выход - с тактовым входом распределителя . 2. Устройство ПОП.1, отличающееся тем, что преобразователь кода во временной интервал содержит элемент И, сдвиговый регистр и дешифратор, группа входов которого соединена с соответствующими i входами преобразователя кода во временной интервал, группа выходов - с (Л группой соответствующих входов сдвигового регистра, тактовый вход которого соединен с тактовым входом преобразователя и первым входом элемента И, а выход - с вторым входом элемента И, выход которого соединен с входом режима работы сдвигового 00 о регистра и входом преобразователя. 00 со

| Многоканальное устройство для функционального контроля интегральных схем | 1979 |

|

SU857890A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-09-23—Публикация

1982-12-23—Подача