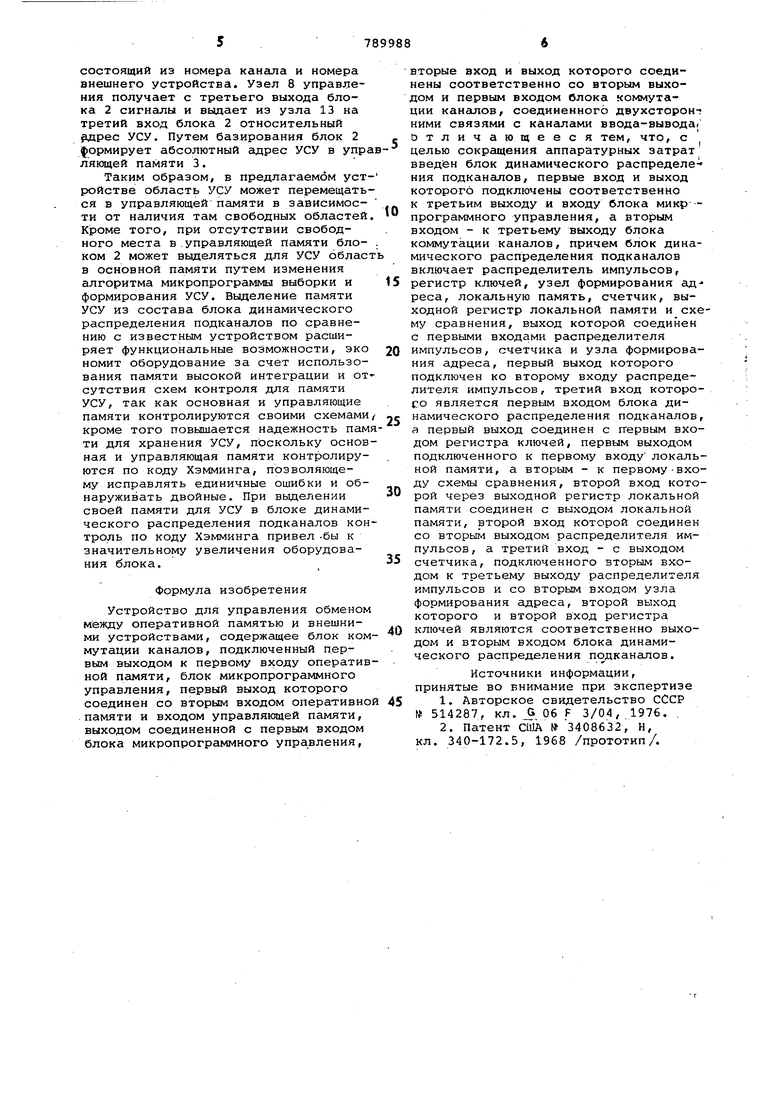

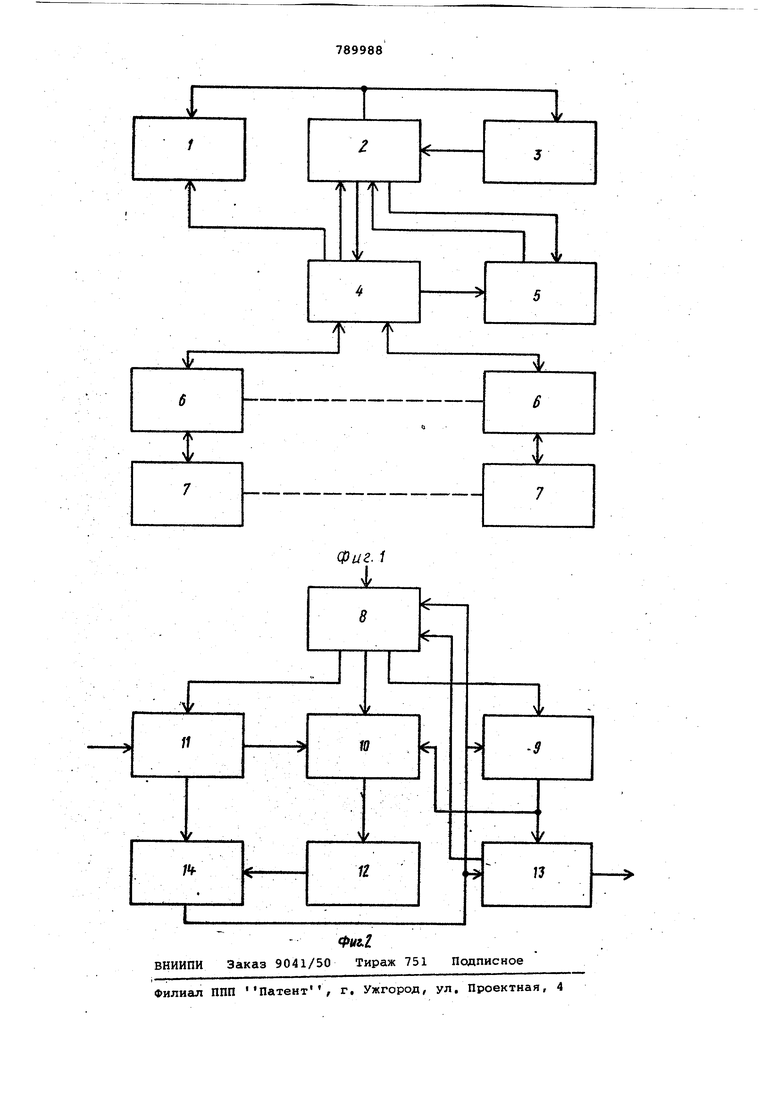

Поставленная цель достигается тем что в устройство, содержащее блок коммутации каналов, подключенный пер вым выходом к первому входу оператив .ной памяти, блок микропрограммного управления, первый выход которого со динен со вторым входом оперативной, памяти и входом управляющей памяти, {выходом соединенной с первым входом влока микропрограммного управления, вторые вход и выход которого соеди нены соответственно со вторым выходом и первым входом блока коммутации каналов, соединенного двухсторонними связями с каналами ввода-вывода, введен блок динамическогораспределе ния подканалов, первые вход и выход которого подключены соответственно к третьим выходу и. входу блока микро программного управления, а вторым входом - к третьему выходу блока ком мутации каналов, причем блок динамического распределения подканалов .включает распределитель импульсов, регистр ключей, узел формирования адреса, локальную память, счетчик, выходной регистр локальной памяти и схему сравнения, выход которой соединен с первыми входами распределителя импульсов, счетчика и узла формирования адреса, первый выход которого подключен ко второму входу распределителя импульсов, третий вход которого является первым входом блока динамического распределения подканалов, первый выход соединен с пер вым входом регистра ключей, первым выходом подключенного к первому входу локальной памяти, а вторым - к первому входу схемы сравнения, второ вход которой через выходной регистр локальной памяти соединен с выходом локальной памяти, второй вход которо соединен со вторым выходом распределителя импульсов, а третий вход - с выходом счетчика, подключенного -вторым входом к третьему выходу распред лителя импульсов- и со вторым входом узла формирования адреса, второй выход которого и второй вход регистр ключей являются соответственно выходом и вторым входом блока динамического распределения подканалов. На фиг. 1 приведена блок-схема ус ройства; на фиг. 2 - схема блока динамического распределения подканалов Устройство содержит оперативную (основную) память 1, блок 2 микропро граммного управления, управляющую память 3 микропрограмм, блок 4 комму тации каналов, бло 5 динамического распределения подканалов,канашы 6 -и внешние устройства 7 ввода-вывода. Блок 5 динамического распределения п каналов содержит узел 8 распределени импульсов (распределитель импульсов) счетчик 9, локальную память 10, регистр 11 ключей, выходной регистр 12 локальной памяти, узел формировв ния адреса и схему 14 сравнения. Устройство работает следующим образом. Управление обращением к основной памяти 1 и управляющей памяти 3 производится сигналами, выдаваемыми с первого выхода блока 2. Микрокоманды, определяющие алгоритм работы блока 2 микропрограммного управления, (поступают в блок 2 из управляющей памяти 3. Блок 4 коммутирует один из каналов, требующих обслуживания для передачи данных на первый вход основной памяти 1. При передаче данных оборудование блока 4 и основной памяти 1 разделяется на один цикл основной памяти. Работа мультиплексного и блок-мультиплексных каналов происходит под управлением управляющего слова внешнего устройства (УСУ), в котором записаны режим работы и операция, запущенная на устройстве, указаны область обмена с основной памятью и объем массива данных. Для выборки УСУ блок 4 коммутирует сигнал gianpoca от наиболее приоритетного из требующих обслуживания каналов б на второй вход блока 2, который выдает в регистр 11 управляющую команду, содержащую номер канала и адрес устройства, являющихся ключом поиска для блока 5. В процессе формирования относительного адреса УСУ узел 8 опрашивает ячейки локальной памяти 10, содержимое которых поступает на выходной регистр 12. На входы схемы 14 сравнения со второго выхода регистра 11 и выхода выходного регистра 12 поступают для сравнения ключи, при этом формируется сигнал сравнения, который с выхода схемы 14 сравнения поступает на узлы 8 и 13. При появлении этого сигнала содержимое счетчика 9 поступает на второй вход узла 13, а затем с его выхода на второй вход узла 8. Содержимое счетчика 9 при сравнении ключей будет относительным адресом УСУ в области УСУ. При несравнении ключей соответствующий сигнал « поступает с выхода схемы 14 сравнения на первый вход счетчика 9 и первый вход узла 8. Счетчик модифицируется, а сигнал со второго выхода узла 8, поступающий на второй вход локальной памяти 10, вызывает выборку следующей строки таблицы ключей по адресу, поступающему на третий вход локальной памяти 10 с выхода счетчика 9. В режиме записи ключа узел 8 управления организовывает сканирование таблицы ключей в локальной .памяти 10, пока не будет свободная строка. Текущее значение счетчика будет относительным адресом УСУ, которое записывается в основную или управляющую память, а в таблицу кл1очей записывается ключ. состоящий из номера канала и номера внешнего устройства. Узел В управления получает с третьего выхода блока 2 сигналы и выдает из узла 13 на третий вход блока 2 относительный адрес УСУ. Путем базирования блок 2 формирует абсолютный адрес УСУ в упр ляющей памяти 3. Таким образом, в предлагаемом уст ройстве область УСУ может перемещать ся в управляющей памяти в зависимости от наличия там свободных областей Кроме того, при отсутствии свободного места в.управляющей памяти блоком 2 может выделяться для УСУ облас в основной памяти путем изменения алгоритма микропрограммы выборки и формирования УСУ. Выделение памяти УСУ из состава блока динамического распределения подканалов по сравнению с известным устройством расширяет функциональные возможности, эко номит оборудование за счет использования памяти высокой интеграции и от сутствия схем контроля для памяти УСУ, так как основная и управляющие памяти контролируются своими схемами кроме того повышается надежность пам ти для хранения УСУ, поскольку основ ная и управляющая памяти контролируются по коду Хэмминга, позволяющему исправлять единичные ошибки и обнаруживать двойные. При вьщелении своей памяти для УСУ в блоке динамического распределения подканалов ко троль по коду Хэмминга привел -бы к значительному увеличения оборудования блока. Формула изобретения Устройство для управления обменом между оперативной памятью и внешними устройствами, содержащее блок ком мутации каналов, подключенный первым выходом к первому входу операти ной памяти, блок микропрограммного управления, первый выход которого соединен со вторым входом оперативн .памяти и входом управляющей памяти, выходом соединенной с первым входом блока микропрограммного управления, вторые вход и выход которого соединены соответственно со вторым выходом и первым входом блока коммутации каналов, соединенного двухсторон- ними связями с каналами ввода-вывода/ отличающееся тем, что, с целью сокращения аппаратурных затрат введен блок динамического распределения подканалов, первые вход и выход которого подключены соответственно к третьим выходу и входу блока микр- программного управления, а вторым входом - к третьему выходу блока коммутации каналов, причем блок динамического распределения подканалов включает распределитель импульсов, регистр ключей, узел формирования ад- реса, локальную память, счетчик, выходной регистр локальной памяти и схему сравнения, выход которой соединен с первыми входами распределителя импульсов, счетчика и узла формирования адреса, первый выход которого подключен ко второму входу распределителя импульсов, третий вход которосо является первым входом блока динамического распределения подканалов, а первый выход соединен с первым входом регистра ключей, первым выходом подключенного к первому входу локальной памяти, а вторым - к первому-входу схемы сравнения, второй вход которой через выходной регистр локальной памяти соединен с выходом локальной памяти, второй вход которой соединен со BTOpbiiM выходом распределителя импульсов, а третий вход - с выходом счетчика, подключенного вторым входом к третьему выходу распределителя импульсов и со вторым входом узла формирования адреса, второй выход которого и второй вход регистра ключей являются соответственно выходом и вторым входом блока динамического распределения подканалов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 514287, кл. .06 F 3/04,Д976. . 2.Патент США 3408632, Н, кл. 340-172.5, 1968 /прототип/.

I f

/ f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

Авторы

Даты

1980-12-23—Публикация

1978-12-21—Подача