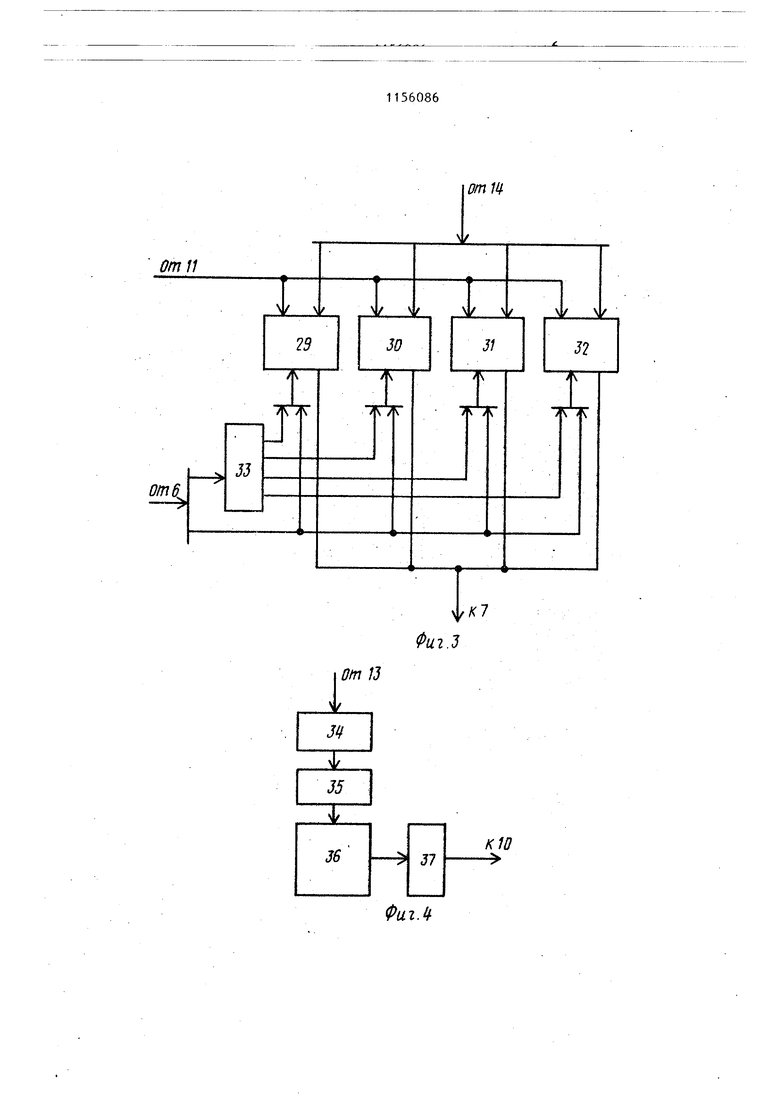

от 11

от т

К7

Фиг.

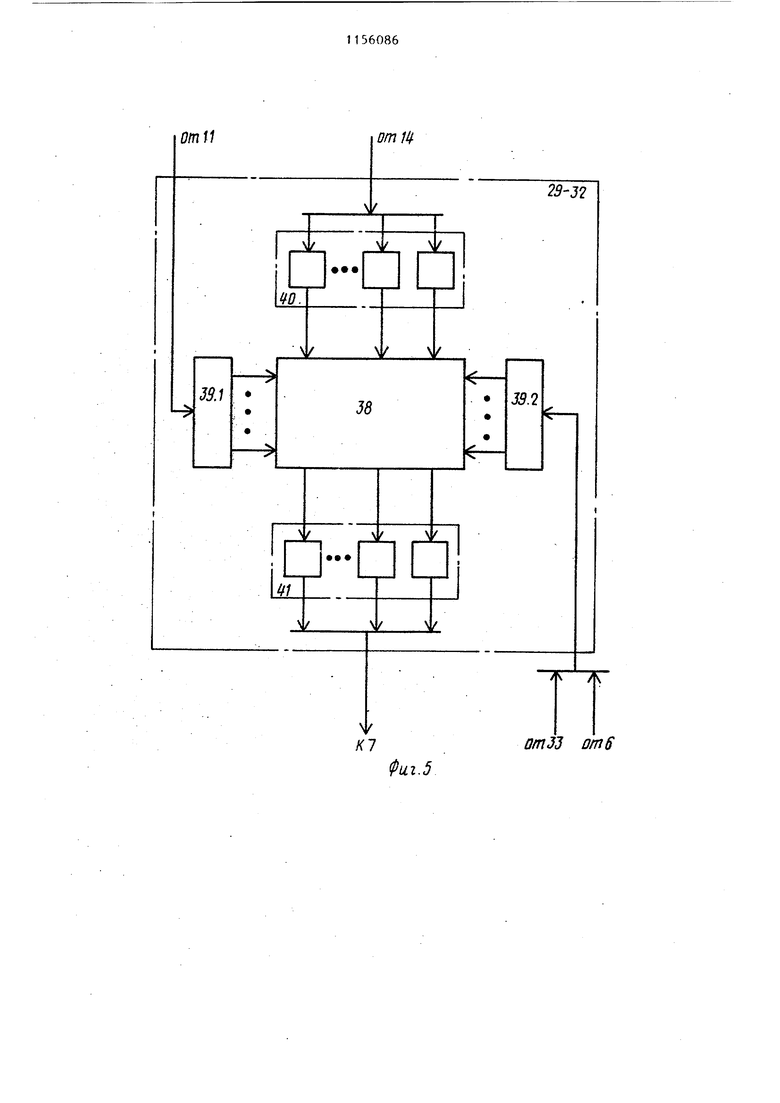

от 13

KW

Фаг.If

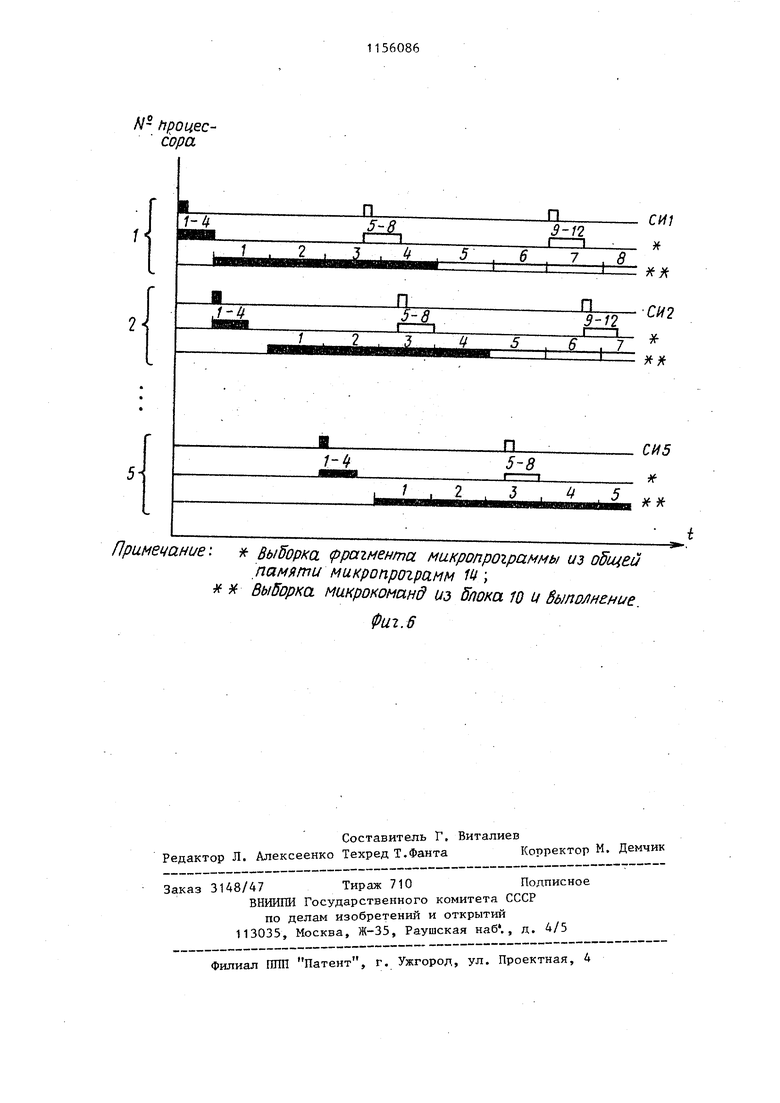

от 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Процессор с реконфигурацией | 1979 |

|

SU798853A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДАННЫХ, содержащее блок переключате лей, N блоков оперативной памяти и М процессоров, каждый из которых вк чает операционный блок, генератор синхроимпульсов, регистр адреса мик рокоманды, регистр микрокоманды, дешифратор микрокоманды, блок памяти микропрограмм и регистр адреса, синхровход, информационный вход и выход которого соединены соответственно с выходом дешифратора микроко манды и первым информационным выход операционного блока того же процессора и адресными входами блоков опе ративной памяти, входы разрешения о ращения которых подключены к соответствующим выходам блока переключа телей, выход команды, второй информ ционный выход, информационный вход вход кода операции операционного блока каждого процессора соединены соответственно с первым информацион ным входом регистра адреса микрокоманды того же процессора, информаци онными входами и информационными вы ходами блоков оперативной памяти и выходом дешифратора микрокоманды того же процессора, выход регистра адреса микрокоманды каждого процессора подключен , к первому адресному входу блока памяти микропрограмм того же процессора, вход, первый и второй выходы регистра микрокоманды каждого процессора соединены соответственно с выходом блока памяти микропрограмм, входом дешифратора микрокоманды и вторым информационным входом регистра адреса микрокоманды того же процессора, а вход генератора синхроимпульсов каждого процессора подключен к синхровходу устройства, отличающееся тем, что, с целью уменьшения объема оборудования, оно содержит блок общей памяти микропрограмм, а в каждый процессор дополнительно введены счетчик адреса, схема сравнения и регистр адреса об-, щей памяти микропрограмм, синхровход, .информационный вход и выход которого соединены соответственно с выходом генератора синхроимпульсов и выходом команды операционного блока того же процессора и адресным входом блока общей памяти микропрограмм, выход которого подключен к входам разрешения обращения блоков памяти микропрограмм всех процессо-г ров, вход и выход счетчика адреса каждого процессора соединены соответственно с выходом генератора синхроимпульсов и вторым адресным входом блока памяти микропрограмм того же процессора, а первый и второй входы и выход схемы сравнения калщого процессора подключены соответственно к выходу регистра адреса

U

r

J9.2

У М

/N

urn 33 от 6

Фиг.5

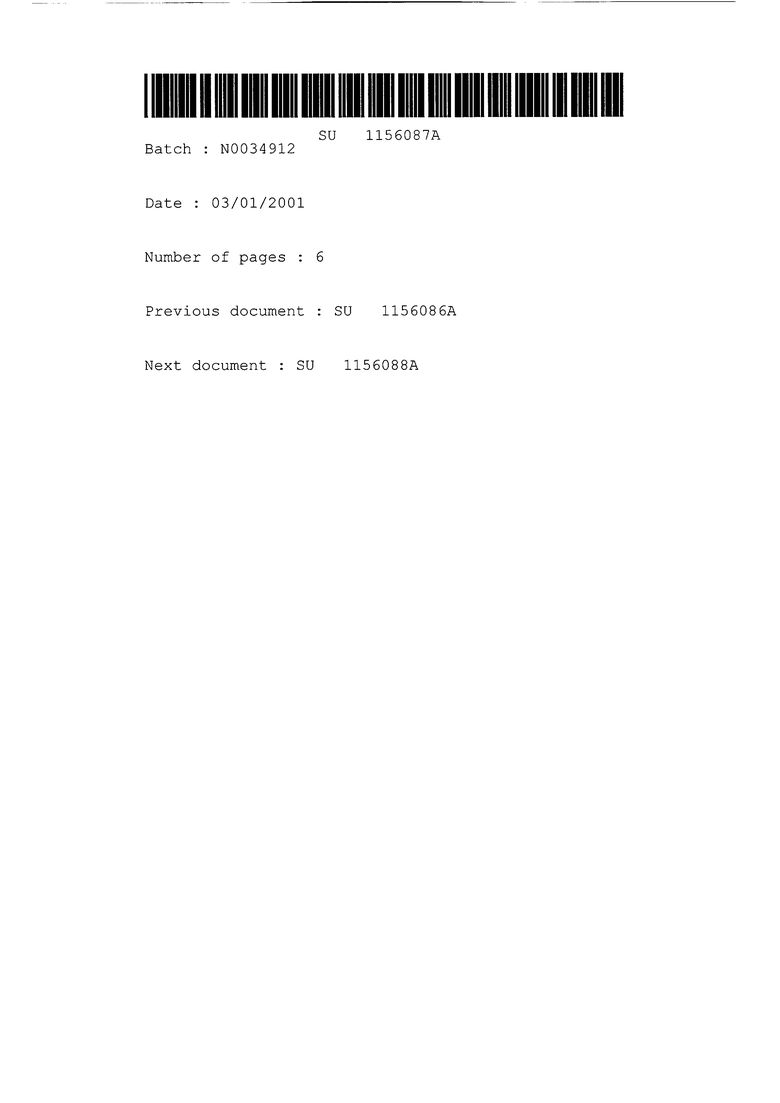

N° ПроцессораРедактор Л. Алексеенко Техред Т.Фанта Корректор М. Демчик

Заказ 3148/47 Тираж 710Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г, Ужгород, ул. Проектная, 4

Составитель Г. Виталиев

Date : 03/01/2001

Number of pages : 6

Previous document : SU 1156086A

Next document : SU 1156088A

союз СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

SU,,.. 1156087 А

(19)

4(51) G 06 F 15/16

ГОСУДАРСТВЕНКЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

(21)3466791/24-24

(22)07.07.82

(46) 15.05.85. Бюл. № 18

(72) И.Я. Денищенко,, Е.М. Ерзаков

и В.И, Головин

(53) 681.32(088.8)

(56) Малые ЭВМ и их применение.

М., Статистика, 1980, с. 77-95.

Патент США № 3.921.149, кл. G 06 F 15/16, опублик. 1975.

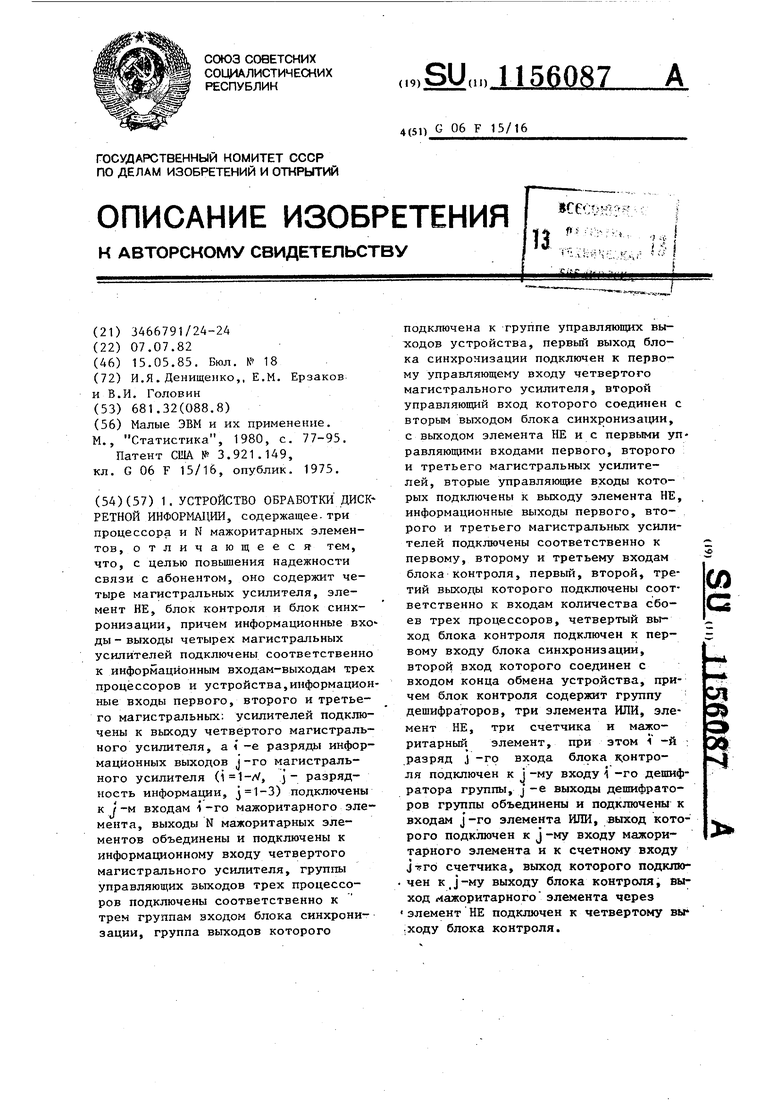

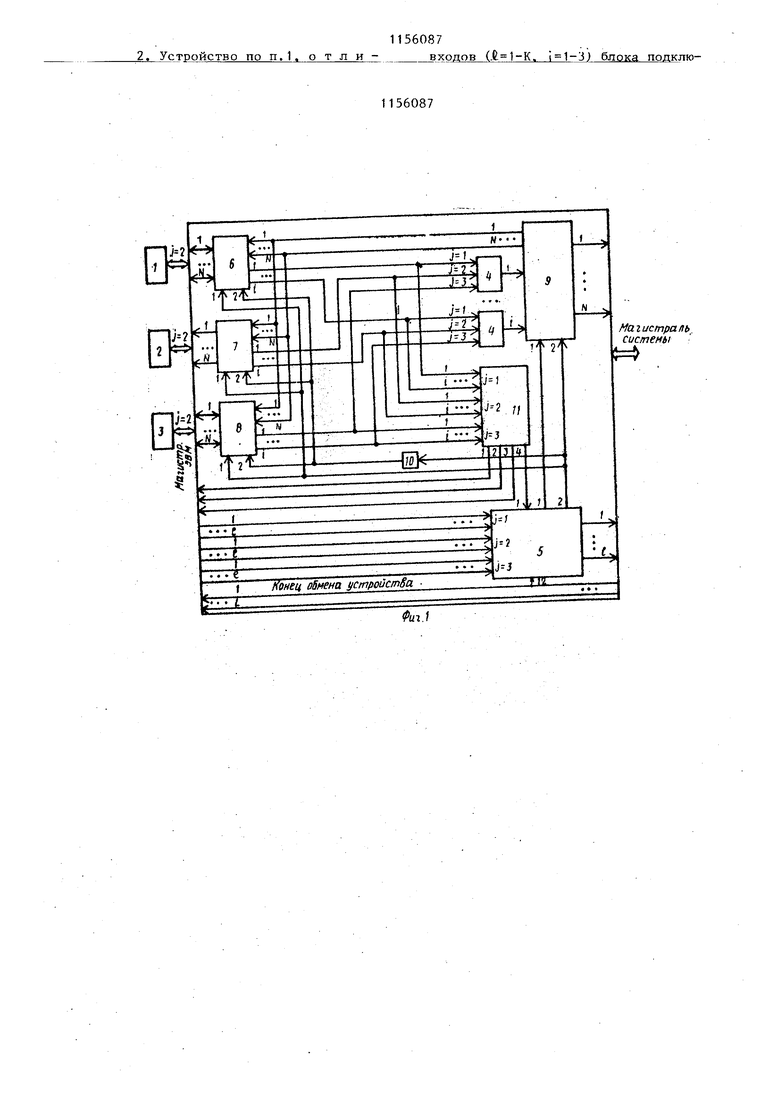

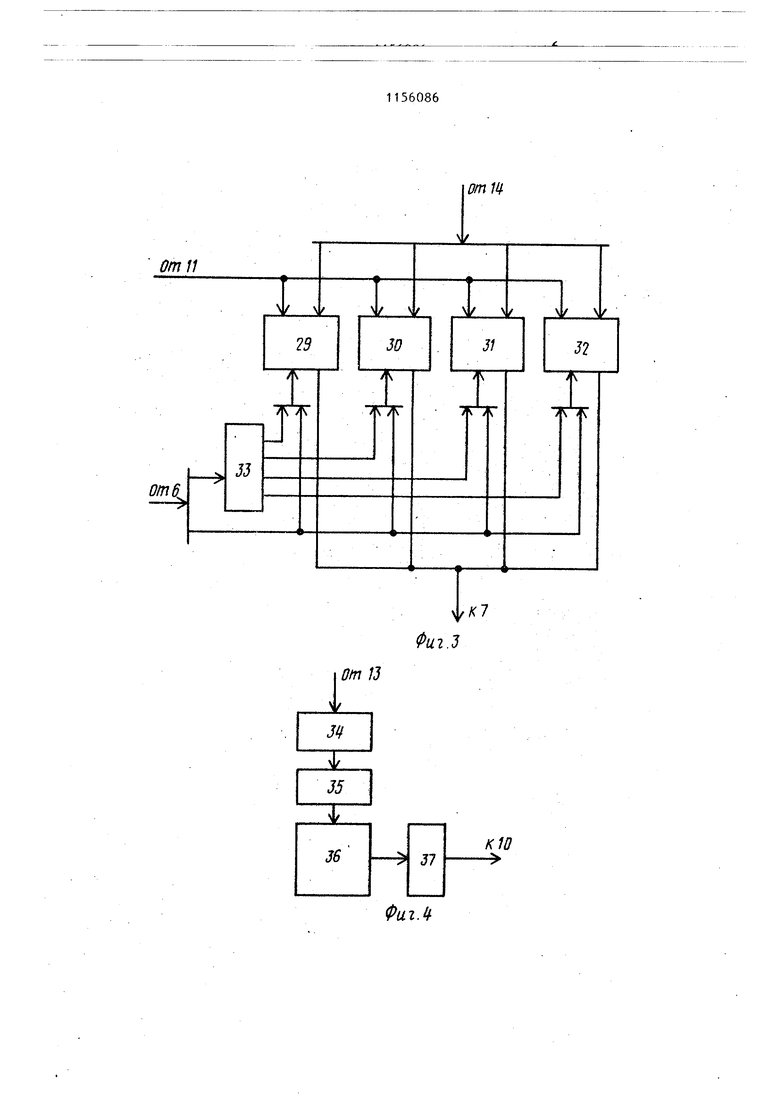

(54)(57) 1. УСТРОЙСТВО ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, содержащее.три процессора и N мажоритарных элементов, отличающееся тем, что, с целью повышения надежности связи с абонентом, оно содержит четыре магистральных усилителя, элемент НЕ, блок контроля и блок синхронизации, причем информационные вхо ды - выходы четырех магистральных усилителей подключены соответственно к информационным входам-выходам трех процессоров и устройства,информационные входы первого, второго и третьего магистральных: усилителей подключены к выходу четвертого магистрального усилителя, а i -е разряды информационных выходов J-го магистрального усилителя (, j- разрядность информации, ) подключены к j-м входам i-го мажоритарного элемента, выходы N мажоритарных элементов объединены и подключены к информационному входу четвертого магистрального усилителя, группы управляющих выходов трех процессоров подключены соответственно к трем группам входом блока синхронизации, группа выходов которого

подключена к группе управляющих выходов устройства, первьш выход блока синхронизации подключен к первому управляющему входу четвертого магистрального усилителя, второй управляющий вход которого соединен с вторым выходом блока синхронизатщи, с выходом элемента НЕ и с первыми управляющими входами первого, второго и третьего магистральных усилителей, вторые управляющие входы которых подключены к выходу элемента НЕ, информационные выходы первого, второго и третьего магистральных усилителей подключены соответственно к первому, второму и третьему входам блока контроля, первый, второй, тре(Л тий выходы которого подключены соотсветственно к входам количества сбоев трех процессоров, четвертый выход блока контроля подключен к первому входу блока синхронизации, второй вход которого соединен с входом конца обмена устройства, причем блок контроля содержит группу

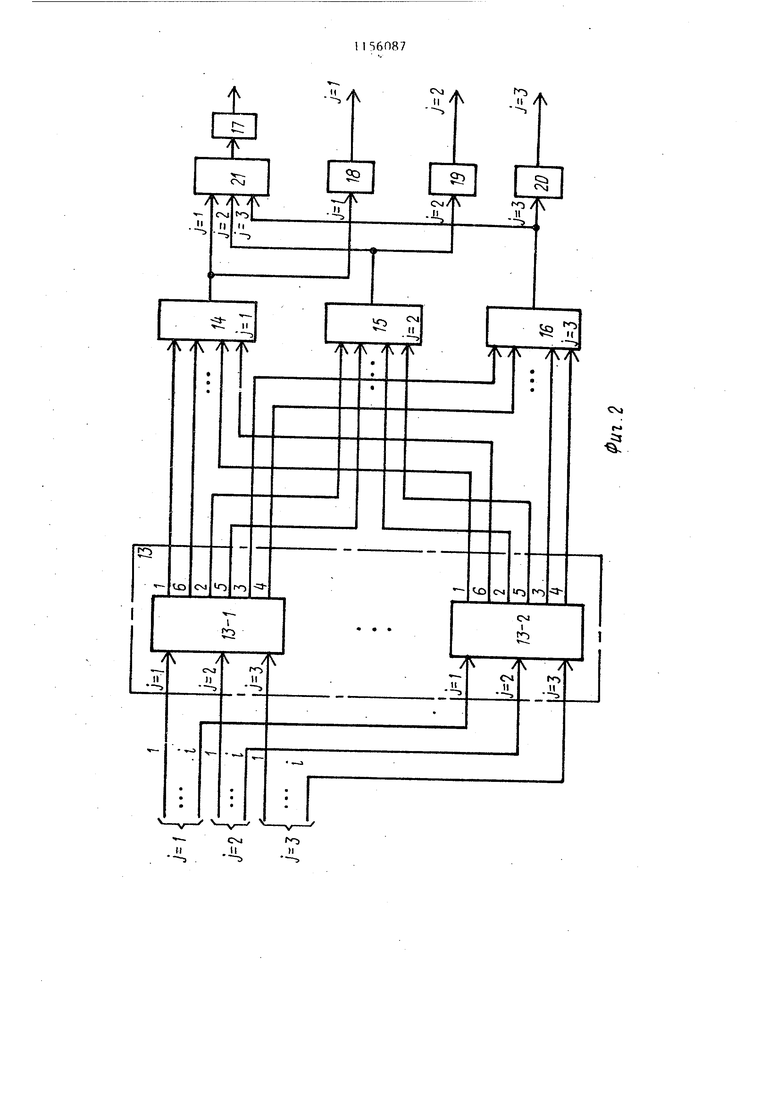

дешифраторов, три элемента ИЛИ, элемент НЕ, три счетчика и мажоритарный элемент, при этом i -и :

ч разряд J -го входа блока контроля подключен к j-му входу -го дешифратора группы, J-е выходы дешифраторов группы объединены и подключены к входам j-ro элемента ИЛИ, выход которого подключен к j-му входу мажоритарного элемента и к счетному входу счетчика, выход которого подключей к j-му выходу блока контроля, выход мажоритарного элемента через

элемент НЕ подключен к четвертому вы ходу блока контроля.

1156087

| Патент США № 4073005, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Патент Великобритании № 1466488, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Устройство для обработки данных | 1979 |

|

SU849222A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1982-05-28—Подача