(54) ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1985 |

|

SU1252770A1 |

| Арифметико-логический модуль | 1983 |

|

SU1160395A1 |

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Многофункциональный логический модуль | 1980 |

|

SU930678A2 |

| Устройство для арифметической илОгичЕСКОй ОбРАбОТКи дВОичНыХчиСЕл | 1979 |

|

SU842795A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Многофункциональный элемент для логической матрицы | 1982 |

|

SU1037344A1 |

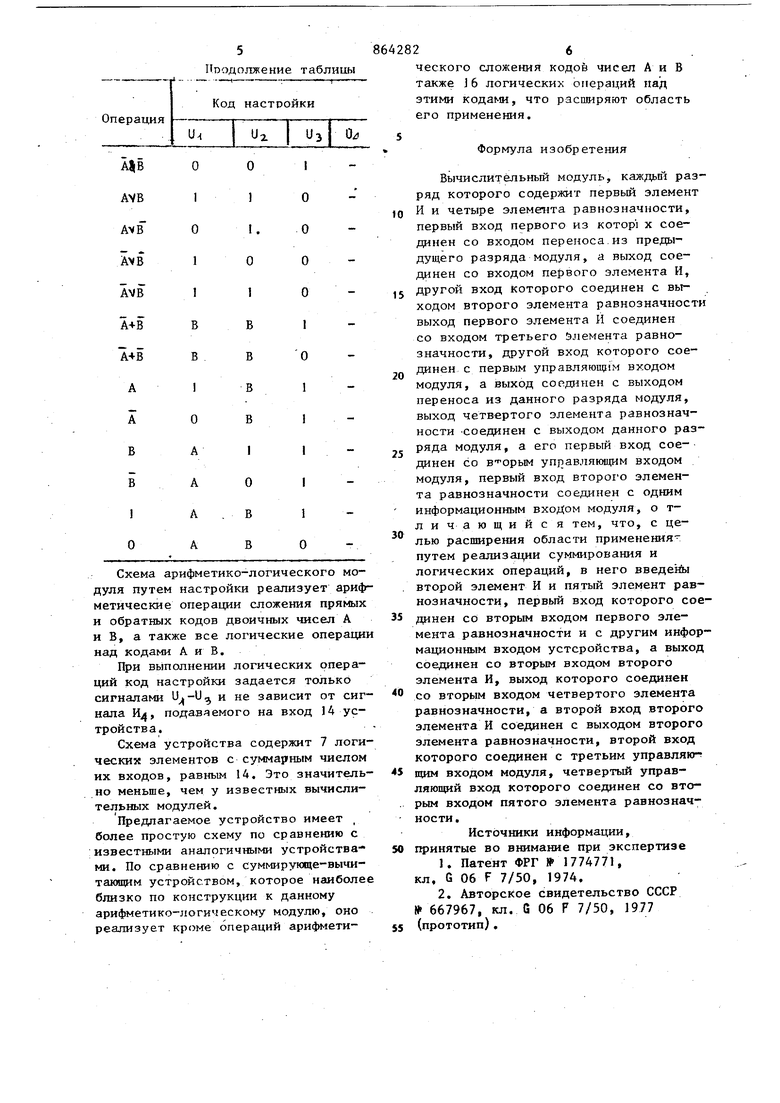

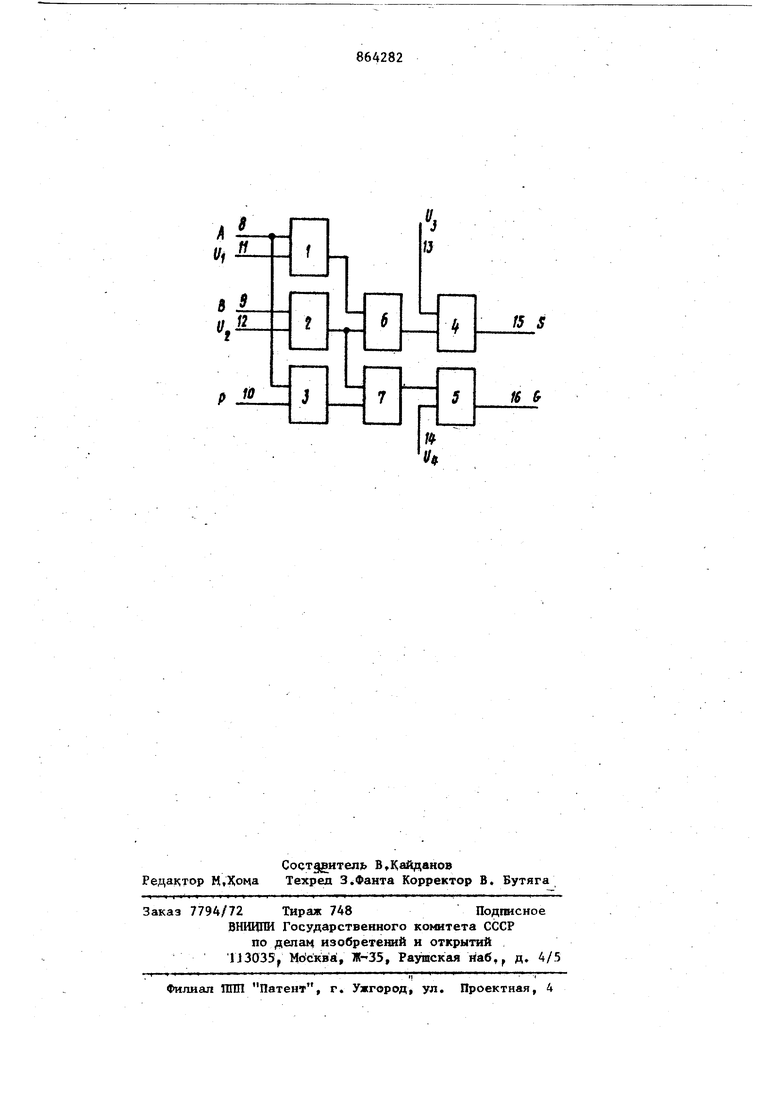

Изобретение относится к вычислительной технике и может использовать ся при построении различмлх цифровых устройств арифметической и логическо обработки двсичных кодов. Известен арифметический модуль, который содержи два информационных входа, вход переноса, 5 управляющих входов, выход результата и 12 логиче ких злементов И-НЕ. Устройство реали зует путем настройки операцию арифме тического сложения и логические опер ции под кодами двух двоичных чисел р Недостатком этого устройства является его сложность. Кроме того в устройстве не вырабатывается выходной снгнад переноса, что ограничивает область его применения. Наиболее близким по технической сущности к предлагаемому яаляется полное суммирующе-вычислительное устройство, выбранное в качестве прототипа, содержащее элемент И и четыре элемента равнозначности, первый вход первого из которых является входом переноса устройства, а второй- управляющим входом устройства, а его выход соединен со входом элемента И, другой вход которого соединен с выходом второго элемента равнозначное ти, а выход - со входом третьего элемента равнозначности, другой вход которого - управляювснй, а выход является выходом результата устройства, выход четвертого элемента равнозначности является выходом переноса устройства, его первый вход - управляю ций, а второй вход с.оединен с выходом второго элемента равнозначности, входы которого являются первым и вторым информационш 1ми входами устрЫ - ства fz. Однако это устройство не реализует логических операций над кодами двоич . ных чисел, что явлется недостатком, ограничивающем его применение в обласг ти вычислительной техники. Цель изобретения - расширение области применения путем реализации суммирования и логических операций. Поставленная цель достигается тем что вычислительный модуль, каждай разряд которого содержит первый элемент И и четыре элемента равнозначноста, первый вход первого из которых соединен со входом переноса из предыдущего разряда модуля, а выход соединен со входом первого элемента И, другой вход которого соединен с выходом второго элемента равнознач ноет, выход первого элемента И соединен со входом третьего элемента равнозначности, другой вход которого соединен с.первым управляющим входом модуля, а выход соединен с вы ходом переноса из данного разряда модуля, выход четвертого элемента равнозначности соединен с данного разряда модуля, а его первый вход соединен со вторым управлякнцим входом модуля, первый вход второго элемента равнозначности соединен с одним информационным входом модуля, в него введены второй элемен И и пятый элемент равнозначности, первый вход которого соединен со вторым входом первого элемента равнозначности и с другим информационны входом устройства, а выход соединен со вторым входом второго элемента И, выход которого соединен со вторым входом четвертого элемента равнознач ности, а второй вход второго элемента И соединен с выходом второго элемента равнозначности, второй вход которого соединен с третьим управляющим входом модуля, четвертый управляющий вход которого соединен со вто рым входом пятого элемента равнознач ности. Такой вычислительный модуль наряд с операцией арифметического- сложения реализует 16 логических операций над кодами двоичных чисел. На чертеже представлена схема устройства. Устройство содержит логические эл менты равнозначности 1-5, элементы И 6, 7, информационные вкЬды 8 и 9, вход переноса 10, управляюпще входы 11--14, выход результата 15 и выход переноса 16. Первый вход элемента равиозначности 1 соединен с управляюпщм входом 11 модуля, а его второй вход - с информационным входом 8, а выход пятого элемента равнознач 4 ости ) соединен со входом элемента 6, второй вход которого соединен с выходом элемента равнозначности 2, первый вход которого соединен с управяющим входом 12 устройства, а второй - с информационным входом 8 устройства. Выход элемента равнозначности 2 соединен со входом элемента И 7, другой вход которого соединен со входом элемента равнозначности 3, первый вход которого соединен с информационным входом 8 устройства, а второй вход - со входом переноса 10 модуля. Выходы элементов И 6 и 7 соединены с первыми входами элементов равнозначности 4 и 5 соответственно, вторые входы которых соединены с управляющими входами 13 и 14 устрой ства соответственно. Выход элемента равнозначности 4 является выходом результата 15, а выход элемента равнозначности 5 - выходом переноса 16 устройства. Устройство работает следующим образом. На информационные входы 8 и 9 подаются двоичные информационные сигналы А и В, на вход 10 - сигнап переноса Р, С выхода 15 устройства снимается сигнал S результата опера.1ЩИ, а с выхода 16 - сигнал G переноса в старший разряд. Сигналы настройки и. -U подаются на управляющие входы 11-14 устройства соответственно. Код настройки (сигналы U. iU.) определяет арифметическую или логическую операцию, реализуемую ус|тройством. Коды настроек и соответствую1цие им реализуемые устройством операции представлеиы в таблице.

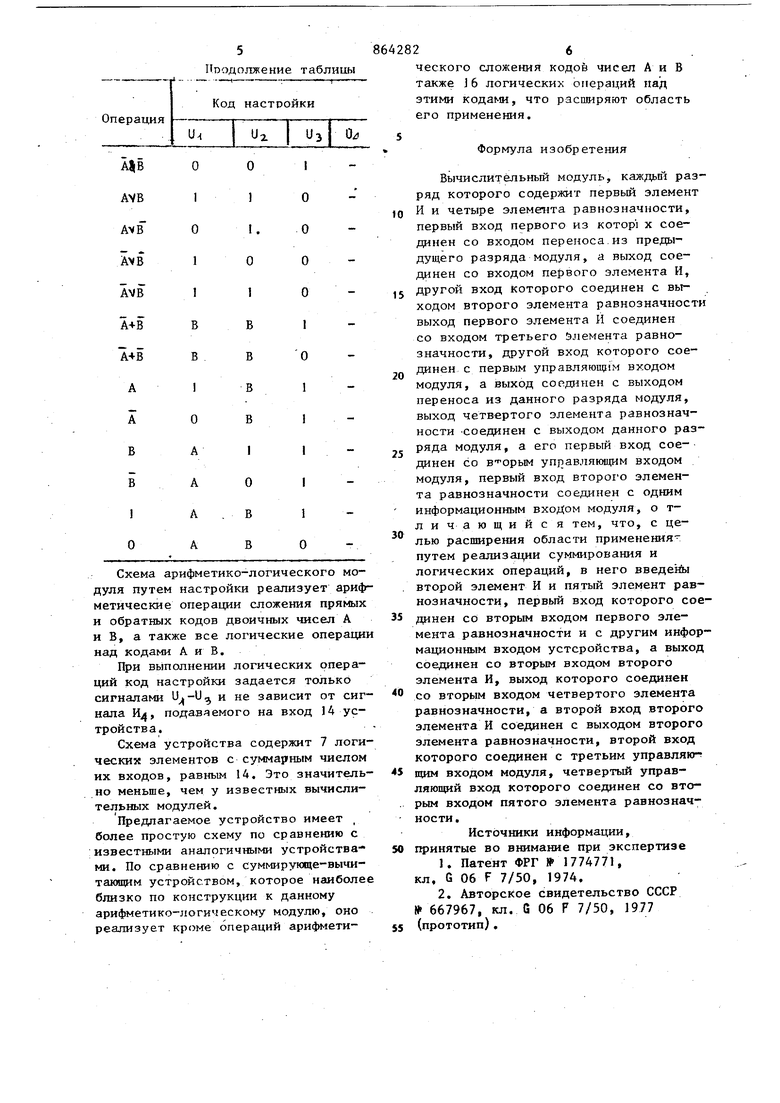

Пподолжение таблицы

Схема арифметико-логического модуля путем настройки реализует арифметические операции сложения прямых и обратных кодов двоичных чисел А и В, а также все логические операции над кодами А и В.

При выполнении логических операций код настройки задается только сигналами и не зависит от сигнала Ил, подаваемого на вход 14 устройства.

Схема устройства содержит 7 логических элементов с суммарным числом их входов, равным 14. Это значительно меньше, чем у известных вычислительных модулей.

предлагаемое устройство имеет , более простую схему по сравнению с известными аналогичными устройствами. По сравнению с суммиругеще-вычитаиицим устройством, которое наиболее близко по конструкции к данному арифметико-логическому модулю, оно реализует кроме операций арифметического сложения кодов чисел А и В также J6 логических операций над этими кодами, что расширяют область его применения.

Формула изобретения

Вычислительный модуль, каждьй разряд которого содержит первый элемент И и четыре элемента равнозначности, первый вход первого из KOTopi х соединен со входом переноса.из предыдущего разряда модуля, а выход соединен со входом первого элемента И, ДРУГОР вход которого соединен с выходом второго элемента равнозначност выход первого элемента И соединен со входом третьего Злеманта равнозначности, другой вход которого соединен с первым управляю1Щ1м входом модуля, а выход соединен с выходом переноса из данного разряда модуля, выход четвертого элемента равнозначности Соединен с выходом данного разряда модуля, а его первый вход соединен со уп11авляю1цим входом модуля, первый вход второхо элемента равнозначности соединен с одним информационным входом модуля, о тли чающийся тем, что, с целью расширения области примененияпутем реализации суммирования и логических операций, в него введешл второй элемент И и пятый элемент равнозначности, первый вход которого соединен со вторым входом первого элемента равнозначности и с другим информационным входом устсройства, а выход соединен со вторым входом второго элемента И, выход которого соединен со вторым входом четвертого элемента равнозначности, а второй вход второго элемента И соединен с выходом второго элемента равнозначности, второй вход которого соединен с третьим управлякп

щим входом модуля, четвертый управляющий вход которого соединен со вто. рым входом пятого элемента равнозначности.

Источники информации,

0 принятые во внимание при экспертизе

5 (прототип).

Авторы

Даты

1981-09-15—Публикация

1980-01-07—Подача