нен с емого информационным входом управдя- к выходу генератора тактовых импульделителя частоты н подк;ж)чен сои. ПЬОДЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Корреляционный измеритель временизАпАздыВАНия | 1979 |

|

SU824219A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Корреляционное устройство для определения задержки | 1982 |

|

SU1051545A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1515174A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

1. КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕНИ ЗАПАЗДЫВАНИЯ, содержащий Ъумматор, первьй и второй регистры, выход первого из которых является выходом устройства, компаратор, первый вход которого является первым информационным входом устройства, второй вход компаратора подключён к шине нулево- го потенциала, первый счетчик, выход переноса которого соединен со счетным входом второго счетчика, от ли чающийся тем, что, с целью повышения быстродействия, в него введены блок памяти, блок постоянной памяти, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент задеряоси и умножитель частоты, вход которого является вторьм информационным входом устройства, выход умножителя частоты соеданен со счетным входом первого счетчика, информационные вьйсоды которого соответственно соединены с первой группой адресных входов блока постоянной памяти, с адресными входами блока памяти и информационными входами первого регистра, тактовый вход которого подключен к выходу переноса сумматора, выходы которого соответственно соедине.ны с информационными входами блока памяти, первая группа входов сумматора подключена к шине нулевого потенциала, вторая группа входов сумматора соответственно подключена к выходам второго регистра, вход переноса сумматора подключен к выходу элемента ИСКПЮЧАЩЕЕ ИЛИ, первый и второй входы которого подключены соответственно к выходам компаратора и блока постоянной памяти, вторая группа адресных входов которого подключена к информационным выходам второго счетчика, выход умножителя частоты через элемент задержки соединен с входом управления записью блока памяти и тактовым входом второго регистра, информационные входы которого соответственно подключены I к выходам блока памяти. 2. Измеритель по п.1, от ли чающийся тем что умножитель частоты содержит генератор тактовых 9: импульсов, делитель частоты, счето чик, регистр и управляемый делитель 4 частоты , выход переноса которого :о является выходом умножителя частоты, управляющие входы управляемого делителя частоты соответственно подключены к информационным выходам регистра, информационные входы которого соответственно подключены к инфориационным выходам сче;тчика, вход сброса которого объединен с TaKTOBtdM входом регистра и является входсш умножителя частоты, счетный вход i счетчика подключен к выходу делителя частоты, вход которого объедаг

Изобретение относится к устройствам для определения времени запаздывания по положению максимума взаимн корреляционной функции и может ИСПОЗОВАТЬСЯ в системах автоматического управления и измерительной аппаратуре .

Известен корреляционный измеритель времени запаздывания, содержащий блок регистровой памяти, входы и выходы которого соединены с входами и выходами ключей, три блока пермножителей, первые входы которых содинены с тремя последними выходами блока регистров, а выходы блоков перемножителей соединены с входами блоков интегрирования, выходы которых соединены с входами блока элементов И, выходы которого соединены с первьми входами цифровых компараторов, выходы которых соединены с входами элементов И, выходы Которых соединены с первыми входами триггеров, выходы которых через вспомогательные элементы И соединены с входами первого и второго счетчиков, вторые входы вспомогательных элементов И соединены е выходами соответственно первого и второго элементов ИЛИ, входы которых соединены с выходами линий задержки, входы которых соединены с выходом генератора, а дополнительные выходы с входом третьего элемента ИЛИ, выход которого соединен с управляющим входом блока элементов И, а вход блока регистров и вторые входы блоков перемножителей соединены соответственно с первым и вторьтм входами устройства Г

Недостатками этого устройства являются ограниченность функциональных возможностей, поскольку для его использования требуется сходный характер сигналов (исследуемый объект не должен приводить к линейному преобразованию сигналов), сложность аппаратурной реа;шзации, постоянное время отклика, что не

удобно, поскольку для сильно взаимосвязанных процессов это время может быть сокращено, а для слабосвязанных должно автоматически увеличиваться. Кроме того, это устройство имеет относительно узкий динамический диапазон входных сиг-. налов.

Наиболее близким по технической сущности к предлагаемому является корреляционный измеритель времени запаздывания, содержащий Компаратор, первый и второй регистры, сумматор, первьй и второй счетчики,выход переноса первого счётчика соединен со счетным входом второго счётчика, информационный вход компаратора соединен с первым входом корреляционного измерителя времени запаздывания, выходы которого соединены с

выходами первого регистра 2,

I -,

Недостатками известного корреляционного измерителя времени запаздывания являются относительно низкое быстродействие, что связано с одной стороны, с необходимостью выполнения большого количества операций за один цикл измерения, сложностью этих операций, а с другой - с тем, что время оценки не зависит от взаимной связи характеристик процессов. В действительности для сильносвязанных процессов это время моАет быть выбрано относительно MamiM, а для слабосвязанных процессов, например содержащих значительную аддитивную случайную составляющую в виде шума, время измерения должно быть увеличено. Кроме того, известное устройство имеет ограниченные функциональные возможности, поскольку не может изменять свои характеристики в зависимости от вида сигнала. Наконец это устройство имеет относительно узкий допустимый диапазон входных сигналов

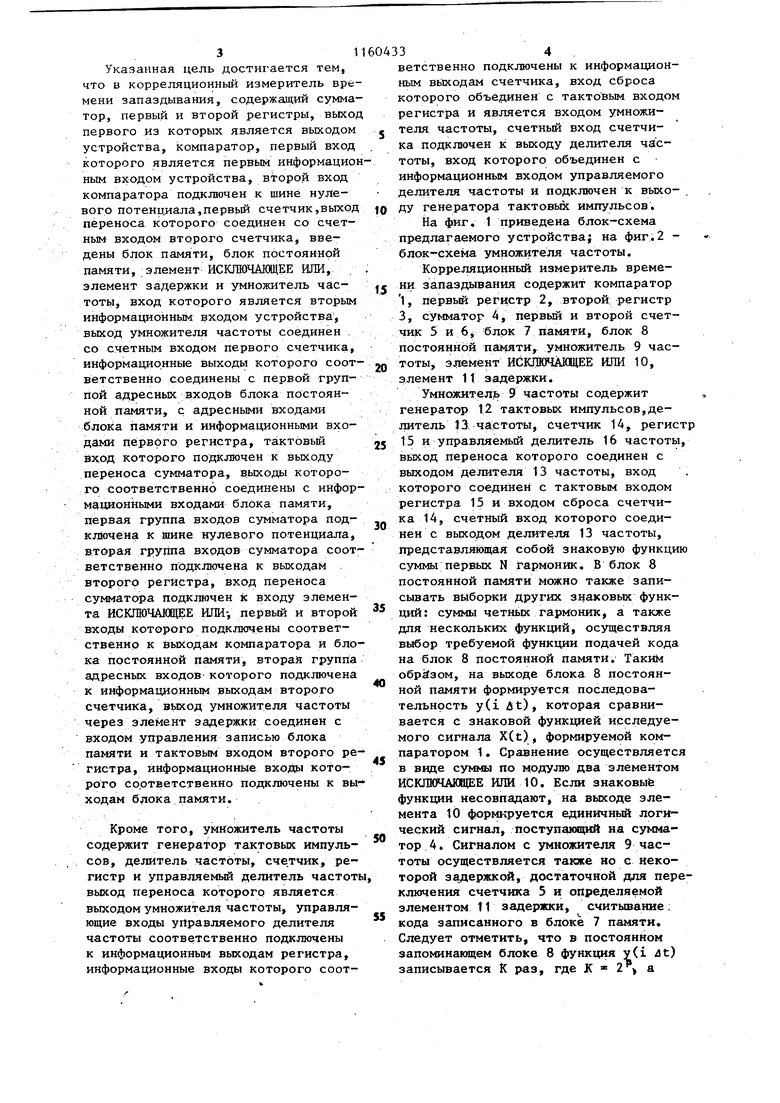

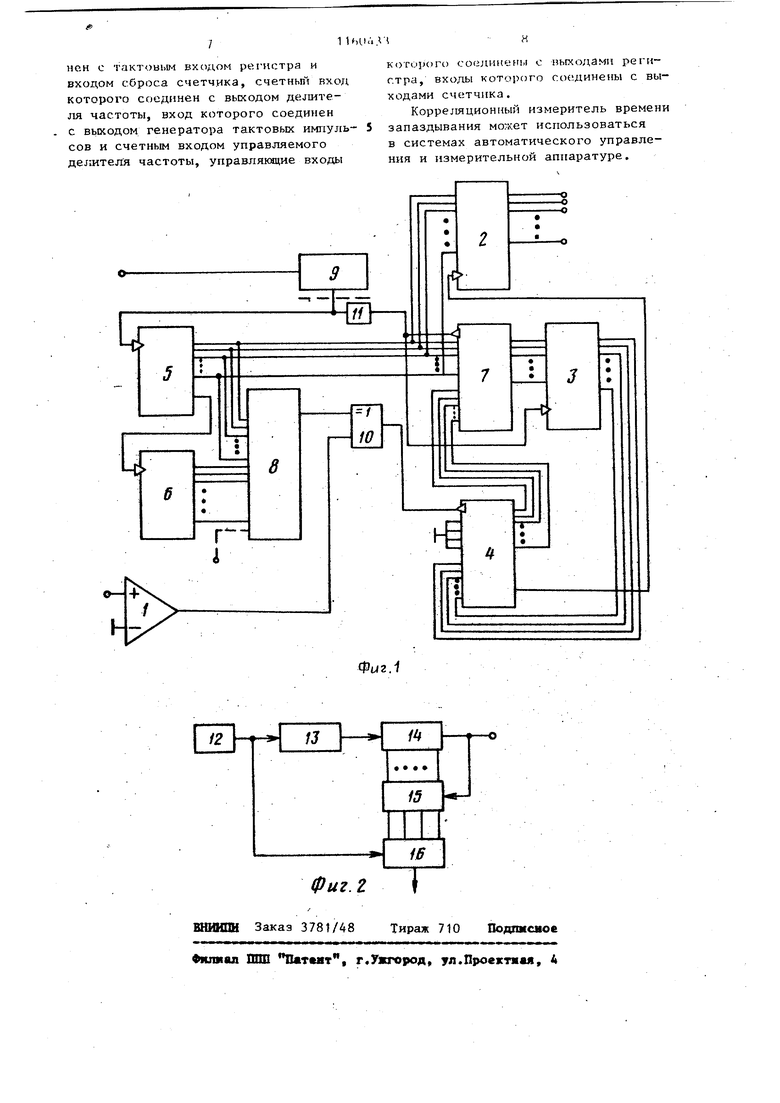

Целью изобретения является повышение быстродействия при одновременном сокращении аппаратурных затрат. Указанная цель достигается тем, что в корреляционный измеритель вре мени запаздывания, содержащий сумма тор, первый и второй регистры, выхо первого из которых является выходом устройства, компаратор, первый вход которого является первьм информацио ным входом устройства, второй вход компаратора подключен к шине нулевого потенциала,первый счетчик,выход переноса: которого соединен со счетным входом второго счетчика, введены блок памяти, блок постоянной памяти, элемент ИСКПЮЧАВДЕЕ ИЛИ, . элемент задержки и умножитель частоты, вход которого является вторым информационным входом устройства, выход умножителя частоты соединен . со счетным входом первого счетчика, информационные выходы которого соот ветственно соединены с первой группой адресных входой блока постоян ной памяти, с адресными входами блока памяти и информационными входами первого регистра, тактовьй вход которого подключен к выходу переноса сумматора, выходы которого соответственно соединены с инфор мационными входами блхэка памяти, первая группа входов сумматора подключена к шине нулевого потенциала, вторая группа входов сумматора соот ветственно подключена к выходам . второго регистра, вход переноса сумматора подключен к входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-, первый и второй входы которого подключены соответственно к выходам компаратора и бло ка постоянной памяти, вторай группа адресньк входов- которого подключена к информационным выходам второго счетчика, вькод умножителя частоты через элейент задержки соединен с входом управления записью блока памяти и тактовым входом второго ре гистра, информационные входы которого соответственно подключены к вы ходам блока памяти. Кроме того, умножитель частоты содержит генератор тактовых импульсов, делитель частоты, счетчик, регистр и управляемый делитель частот выход переноса которого является выходом умножителя частоты, управляющие входы управляемого делителя частоты соответственно подключены к информационным выходам регистра, информационные входы которого соответственно подключены к информационным выходам счетчика, вход сброса которого объединен с тактовым входом регистра и является входом умножителя частоты, счетный вход счетчика подключен к выходу делителя частоты, вход которого объединен с информационным входом управляемого делителя частоты и подключен к выходу генератора тактовых импульсов. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2 блок-схема умножителя частоты. Корреляционный измеритель времени запаздывания содержит компаратор 1, первый регистр 2, второй регистр 3, сумматор 4, первый и второй счетчик 5 и 6j блок 7 памяти, блок 8 постоянной памяти, умножитель 9 частоты, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элемент 1 задержки. Умножитель 9 частоты содержит генератор 12 тактовьк импульсов,делитель J3. частоты. Счетчик 14, регистр 15 и управляемый делитель 16 частоты, выход переноса которого соединен с выходом делителя 13 частоты, вход которого соединен с тактовым входом регистра 15 и входом сброса счетчика 14, счетный вход которого соединен с выходом делителя 13 частоты, представляющая собой знаковую функцию суммы первых N гармоник. В блок 8 постоянной памяти можно также записывать выборки других знаковых функций: суммы четньк гармоник, а также для нескольких функций, осуществляя выбор требуемой функции подачей кода на блок 8 постоянной памяти. обрйзом, на вьпсоде блока 8 постоянной памяти формируется последовательность y(i At), которая сравнивается с знаковой функцией исследуемого сигнала X(t),, формируемой компаратором 1, Сравнение осуществляется в виде суммы по модулю два элементом ИСКЛЮЧАЮЩЕЕ ИШ 10. Если знаковые функции несовпадают, на выходе элемента 10 формируется единичнь1й логический сигнал, поступаюпщй на сумматор 4. Сн налом с умножителя 9 частоты осуществляется также но с некоторой задержкой, достаточной для переключения счетчика 5 и определяемой элементом t1 задержки, считывание: кода записанного в блоке 7 памяти. Следует отметить, что в постоянном запоминакщем блоке 8 функция у(1 /)t) записывается К раз, где К 2 а 5 р - разрядность счетчика 5, причем каждый раз со сдвигом во времени. Таким образом, при считывании из блока 8 постоянной памяти для каждого значения входного сигнала X(t) функция y(i dt) выбирается К раз с изменяющейся временной задержкой, каждый раз сравниваясь на элементе 11. Результат сравнени прибавляется к коду, зафиксированному в блоке 7 памяти,Таким обра зом, если знаковые функции сигнало X(t) и yCi йt-j)(гдe j 1, ..., К) совпадают по соответствующему адре су, в блоке 7 памяти накапливается код. Когда величина этого кода дос тигнет заданной величины, прибавле ние следующей едании) вход которог соединен с выходом генератора 12 т товых импульсов и информационным входом управляемого делителя 16 ча аготы, управляющие входы которого соединены с информационными выходами регистра 15, входы которого соединены с выходами счетчика 4, Корреляционный измеритель времени запаздывания работает следутощим образом, Исследуемьш сигнал подается на первьщ информационш вход, а опорный временной импульс - на второй информационньй вход. Входной сигнал X(t) преобразуется компараТором 1 в его знаковую функцию sign X(t). Импульсный опорньй сигнал со второго информационного вхо поступает на вход умножителя 9 час тоты, на выходе которого формирует ся последовательность импульсов с частотой в М раз, превьшающей част ту опорного сигнала, причем фаза выходного сигнала привязана к фазе опорного сигнала. Импульсы с умножителя 9 частоты поступают, на вход счетчика 5, импульсами с выхода переноса которого перекш)чается счетчик 6. Коды с выходов счетчиков 5 и 6 задают адрес сигнала, записанного в блоке 8 постоянной памяти. В простейшем случае там могут быть записаны выборки знаковой функции синусного сигнала y(i At) - sign (sin/()3 . Если исследуемый объект нелинейнкй в сигнале U),(t) могут присутствовать кратные гармонические составляющие, как четные, так и нечетные. ,В этом случае, для обеспечения 3 учета четных гармоник в блоке 8 постоянной памяти могут быть записаны выборки функции iNiwM iWAt V Uilcsi f Fs il-г wiA-tjS fi- -Cftses--I к нему вызовет появление единичного сигнала на выходе переноса сумматора 4, что вызовет запись соответствующего ему кода адреса, определяющего временную задержку сигнала в регистр 2. Регистр 3 служит для промежуточного хранения ранее накопленного кода, подаваемого на сумматор 4. Естественно, что умножитель 9 частоты должен обеспечивать коэффициент умножения М L-K, где L число выборок функции у(i 4t) за период сигнала, поданного на вход 14, т.е. i 1 - L. Величина М определяется коэффициентом деления делителя 13 частоты. Поскольку предложенное устройств© обеспечивает контроль за полржением максимума в темпе поступления входных данных, а в качестве взаимно корралящонной используется функция взаимной :знаковой корреляции, обеспечивается сравнительное высокое быстродействие, так как не требуется выполнять такие сложные операции, как умножение. Это обеспечивает и относительно широкий динамический диапазон входных сигналов, определяется компаратором 1. Благодаря возможности выбора кнформащ1И, записанной в постоянном запоминающем блоке 8, обеспечивается ошрокий выбор опорньсс функций, что позволяет исследовать задержки распространения в самых различных системах: линейных, нелинейньлс, инвертирующих, для заданной гармоНической составляющей и т.д. Поскольку накопление информации в оперативном запоминающем устройстве происходит в зависимости от взаиг мосвязи сигналов быстро для сильнокоррелиррёанных сигналов и медленно для слабокоррелированных, автоматически обеспечивается .выбор време- ни измерений В исходном состоянии, 8 оперативно эапо)шн8ющем блоке 8 должен быть записан нулевой код, что может быть обеспечено, например, подачей ийпульса с выхода переноса сумма T oga на вход сброса, который соедипен с тактовым входом регистра и входом сброса счетчика, счетньш вход которого соединен с вькодом делителя частоты, вход которого соединен с вькодом генератора тактовых импульсов и счетным входом управляемого делителя частоты, управляющие входы

которого соединены с выходами регистра, входы которого соединены с выходами сч(5тчика.

Корреляционный измеритель времени запаздывания может использоваться в системах автоматического управления и измерительной аппаратуре.

|t

k

8

€

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Березин С.А | |||

| и Каратаев С.Г | |||

| Корреляционные измерительные устройства в автсматике | |||

| Л., Энергия, 1976, Со 67 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Корреляционный измеритель временизАпАздыВАНия | 1979 |

|

SU824219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-29—Подача